Construction method of non-regular permutation matrix LDPC code and its device

A technology of LDPC codes and permutation matrices, applied in the information field, can solve problems such as increasing the complexity of decoder implementation and destroying the block structure of H matrix

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0080] Embodiment 1: Constructing an irregular permutation matrix LDPC code

[0081] The following specifically describes the process of constructing a (1008,504) LDPC system code by using the construction method described in the present invention:

[0082] Step 1, determine the parameters of the H matrix. Given that the code length N=1008 and the number of check equations M=504, the size of the H matrix is 504×1008. Calculate the factors of M and N separately, we can get N=28×36, M=14×36, so we can choose the size of each sub-block to be 36×36, and the whole matrix can be divided into 14×28 sub-blocks ;

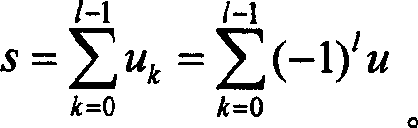

[0083] Step 2, using the density deduction method to determine the dimensional distribution of the H matrix. Determine the dimension distribution function of the variable node as λ(x)=0.2947x+0.2842x 2 +0.4211x 2 , that is, the edges connected by variable nodes with a dimension of 2 account for 29.47% of the total number of edges, the edges connected by variable nodes...

Embodiment 2

[0095] Example 2: Encoder

[0096]The hardware structure of the encoder is shown in Figure 18. The encoder includes information bit input (DUPLICATE), information bit cache RAM, partial checksum RAM (RAM#1_1...), partial checksum update (XOR#1... ), interleaving, node bit buffer RAM, row interleaving index ROM, accumulation interleaver, parity bit buffer RAM, column interleaving index ROM and codeword bit output (MUX) module. Among them, the information bit input (DUPLICATE) copies the input information bits into two parts, which are respectively input into the information bit buffer RAM and part of the checksum update module. The information bit buffer RAM includes three memory RAMs, each of which has a size of 504 bits. The three memory RAMs cyclically store the input information bits, and output them at the end of the encoding, which plays a role in delaying the information bits. The partial checksum RAM includes a 504-bit memory, which is used to save the partial checksum...

Embodiment 3

[0097] Embodiment 3: Decoder

[0098] The overall structure of the decoder is shown in Figure 15, which can be divided into four parts: Controller (control module), Memory (memory), VNU (variable node computing unit) and CNU (check node computing unit).

[0099] Among them, a total of 28 variable node calculation units are required, and a total of 14 check node calculation units are required. The decoding algorithm can use a simplified algorithm of the sum-product algorithm—the minimum sum algorithm. Since there are 94 non-zero permutation matrices in the constructed H matrix, a total of 188 dual-port RAMs with a size of 36×7 bits (here, the quantization width is taken as 7) are required to provide decoding for two codewords at the same time, and they are used as storage units For simultaneous decoding of two codewords, intermediate data is provided to the variable node computing unit and the check node computing unit for calculation.

[0100] As shown in Figure 21, the contr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com