Chemical mechanical polishing technique

A grinding process and chemical-mechanical technology, used in grinding devices, grinding machine tools, other chemical processes, etc., can solve problems such as low dielectric scratches, structural cracks, increased maintenance costs, and increased parts costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

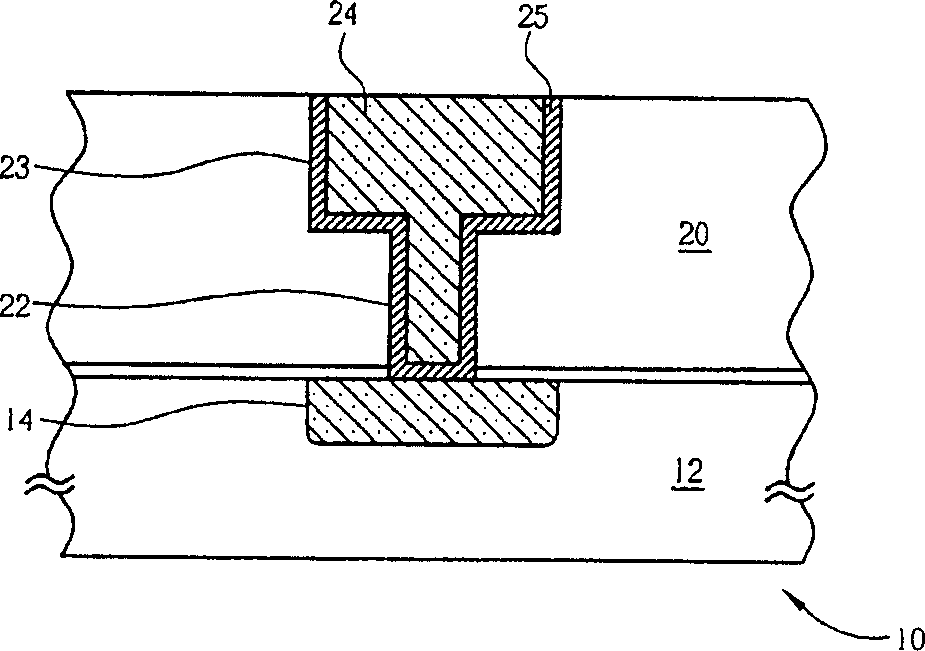

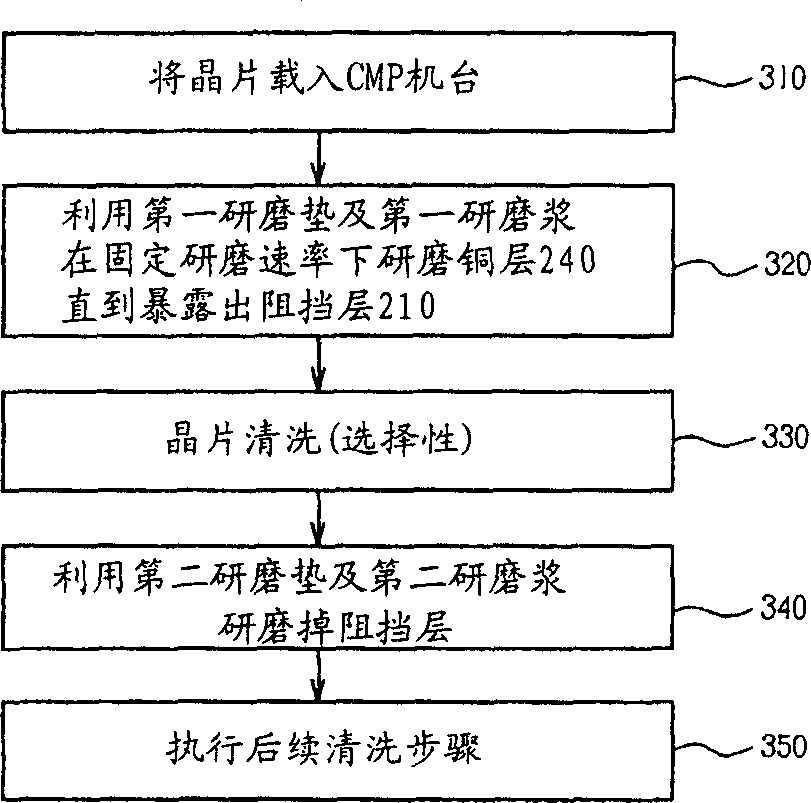

[0028] The invention relates to a method for forming high-reliability integrated circuit metal interconnection, especially aimed at improving the chemical mechanical polishing process applied to copper / barrier layer embedded metal interconnection in the back-end process of integrated circuit. It should be noted that “copper” referred to below generally refers to copper metal or any copper alloy material suitable for the copper damascene process. The main advantages of the present invention are high throughput, especially at the CMP stage, and low cost.

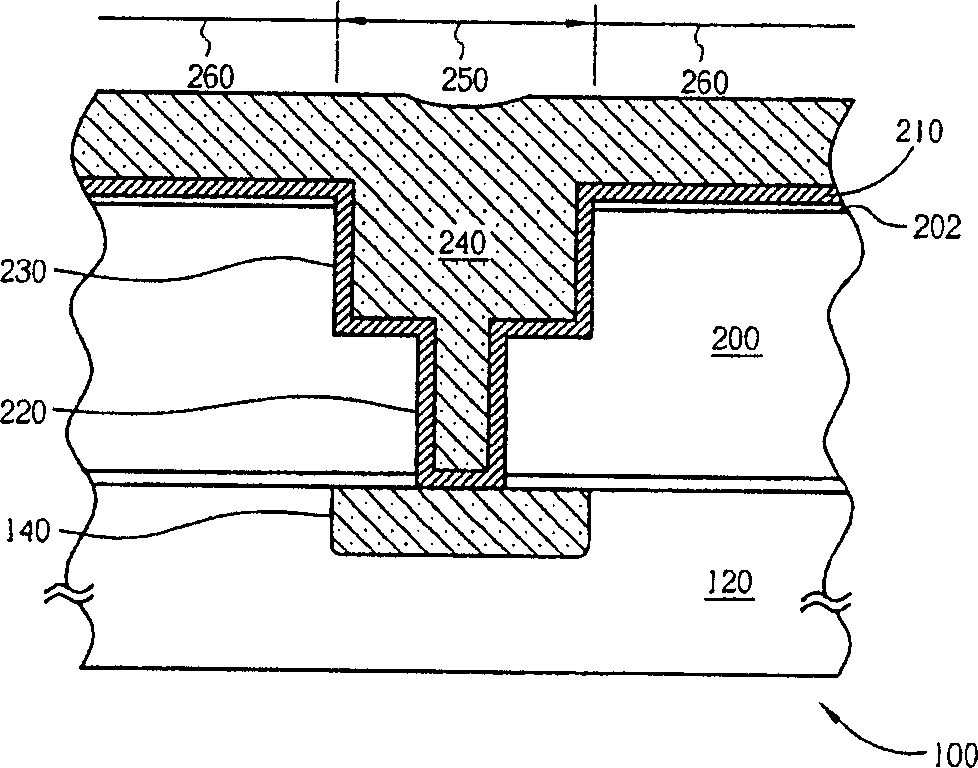

[0029] For clarification, see figure 2 , which shows a schematic cross-sectional view of the semiconductor wafer 100 before performing the CMP process of the present invention, on which the copper metal layer 240 and the barrier layer 210 are formed. Such as figure 2 As shown, the barrier layer 210 is formed on the surface of the damascene recessed region 250 and formed on the uppermost surface region 260 of the dielectric...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com