Lateral double-diffusion field effect transistor, manufacturing method, chip and circuit

A field effect transistor, lateral double diffusion technology, applied in circuits, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as driving capability and speed difference, and achieve increased speed, guaranteed breakdown voltage, and reduced effective mass. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

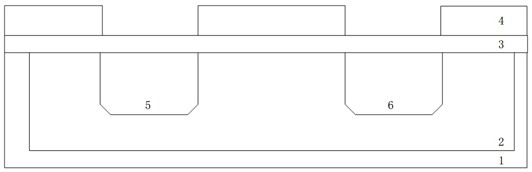

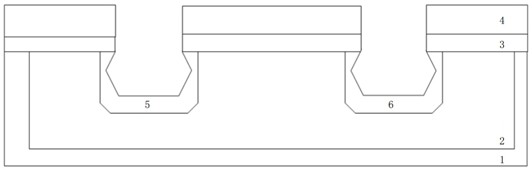

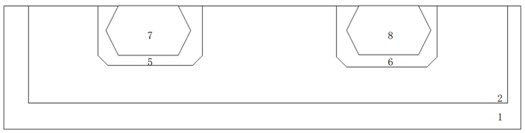

[0031] The specific implementation manners of the embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be understood that the specific implementation manners described here are only used to illustrate and explain the embodiments of the present invention, and are not intended to limit the embodiments of the present invention.

[0032] It should be noted that, in the case of no conflict, the embodiments of the present invention and the features in the embodiments can be combined with each other.

[0033] In the present invention, unless stated to the contrary, the used orientation words such as "up, down, top, bottom" generally refer to the directions shown in the drawings or refer to the vertical, perpendicular or gravitational directions The terms used to describe the mutual positional relationship of the various components mentioned above.

[0034] The present invention will be described in detail bel...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com