Solar cell and preparation method thereof

A solar cell and electrode technology, applied in the field of solar cells, can solve the problems of increasing parasitic light absorption, reducing light utilization efficiency, and low content, and achieve the effects of improving light utilization efficiency, reducing parasitic light absorption, and reducing manufacturing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

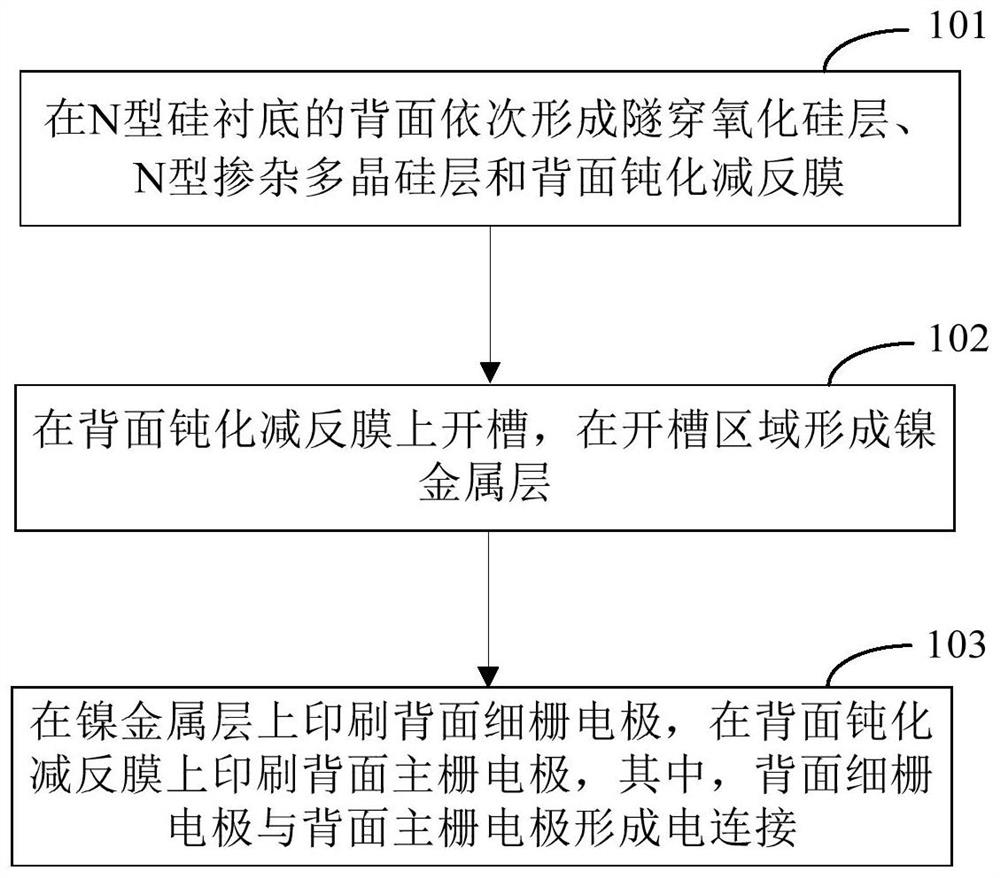

[0045] In order to solve the above problems, an embodiment of the present invention provides a method for manufacturing a solar cell. in, figure 1 A schematic diagram of the main flow of the solar cell fabrication method. Such as figure 1 As shown, the preparation method of the solar cell may include the following steps:

[0046] Step 101, sequentially forming a tunneling silicon oxide layer 2, an N-type doped polysilicon layer 4 and a rear passivation anti-reflection film 5 on the back of the N-type silicon substrate 1;

[0047] Step 102, groove the passivation anti-reflection film 5 on the back surface, and form a nickel metal layer 6 in the grooved area;

[0048] Step 103 , printing the back fine grid electrode 7 a on the nickel metal layer 6 , and printing the rear main grid electrode 7 b on the rear passivation antireflection film 5 , wherein the rear fine grid electrode 7 a is electrically connected to the rear main gate electrode 7 b.

[0049] Wherein, the front sid...

Embodiment 1

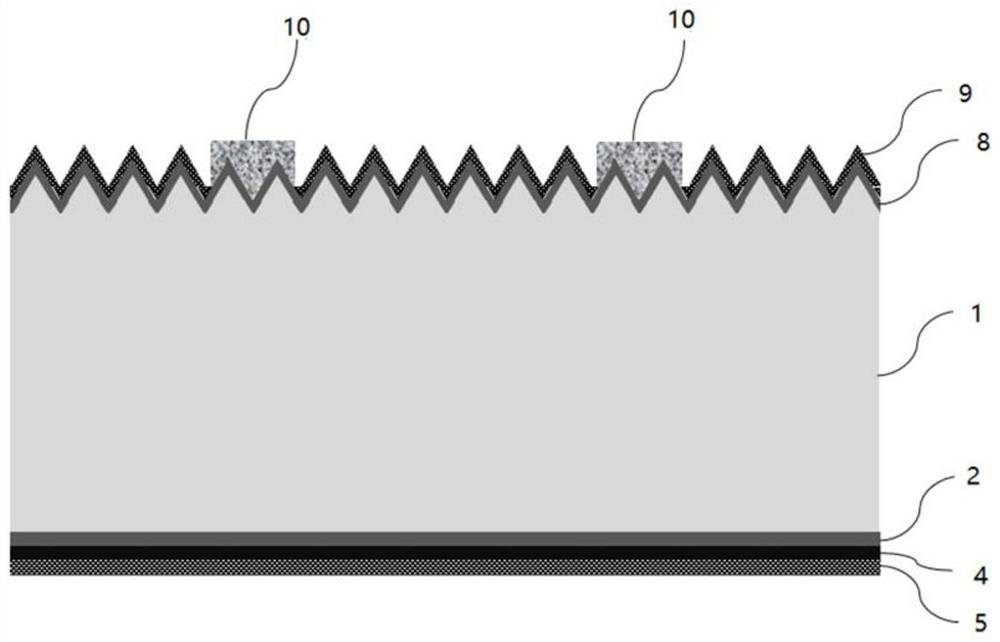

[0093] Step A1: providing an N-type silicon substrate 1 , performing texturing treatment on the front and back sides of the N-type silicon substrate 1 , and performing polishing treatment on the back side of the N-type silicon substrate 1 .

[0094] Step B1: performing boron diffusion treatment on the front side of the N-type silicon substrate 1 to form a P+ emitter 8 .

[0095] Step C1: removing the p-n junction and borosilicate glass on the back of the N-type silicon substrate 1 by using HF acid solution.

[0096] Step D1: Form a tunneling silicon oxide layer 2 with a thickness of 1-2 nm on the back surface of the N-type silicon substrate 1 by high temperature thermal oxidation.

[0097] Step E1: forming an intrinsic polysilicon layer 3 on the tunneling silicon oxide layer 2 on the back side of the N-type silicon substrate 1 by LPCVD / PVD.

[0098] Step F1: doping the intrinsic polysilicon layer 3 on the back side with phosphorus by ion implantation, and performing annealing...

Embodiment 2

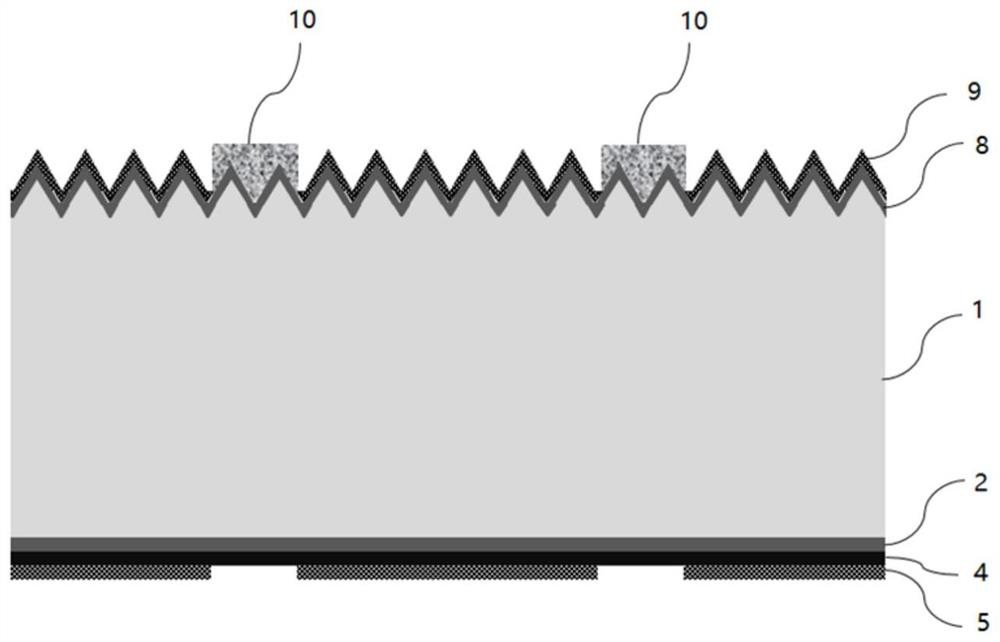

[0107] Step A2-C2: consistent with step A1-C1 provided in Example 1.

[0108] Step D2: Form a tunneling silicon oxide layer 2 with a thickness of 1-2 nm on the back and front of the N-type silicon substrate 1 by high temperature thermal oxidation method.

[0109] Step E2: forming an intrinsic polysilicon layer 3 on the back and front tunnel silicon oxide layers 2 of the N-type silicon substrate 1 by LPCVD / PVD.

[0110] Step F2: doping the intrinsic polysilicon layer 3 on the back side with phosphorus by ion implantation, and performing annealing to form an N-type doped polysilicon layer 4, wherein the N-type doped polysilicon layer has a thickness of 80- Between 200nm.

[0111] Step G2: removing the intrinsic polysilicon layer 3 on the front side of the N-type silicon substrate 1 with potassium hydroxide solution or sodium hydroxide solution, and then removing the tunneling silicon oxide layer 2 and borosilicate glass on the front side with HF acid solution.

[0112] Step H2...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com