Two-stage excitation self-destruction chip based on array type pore channels, and preparation method thereof

An array and channel technology, which is applied in the field of information security and semiconductor devices, can solve the problems of complex structure design, poor safety and reliability, etc., and achieve the effects of ensuring safety, reducing dose and chip area, and realizing directional and fixed-point damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

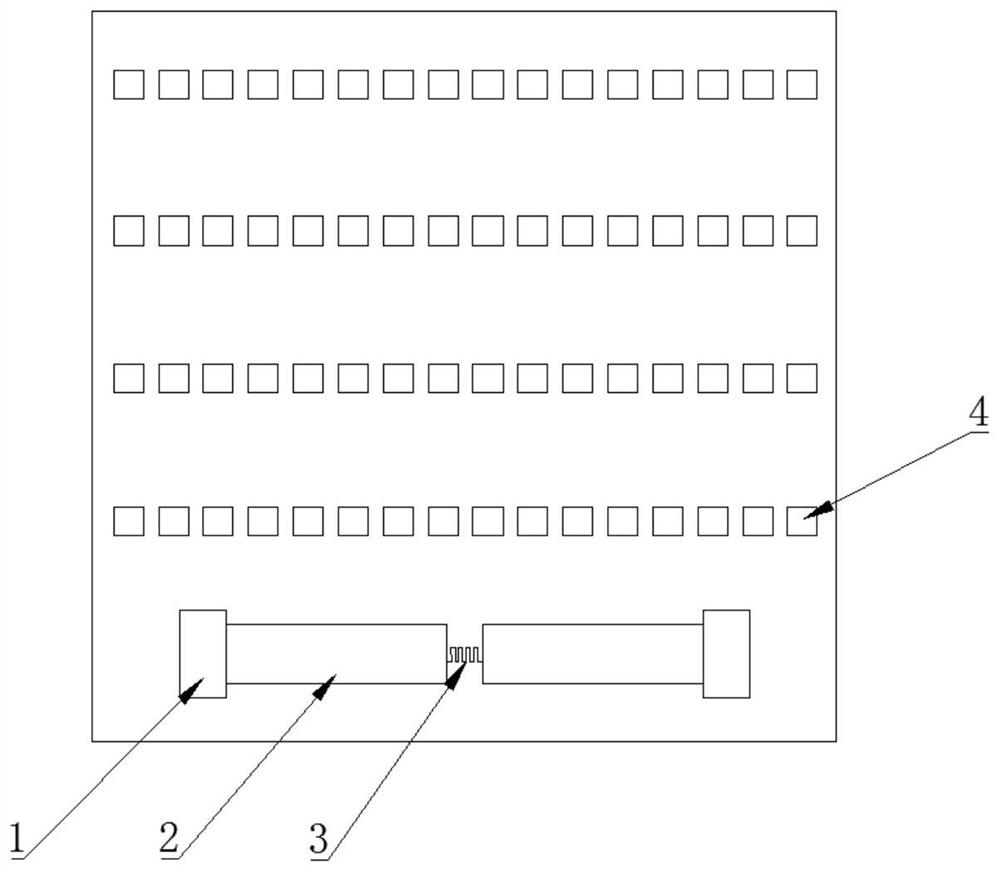

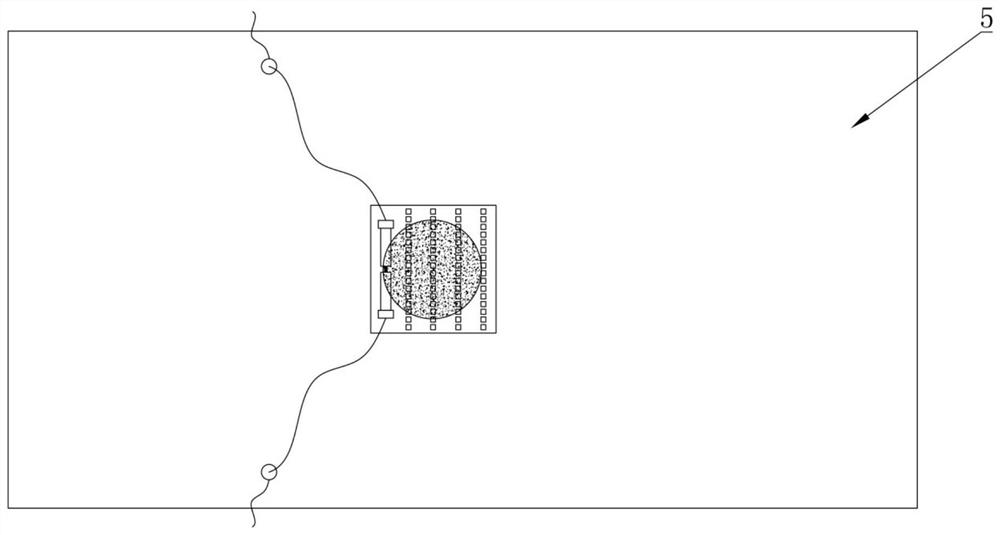

[0059] In this embodiment, the secondary excitation self-destruct chip based on the array channel is as follows: Figure 1-3 shown. The secondary excitation self-destruction chip based on the array hole includes a base layer and a self-destruction structure.

[0060] The base layer is the target chip 5 .

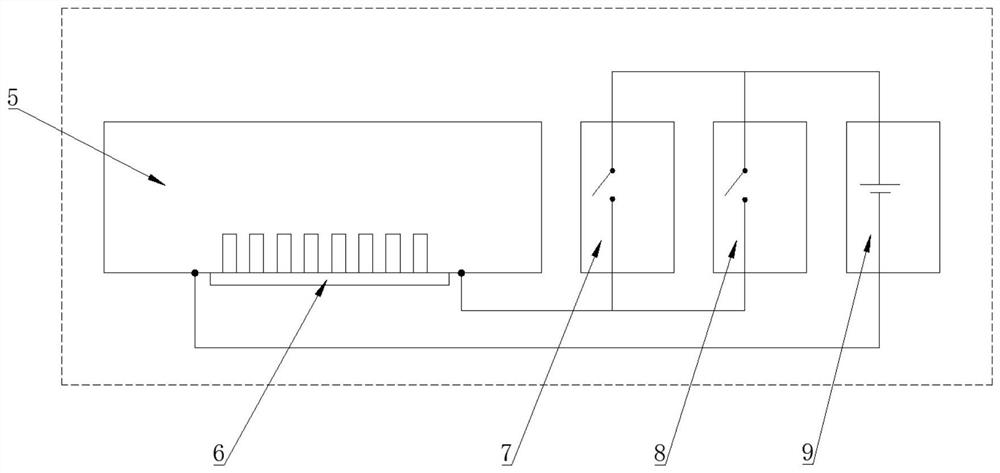

[0061] The self-destruct structure is arranged on the back of the target chip 5 and includes a heating circuit, a plurality of holes 4 , an energetic material layer 6 , a photosensitive switch 7 , a force sensitive switch 8 and a power supply 9 . The holes 4 are arranged in an array in the area to be damaged on the target chip 5 , and the energetic material layer 6 covers the heating area of the heating circuit and part of the hole array area.

[0062] The heating circuit includes an electrode pad 1, two metal wires 2 and a heating wire 3. The electrode pad 1 includes a positive electrode pad and a negative electrode pad, and the positive electrode pad and the negative e...

Embodiment 2

[0067] The following describes the preparation method of the secondary excitation self-destruct chip based on the arrayed channel provided in Example 1. In this example, the base material of the substrate is a silicon single crystal substrate, and the specific steps are as follows:

[0068] S1. Provide a silicon single crystal substrate, prepare an insulating layer on the back of the silicon single crystal substrate, and deposit a metal conductive layer on the surface of the insulating layer:

[0069] S11. Cleaning preparation: clean the silicon single crystal substrate, ultrasonically clean the silicon single crystal substrate with acetone, ethanol, and deionized water for 10 minutes respectively, take it out, dehydrate and dry it under nitrogen atmosphere at 300°C, and set aside;

[0070] S12. Oxide film preparation: After the treatment in step S11, place the silicon single crystal substrate vertically on the sample holder, push it into the thermal oxidation furnace, close th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com