GaN film and preparation method thereof

A thin film and thin film layer technology, applied in the field of GaN thin film and its preparation, can solve problems such as Ga-Si melting back etching, achieve the effect of avoiding melting back etching, avoiding quantum confinement Stark effect, and improving quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

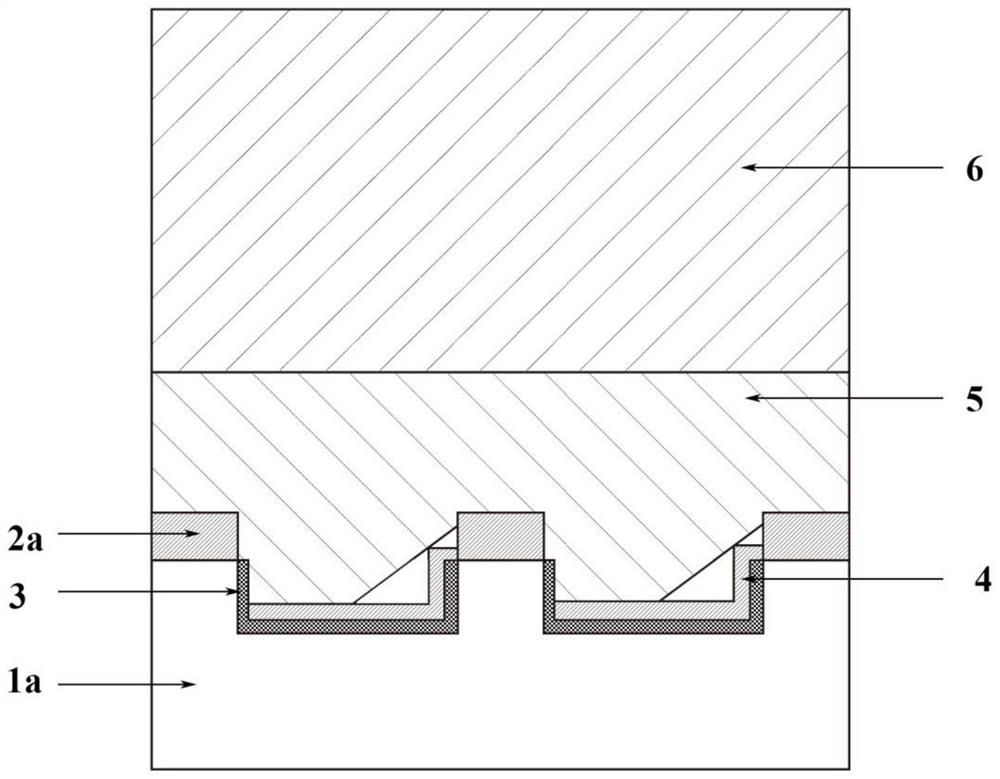

[0035] Such as figure 1 As shown, a GaN thin film, including Si substrate 1a and SiO patterned on Si substrate 1a 2 A mask layer 2a, the Si {111} crystal plane of the Si substrate 1a has Si 3 N 4 buffer layer 3, the SiO 2 Mask layer 2a and Si not involved in GaN growth 3 N 4 Buffer layer 3 with sputtered SiO 2 Film 4; the Si involved in GaN growth 3 N 4 There is a GaN insertion layer 5 on the buffer layer 3 , and a GaN thin film layer 6 is grown on the GaN insertion layer 5 . The SiO 2 The mask layer 2 a has a thickness of 50-100 nm and is a strip mask layer, wherein the width of the strip mask layer is 1-3 μm, and the distance between each strip mask layer is 3-10 μm. The Si that does not participate in GaN growth 3 N 4 The buffer layer 3 has a thickness of 20-100nm, the GaN insertion layer 5 has a thickness of 200-400nm, and the sputtered SiO 2 The thickness of the film 4 is 40-60nm, and the thickness of the GaN thin film layer 6 is 1000-2000nm.

[0036] Wherein...

Embodiment 2

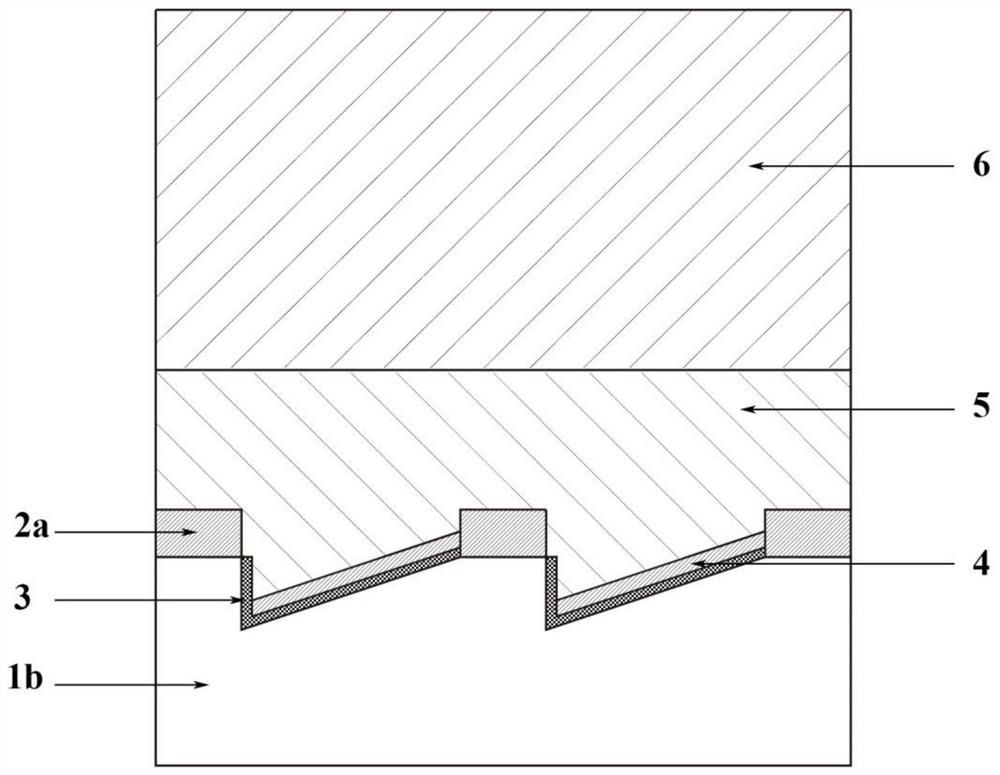

[0041] Such as figure 2 Shown: the difference between this embodiment 2 and embodiment 1 is only that the Si substrate 1b of the GaN thin film has a (112) crystal orientation, and the crystal plane of the Si substrate 1b includes a (112) crystal plane, so The etched Si{111} includes (-1-11) crystal plane and (111) crystal plane; used for growing Si 3 N 4 The Si{111} crystal plane of the buffer layer 3 is the (-1-11) crystal plane; the crystal plane on which the GaN thin film layer 6 is grown is the (1-100) crystal plane.

Embodiment 3

[0043] A method for preparing a GaN film, specifically comprising the steps of:

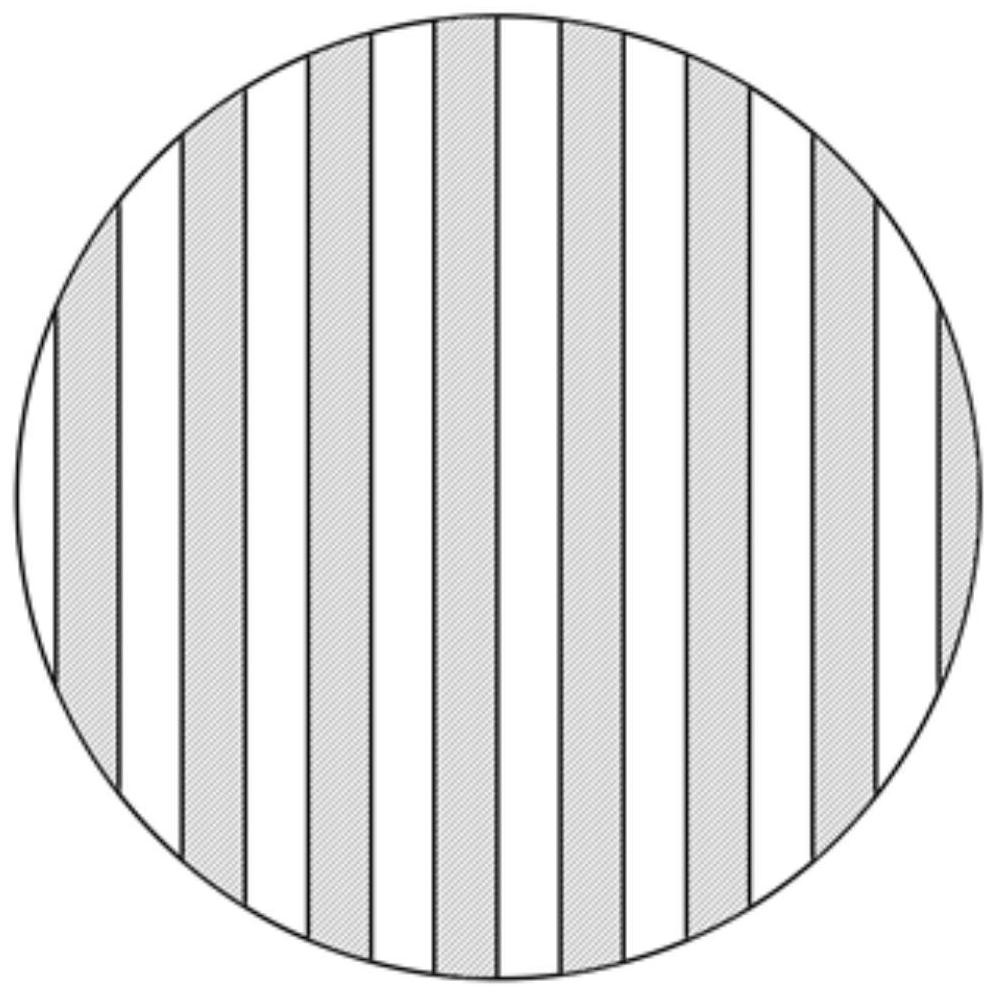

[0044] Step 1), grow a layer of 50-100nm SiO on the substrate 1a of Si(110) by plasma-enhanced chemical vapor deposition (PECVD) 2 Film 2, photoresist pattern transferred to SiO by photolithography process 2 film 2, and then patterned SiO was fabricated by inductively coupled plasma (ICP) etching 2 mask layer 2a, the SiO 2 The mask layer 2a is a strip mask layer, wherein the width of the strip mask layer is 1-3 μm, and the distance between each strip mask layer is 3-10 μm, such as image 3 shown; then, by wet etching, use a KOH solution with a mass concentration of 20%-40% at a temperature of 30°C-40°C for 10-20min, etch to form a groove on the surface of the Si substrate 1a, The sides of the groove are Si {111} crystal planes, including (-111) crystal planes and (1-1-1) crystal planes, such as Figure 5 shown;

[0045] Step 2), nitriding the Si {111} crystal plane etched in step 1), that is...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com