Extended multilevel boost inverter topology and modulation method

A step-up inverter and multi-level technology, which is applied to electrical components, AC power input conversion to DC power output, output power conversion devices, etc., can solve the problem that the level gain cannot be changed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

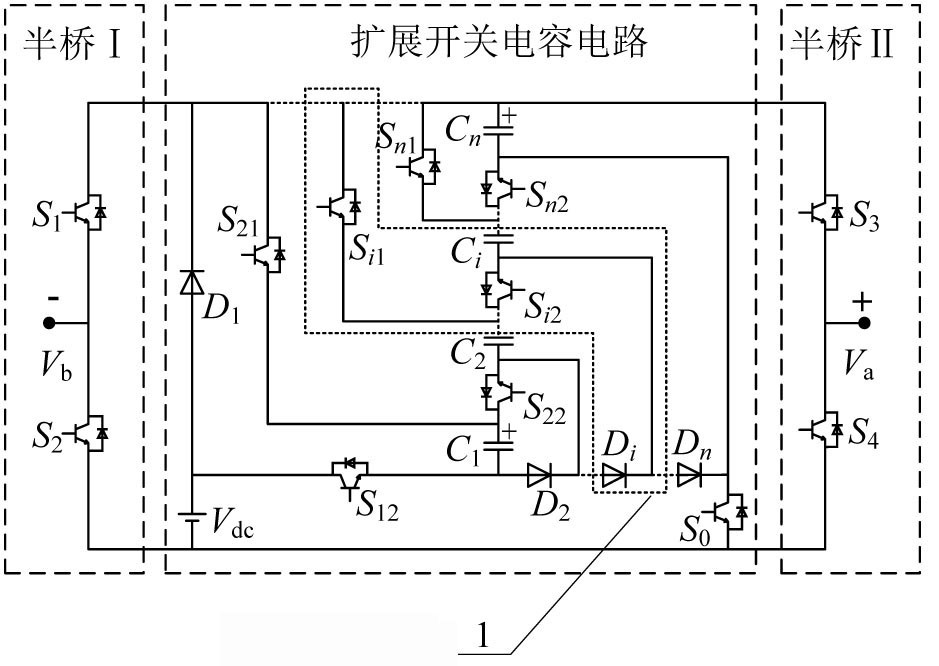

[0030] as attached figure 1 As shown, an extended multi-level boost inverter topology, which includes half-bridge I, half-bridge II and extended switched capacitor circuit; wherein, the midpoint of the half-bridge I and the midpoint of the half-bridge II as The AC output terminal of the extended switched capacitor multi-level boost inverter topology;

[0031] The half-bridge I includes a switching tube S 1 with switch S 2 , the half-bridge II includes a switch S 3 with switch S 4; The extended switched capacitor circuit includes a switched capacitor basic module and at least one level of switched capacitor sub-module 1; the switched capacitor basic module includes a switch tube S 12 , switch tube S 0 , Diode D 1 and electrolytic capacitor C 1 , the switched capacitor sub-module 1 includes a switch tube S i1 , switch tube S i2 , Diode D i and electrolytic capacitor C i , (i=2,3,...,n);

[0032] Among them, the switching tube S of the half-bridge I 1 collector of th...

Embodiment 2

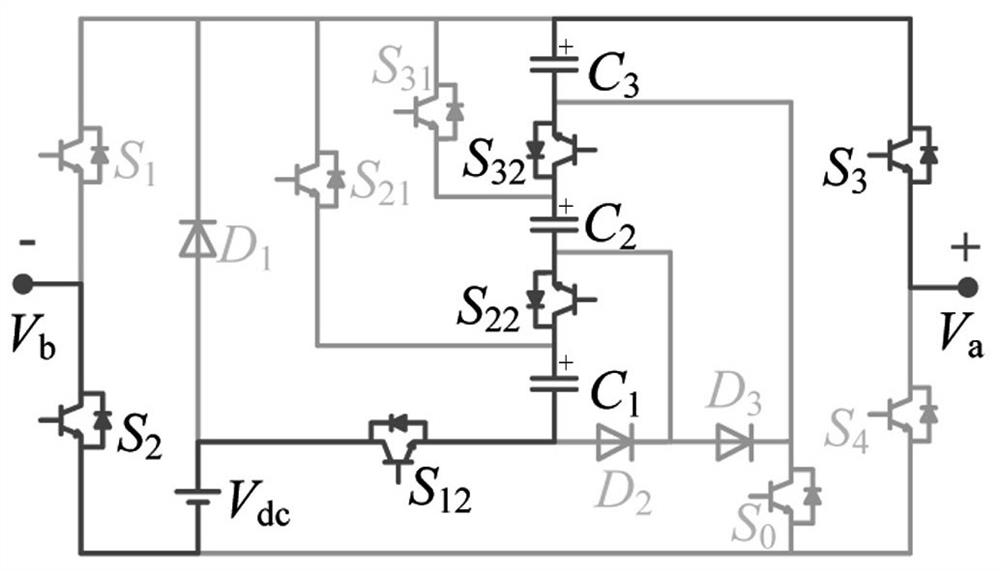

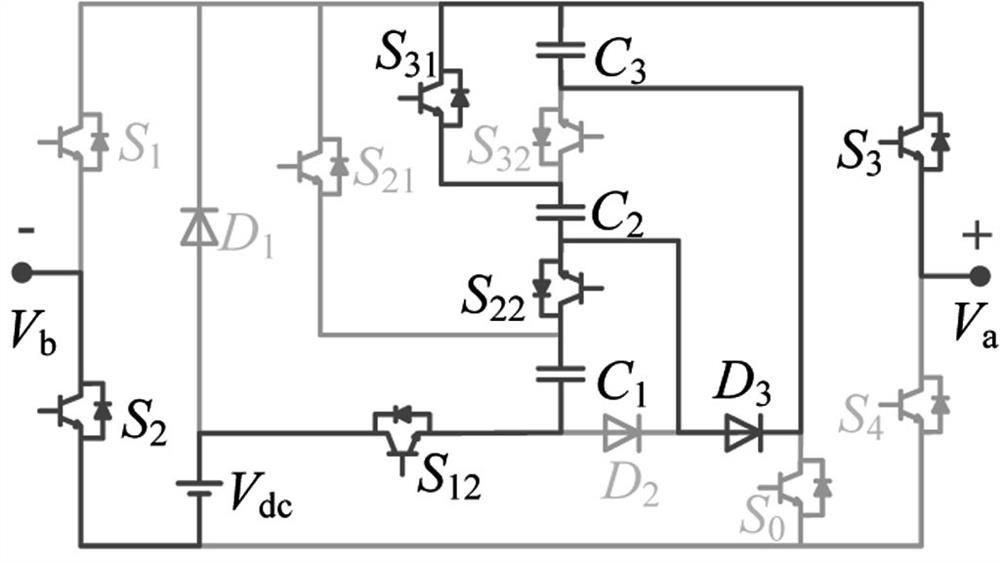

[0048] This embodiment provides a specific implementation manner of extending three switched capacitor sub-modules, as shown in Figure 2(a)-(i) of the accompanying drawings.

[0049] When a 3-level switched capacitor sub-module is configured, the extended multi-level boost inverter topology works in 9 modes:

[0050] Mode 1, as shown in Figure 2(a): switch tube S 2 , switch tube S 3 , switch tube S 12 , switch tube S 22 and switch tube S 32 is turned on, the rest of the switches are turned off, and the diode D 1 , Diode D 2 and diode D 3 Reverse bias cut-off; at this time, the electrolytic capacitor C 1 , electrolytic capacitor C 2 , electrolytic capacitor C 3 with DC input supply V dc Series discharge, inverter topology output 4V dc ;

[0051] Mode 2, as shown in Figure 2(b): switch tube S 2 , switch tube S 3 , switch tube S 12 , switch tube S 22 and switch tube S 31 is turned on, the rest of the switches are turned off, and the diode D 1 and diode D 2 Reve...

Embodiment 3

[0070] An extended multi-level boost inverter system, including a controller and an inverter topology, the inverter topology is the above-mentioned extended multi-level boost inverter topology; the controller includes DSP and FPGA and peripheral circuits, the The controller is communicated with the inverter topology, so as to realize the adjustment of the working mode by adjusting the on-off of the switch tube. When the controller controls the actions of the switch tubes in the extended multi-level boost inverter topology, it executes the steps of the above-mentioned extended multi-level boost inverter topology modulation method.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com