Semiconductor structure and preparation method thereof

A semiconductor and manufacturing method technology, applied in the field of semiconductor structure and preparation, can solve the problems of poor isolation effect of shallow trench isolation structure, etc., achieve the effect of improving isolation effect, reducing narrow channel effect, and avoiding edge notch defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

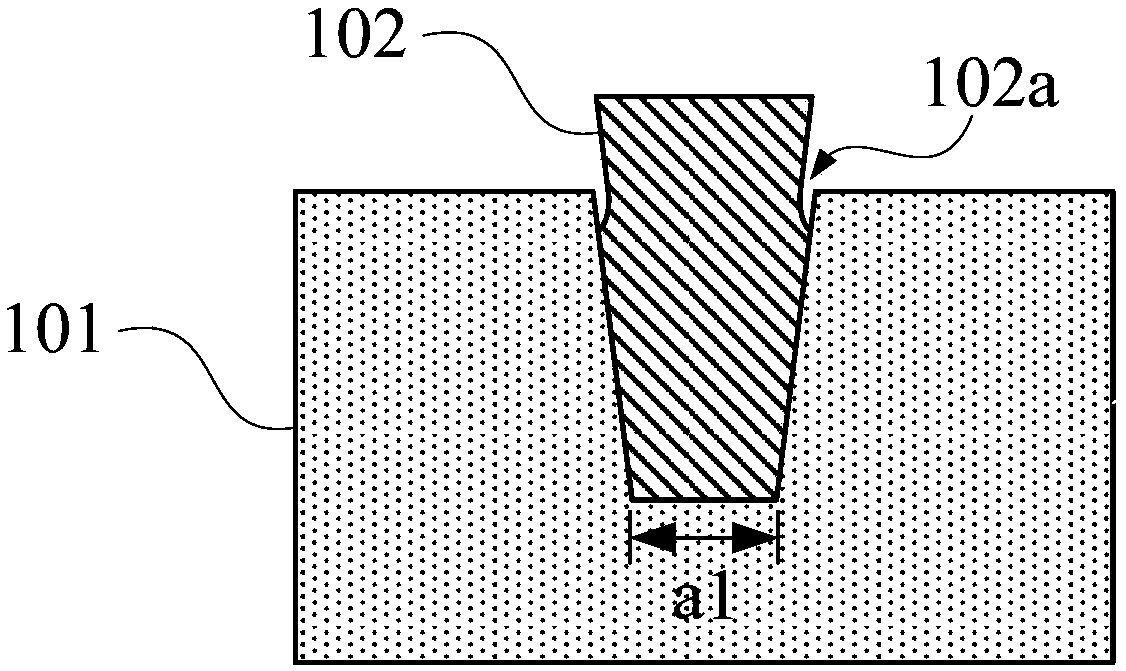

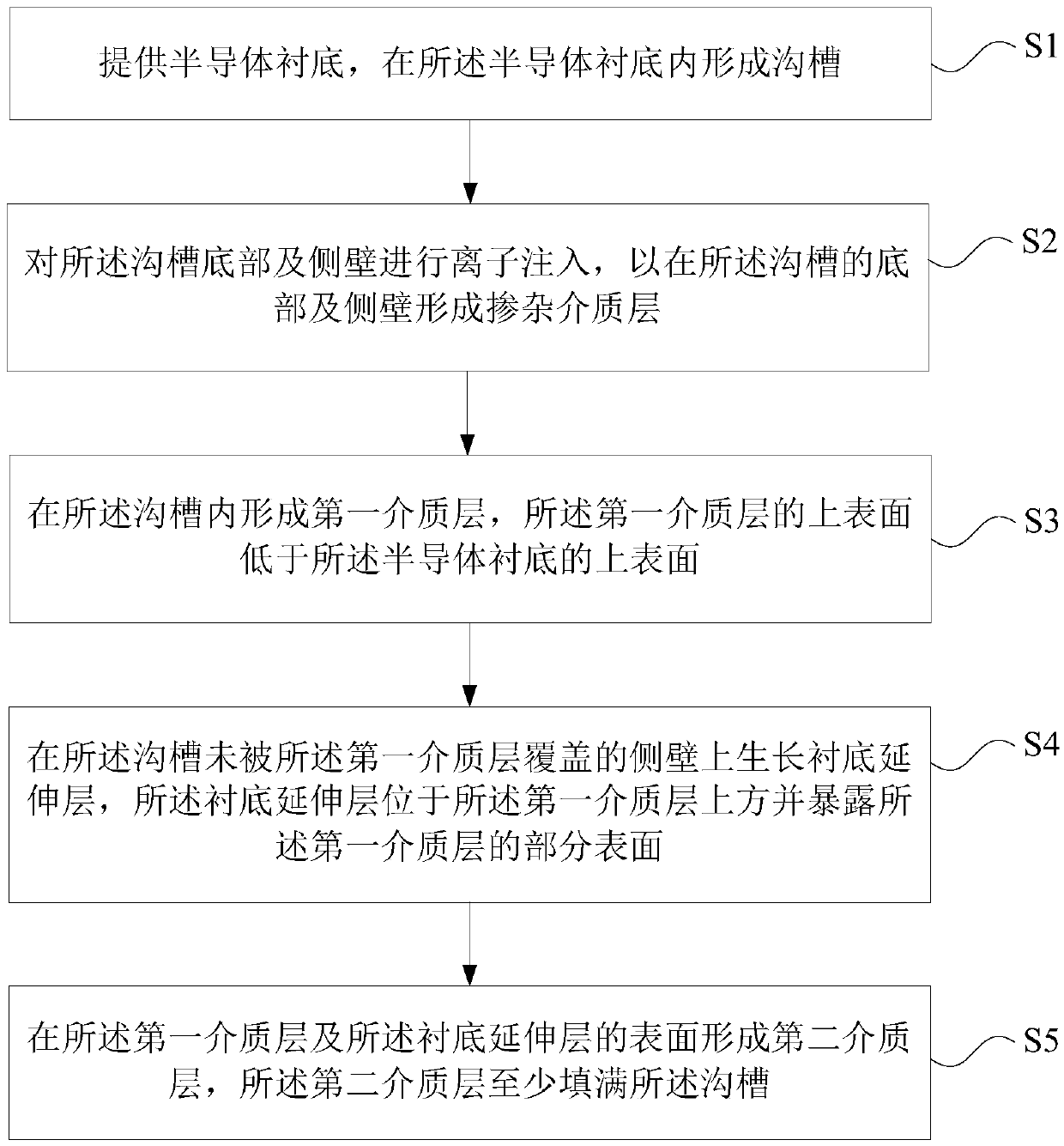

[0079] like figure 1 As shown, it is a schematic cross-sectional view of a shallow trench isolation structure obtained by using the prior art. The silicon dioxide dielectric layer 102 is filled in the trench formed on the silicon substrate 101 to form a shallow trench isolation structure, and in the subsequent process, it is generally necessary to use wet etching to remove the surface of the silicon substrate 101. The dielectric layer is simultaneously etched into the silicon dioxide dielectric layer 102 in the trench, and an edge gap 102a is formed at the edge of the trench. The edge notch 102a will form an additional leakage current channel in the subsequent process, which will affect the isolation effect and even cause the device to fail. In addition, the bottom width a1 of the shallow trench isolation structure also has a great influence on the leakage performance of the shallow trench isolation structure, and the narrow bottom width a1 will cause substrate leakage curren...

Embodiment 2

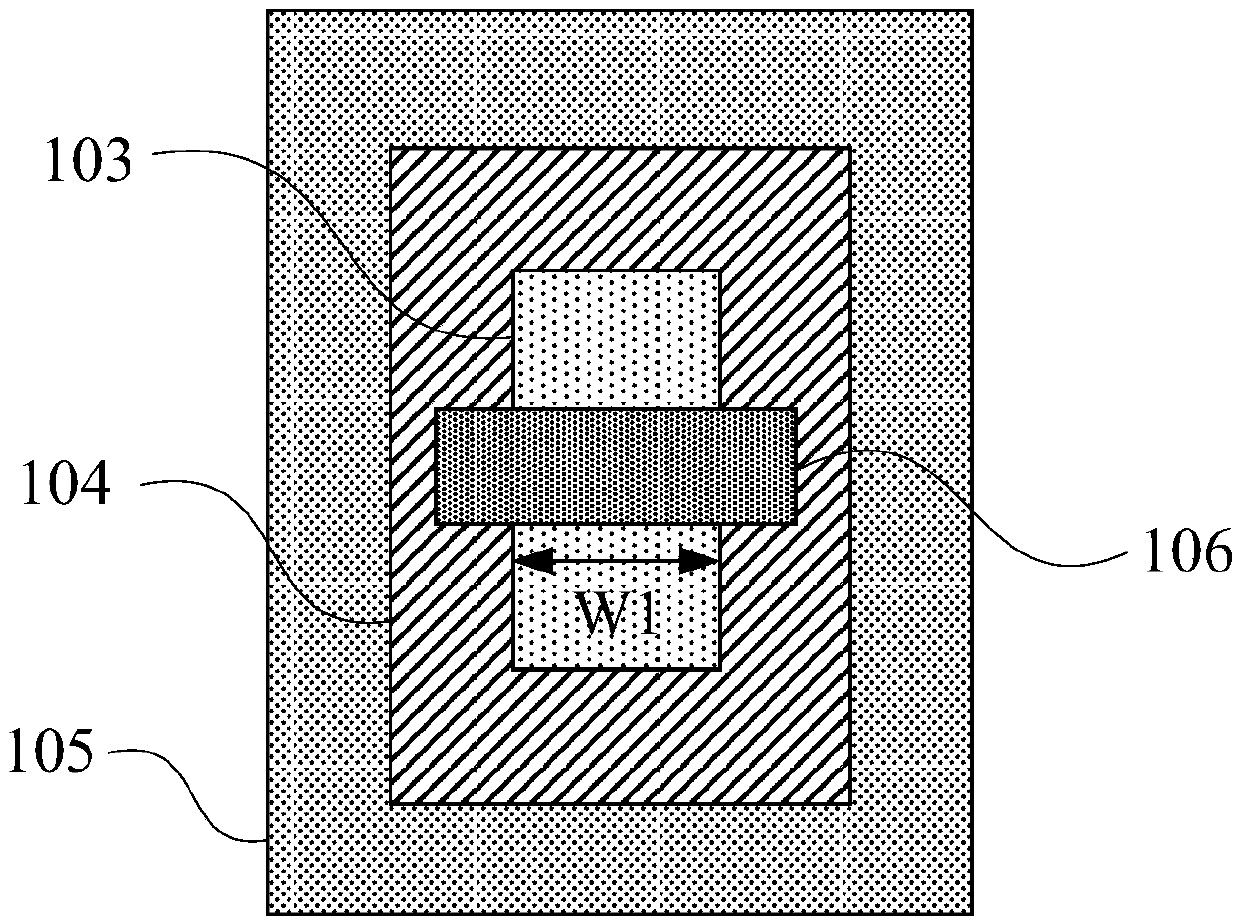

[0095] see Figure 14 , the present invention also provides a semiconductor structure, comprising:

[0096] semiconductor substrate 201;

[0097] a trench 201a is formed in the semiconductor substrate 201;

[0098] A doped dielectric layer 202 is formed on the bottom and sidewalls of the trench 201a;

[0099] The first dielectric layer 203 is formed in the trench 201a, and the upper surface of the first dielectric layer 203 is lower than the upper surface of the semiconductor substrate 201;

[0100] a substrate extension layer 201b, formed on the sidewall of the trench 201a not covered by the first dielectric layer 203, and extending to cover part of the surface of the first dielectric layer 203; and

[0101] The second dielectric layer 204 is formed on the surfaces of the first dielectric layer 203 and the substrate extension layer 201b, and at least fills the trench 201a.

[0102] like Figure 14 As shown, trenches 201a are formed in a semiconductor substrate 201, which...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com