Solder mask zero-clearance PCB preparation method

A PCB board and solder mask technology, applied in the field of PCB board preparation with zero clearance for solder mask, can solve the problems of solder mask bridge falling off, excessive undercut, electrical performance failure, etc., to ensure completeness, avoid excessive undercut, The effect of reducing the difficulty of the process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] Such as Figure 1-4 As shown in, a method for preparing a PCB board with solder resistance and zero clearance provided by an embodiment of the present invention includes the following steps:

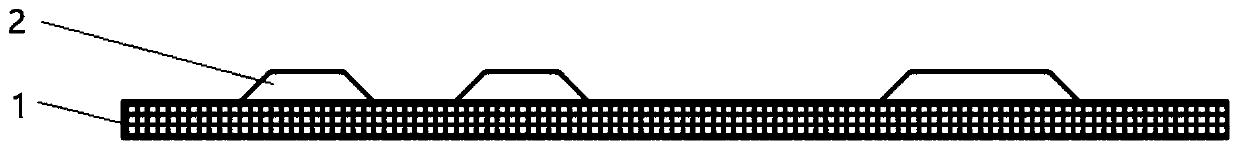

[0036] S1, feeding, place the base material 1 on the processing station, and fix it (such as figure 1 shown);

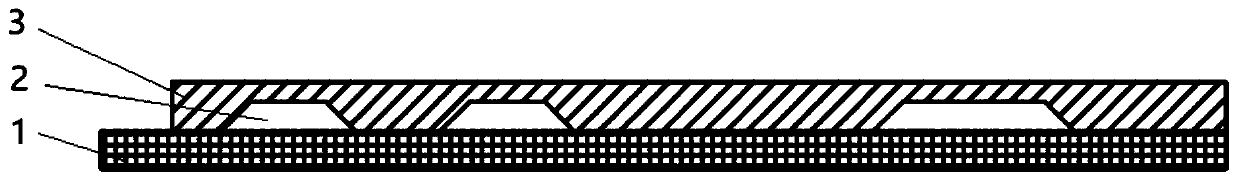

[0037] S2. For the first screen printing, the screen printing process of stretching, degreasing, pre-drying, exposure, development, and drying is carried out in sequence. In the exposure process, selective exposure is used to reserve the window area of the substrate 1 to complete the first screen printing. get semi-finished products (such as figure 2 shown);

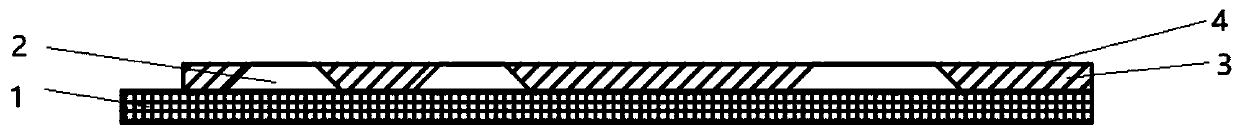

[0038] S3, grind the plate, adopt the process of mechanical brushing to carry out template processing to the semi-finished product, remove the ink layer 3 on the surface of the circuit 2 and the surface of the pad 4, and keep the ink layer 3 between the lines 2 (such as image 3 shown);

[0039] S4, cleanin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com