Double-gate vacuum field emission triode structure and preparation method thereof

A field emission and triode technology, applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve the problems of high vacuum degree requirements, complex preparation process, unfavorable circuit integration and other problems, achieve good electron emission performance, simple preparation process, Effect of Good Electron Transport Properties

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

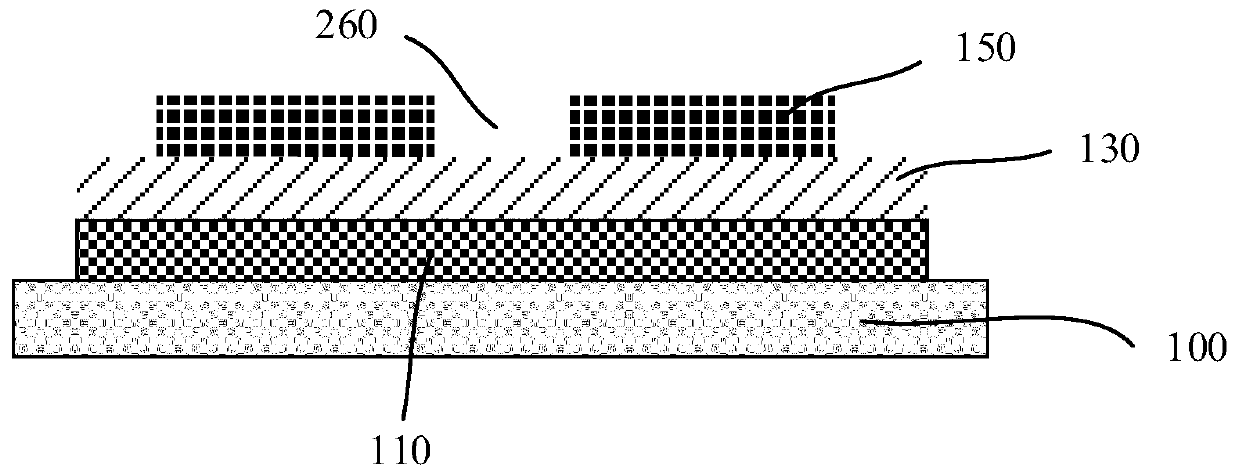

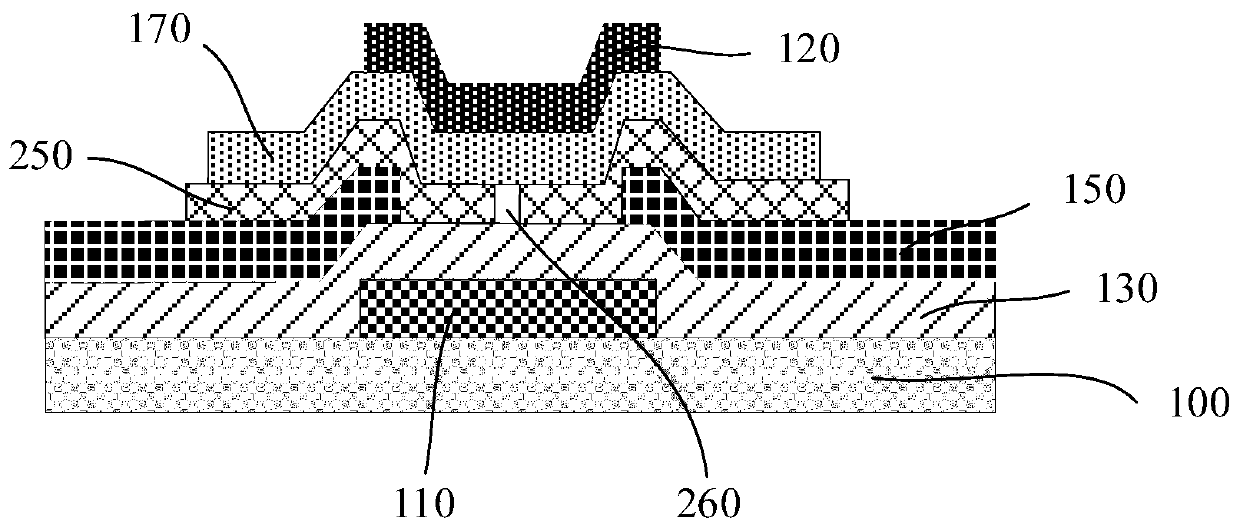

[0061] A double-gate vacuum field emission transistor structure, including a bottom gate 110 deposited on a substrate 100, a bottom gate insulating layer 130 is deposited on the bottom gate 110, and a symmetrical source is deposited on the bottom gate insulating layer 130. The drain electrode 150 has a conductive film 250 deposited on the source-drain electrode 150, a top gate insulating layer 170 is deposited on the conductive film 250, and a top gate 120 is deposited on the top gate insulating layer; between the symmetrical source-drain electrodes 150 An electrode gap of 5-15 μm is provided between them; a nanoscale vacuum channel 260 is provided in the middle of the conductive film 250 .

[0062] The thickness of the bottom gate 110 is 50-200nm; and the bottom gate 110 is made of one or more materials among nickel, copper, platinum, silver, chromium and molybdenum.

[0063] The bottom gate insulating layer 130 has a thickness of 50-250 nm; and the bottom gate insulating lay...

Embodiment 2

[0072] see image 3 with Figure 4 , is a schematic diagram of a double-gate VFET device structure disclosed in the present invention, including a bottom gate 110, a bottom gate insulating layer 130, a source-drain electrode 150, a conductive film 250, a top gate insulating layer 170, a top gate 120 and a vacuum channel 260 .

[0073] The fabrication process of the structure, the specific steps are as follows:

[0074] 1) Fabricate the bottom grid 110 on the substrate 100 by magnetron sputtering or electron beam evaporation, the bottom grid has a thickness of 50-200 nm, a length of 300-500 μm, and a width of 20-50 μm;

[0075] 2) Fabricate the bottom gate insulating layer 130 on the bottom gate 110 by chemical vapor deposition or magnetron sputtering, and the thickness of the bottom gate insulating layer is 50-250nm;

[0076] 3) Fabricate symmetrical source-drain electrodes 150 on the bottom gate insulating layer 130 by magnetron sputtering or electron beam evaporation. Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com