N-type LDMOS employing technology of reducing surface electric field

A surface electric field and technology technology, applied in circuits, electrical components, semiconductor devices, etc., can solve the problems of high specific on-resistance, low N-type LDMOS withstand voltage, etc., to improve breakdown voltage, reduce surface electric field, leakage, etc. The effect of high pressure resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The present invention will be described in further detail below in conjunction with the accompanying drawings.

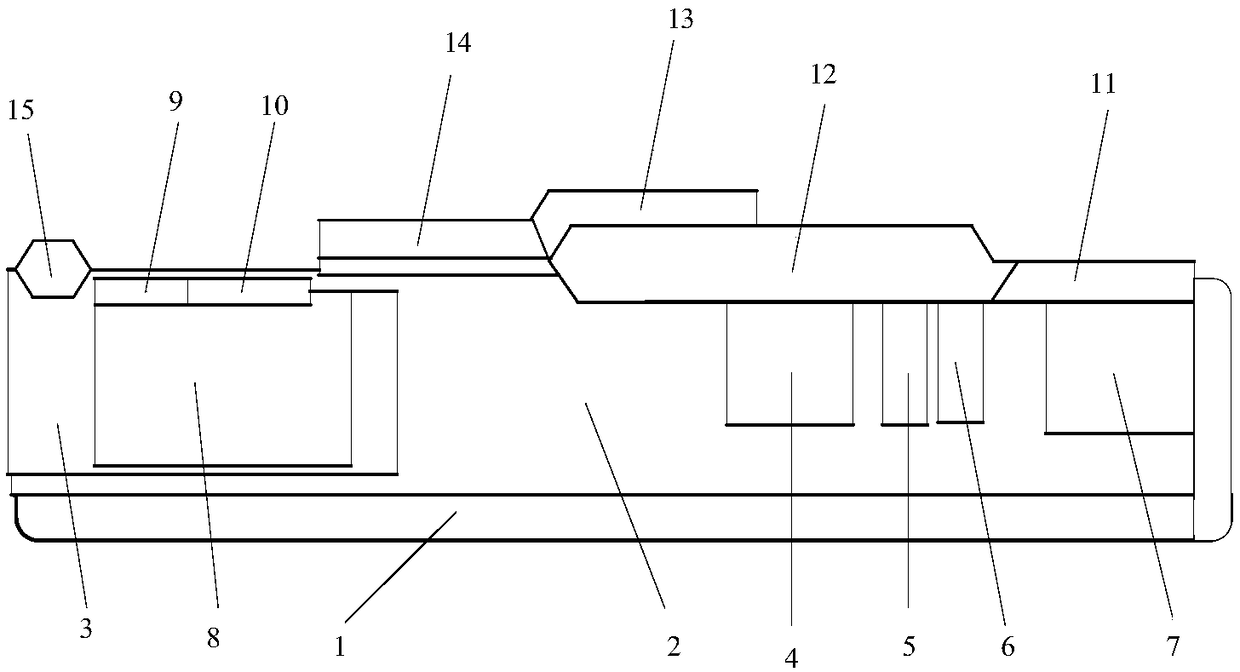

[0017] Such as figure 1 The present invention shows an N-type LDMOS using the technology of reducing the surface electric field, including a p-type substrate layer 1, the p-type sink layer 1 is formed by implanting boron ions in single crystal silicon, on the p-type substrate layer 1 The end face is a deep n well layer 2, the deep n well layer 2 is formed by implanting a large amount of phosphorus ions, and the deep n well layer 2 includes a deep p well layer 3, a p-type doped region 4, a first The drift ring 5, the second drift ring 6 and the n well layer 7, the deep p well layer 3 and the p-type doped region 4 are realized by implanting boron ions of different concentrations and energies, and the energy of the implanted ions is different to adjust The deep p well layer 3 includes a p well layer 8, the function of the p well layer 8 is to reduce the parasit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com