Circuit structure for accelerating convolutional layer and fully connected layer of neural network

A fully connected layer, neural network technology, applied in the field of integrated circuit design, can solve the problem of redundant chip area, and achieve the effect of reducing chip area, improving utilization rate, and improving work efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

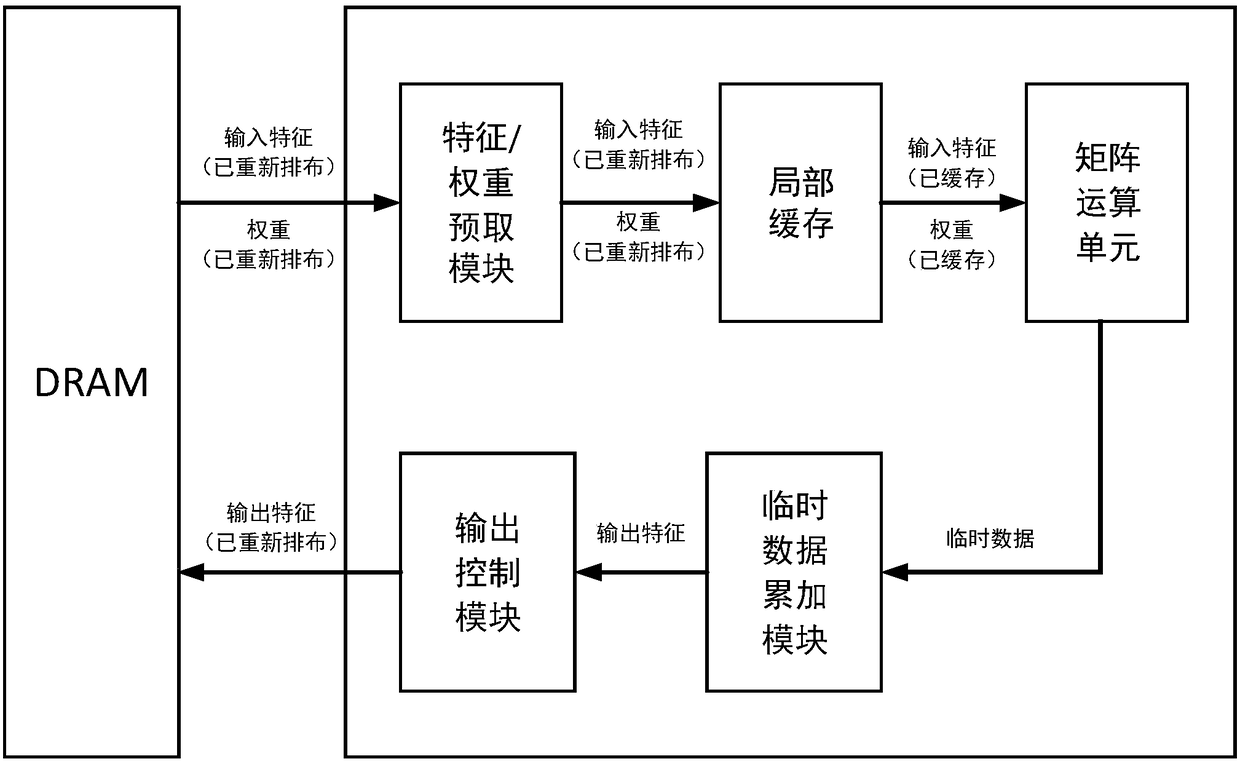

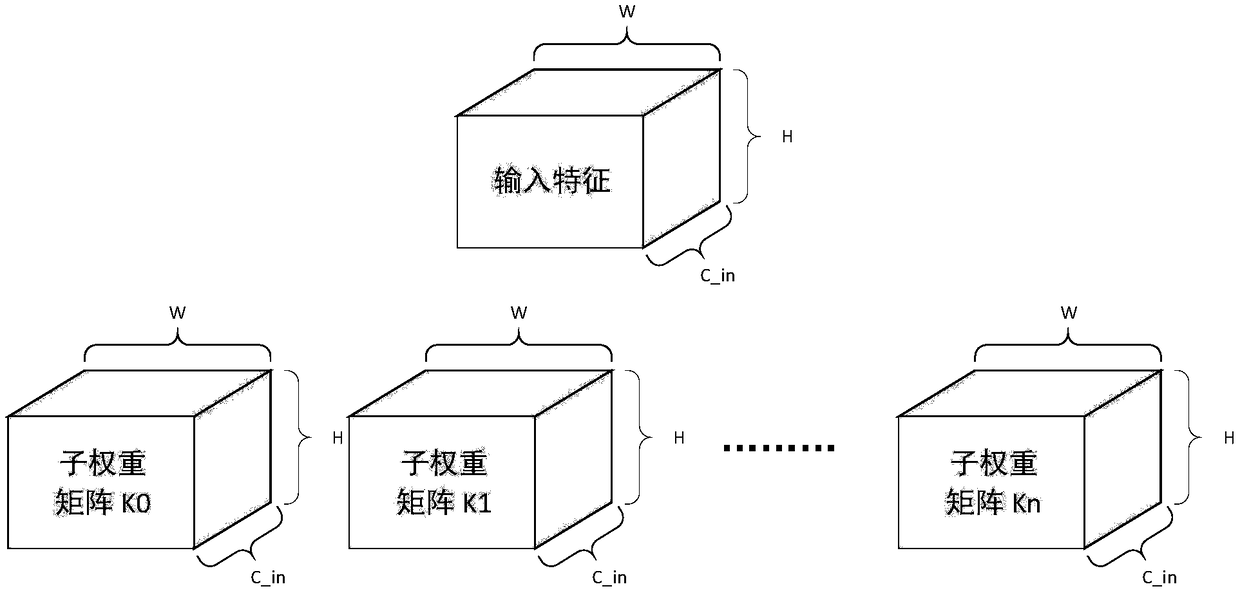

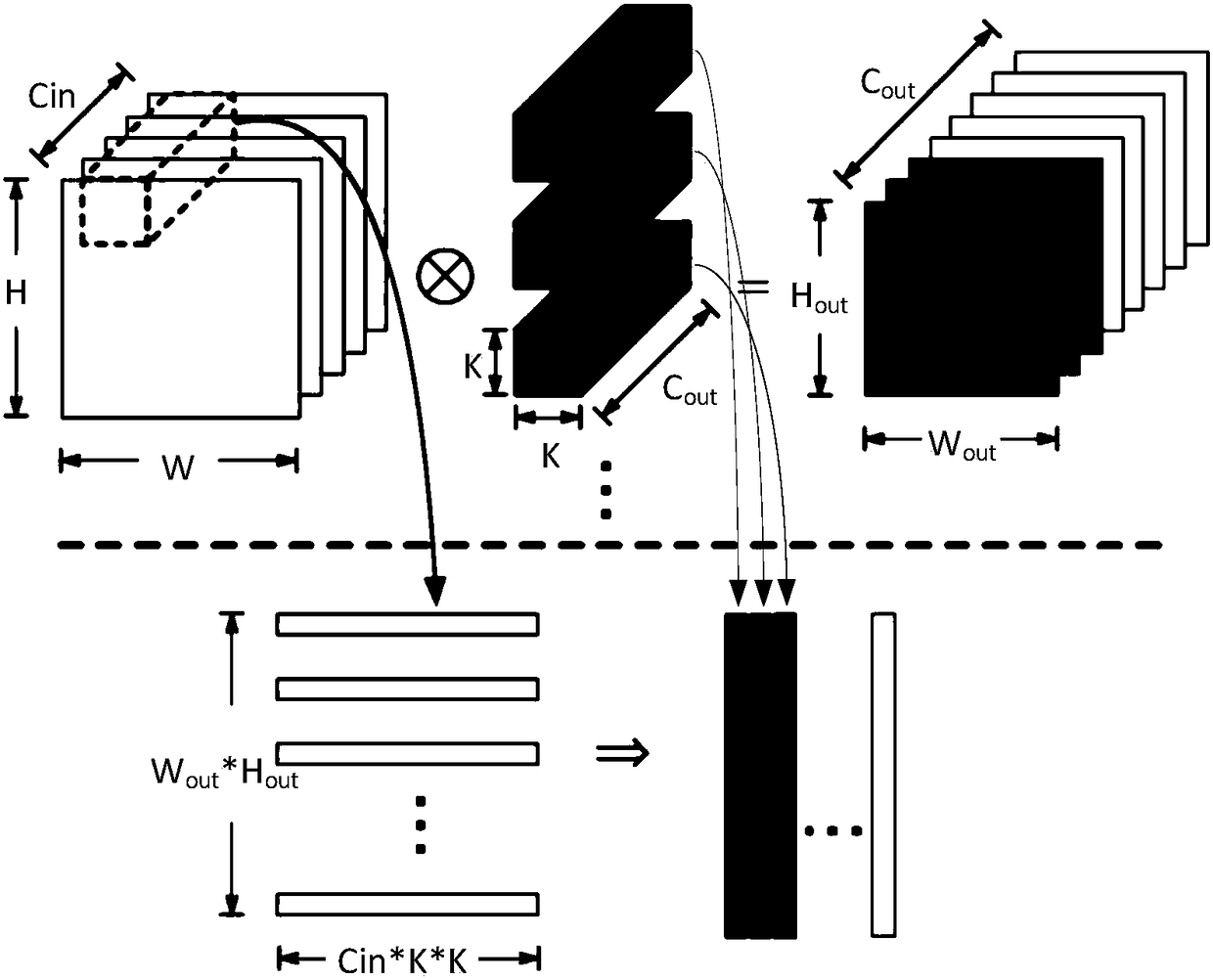

[0024] In the present invention, the basic block diagram of the circuit that can accelerate the convolutional layer and the fully connected layer at the same time is as follows: figure 1 shown. The working process of the design is as follows: input the features and corresponding weights of each layer, and store them in the external memory (DRAM) described in claim 5 . First, the feature / weight prefetching module reads the features and weights that will be involved in the operation from the external memory and puts them into the local cache. The new data will replace the old and no longer used data in the local cache; then, the control circuit will take out the features and weights that will be involved in the calculation from the local cache according to the order of operations, and send them to the matrix operation unit. After rearranging the features and weights, the operations of the convolutional layer and the fully connected layer are mapped to a series of matrix operat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com