Manufacturing process of vertical ceramic patch capacitor and capacitor product of vertical ceramic patch capacitor

A chip capacitor and manufacturing process technology, applied in the field of microelectronics, can solve problems such as inapplicability of vertical capacitors, worrying about the efficiency and accuracy of chip loading, and installation troubles, so as to save equipment and manpower investment and be compatible with automatic installation processes , the effect of ensuring integrity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

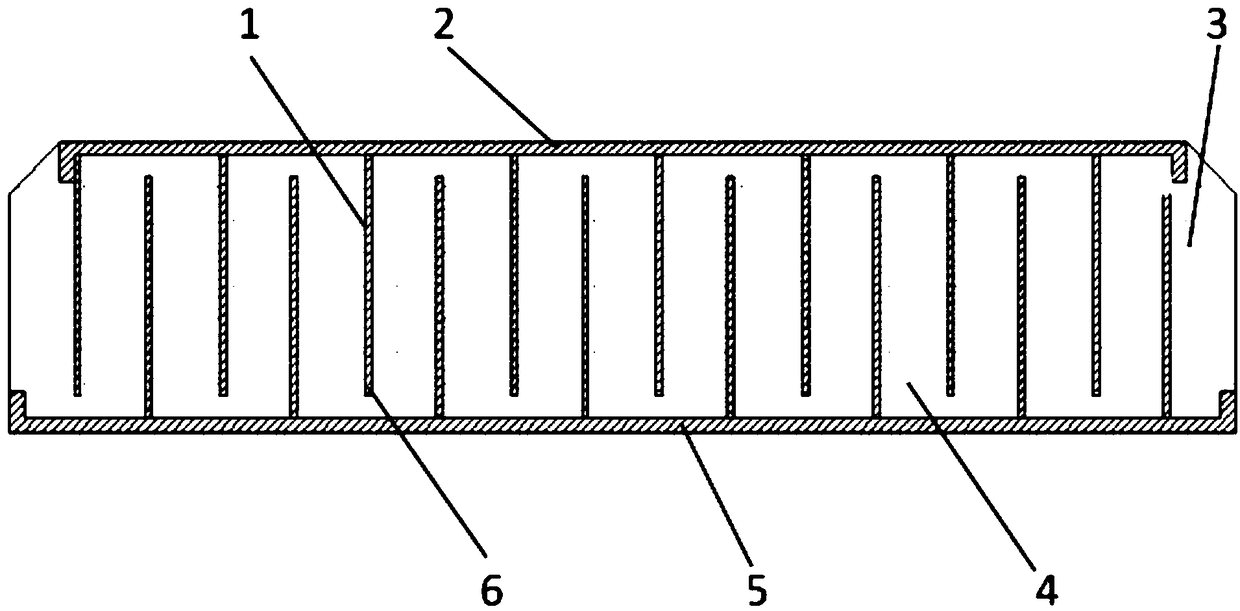

[0044] Such as figure 1 As shown, the construction principle of the vertical ceramic chip capacitor is that the upper and lower inner electrodes 6 are separated by dielectric ceramics to store and release electric energy in the form of static electricity. The capacity formula is as follows:

[0045]

[0046] C: Capacitance; ε: Dielectric constant of the insulator between electrodes; K: Dielectric constant (depending on the type of ceramic)

[0047] A: conductive area; D: thickness of dielectric layer 4 (thin strip thickness); n: number of layers (number of stacked layers);

[0048] The manufacturing process of the vertical ceramic patch capacitor of the present invention comprises the following steps:

[0049] 1) Ingredients: The main raw material barium titanate (BaTiO3) base powder is mixed with the corresponding binder, solvent, and additives according to the formula, and stirred evenly to form a ceramic slurry; the ratio of each ingredient will change due to the capac...

Embodiment 2

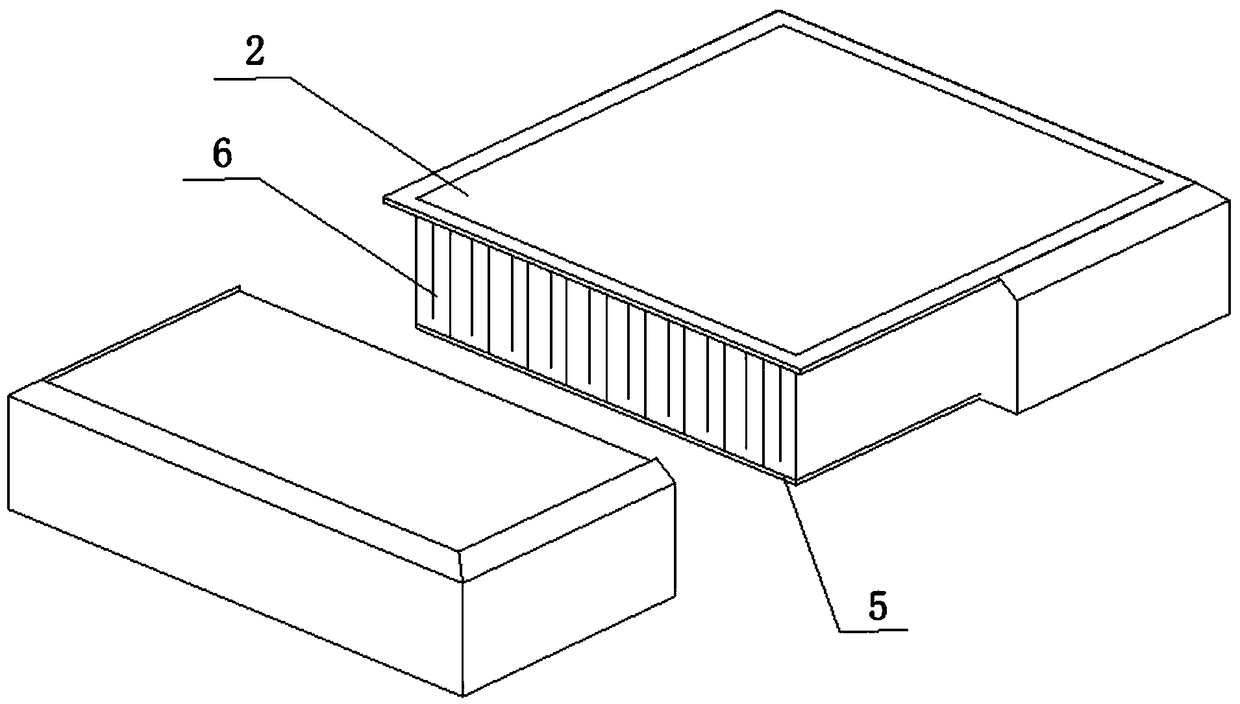

[0065] like Figure 2-4 As shown, the vertical ceramic chip capacitor of the present invention includes a capacitor body 3, and the capacitor body 3 includes an upper end face 2 and a lower end face 5, and internal electrodes 6 are arranged on the inner sides of the upper end face 2 and the lower end face 5, and the inner electrodes 6 includes an upper electrode and a lower electrode, the upper electrode and the lower electrode are vertically staggered, and one end of the upper electrode is connected to the upper end surface 2, and the other end does not touch the lower end surface 5, and the lower electrode is connected to the lower end surface 5, and the other end does not touch the upper end surface 2 , The upper end surface 2 and the lower end surface 5 are provided with a metal layer to form an external terminal electrode 7 , and the terminal electrode 7 is parallel to the mounting surface and connected to the internal electrode 6 .

[0066] In order to further illustrate...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com