Gallium nitride field effect transistor manufacturing method and gallium nitride field effect transistor

A gallium nitride field and manufacturing method technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as poor voltage resistance, and achieve the effect of improving voltage resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0020] This embodiment provides a method for manufacturing a GaN field effect transistor, which is used for manufacturing a GaN field effect transistor.

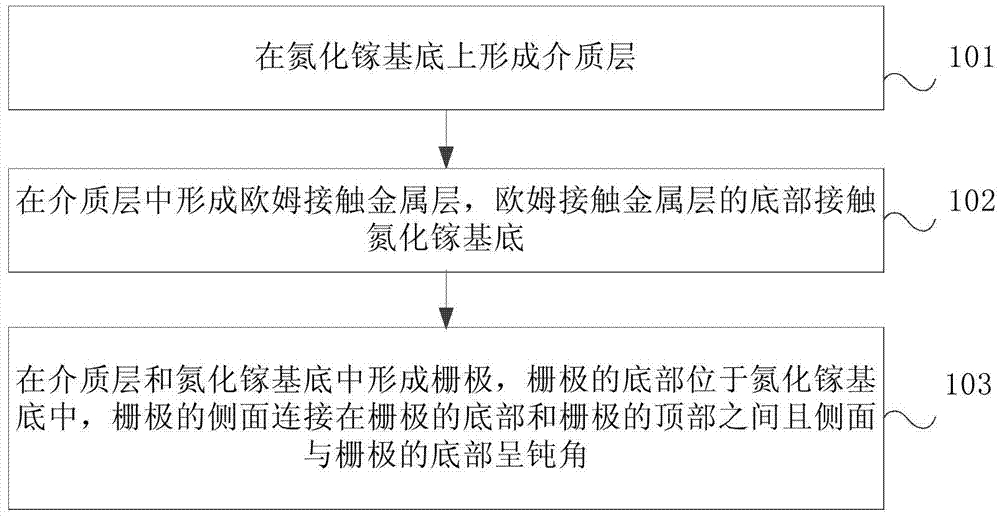

[0021] like figure 1 As shown, is a schematic flow chart of the fabrication method of the eGaN field effect transistor according to the present embodiment. The fabrication method of the gallium nitride field effect transistor includes:

[0022] Step 101, forming a dielectric layer on a gallium nitride substrate.

[0023] The dielectric layer can be composed of one layer of material, or multiple layers of material, and this step can specifically be:

[0024] forming a passivation layer on the gallium nitride substrate;

[0025] An oxide layer is formed on the passivation layer.

[0026] The passivation layer of this embodiment can be Si 3 N 4 layer, the oxide layer may be a PETEOS (Plasma enhanced tetraethyl orthosilicate, plasma enhanced deposition of tetraethoxysilane) layer.

[0027] The gallium nitride substrate in...

example 2

[0041] This embodiment provides a specific manufacturing method of a GaN field effect transistor manufacturing method. like Figures 2A to 2F Shown is a structural schematic diagram of each step in the manufacturing method of the eGaN field effect transistor according to the present embodiment.

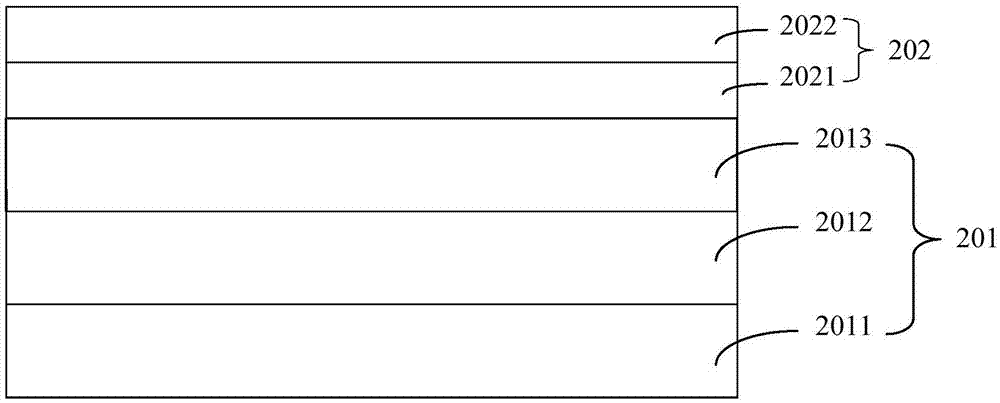

[0042] like Figure 2A As shown, a dielectric layer 202 is formed on a GaN substrate 201 .

[0043] The gallium nitride substrate 201 includes a Si substrate 2011 , a GaN layer 2012 and an AlGaN layer 2013 which are sequentially formed from bottom to top. The dielectric layer 202 in this embodiment includes a passivation layer 2021 and an oxide layer 2022. Specifically, a layer of Si may be formed on the surface of the barrier layer of the AlGaN layer 2013. 3 N 4 layer as a passivation layer 2021, and the Si 3 N 4 A PETEOS layer is formed on the layer as the oxide layer 2022.

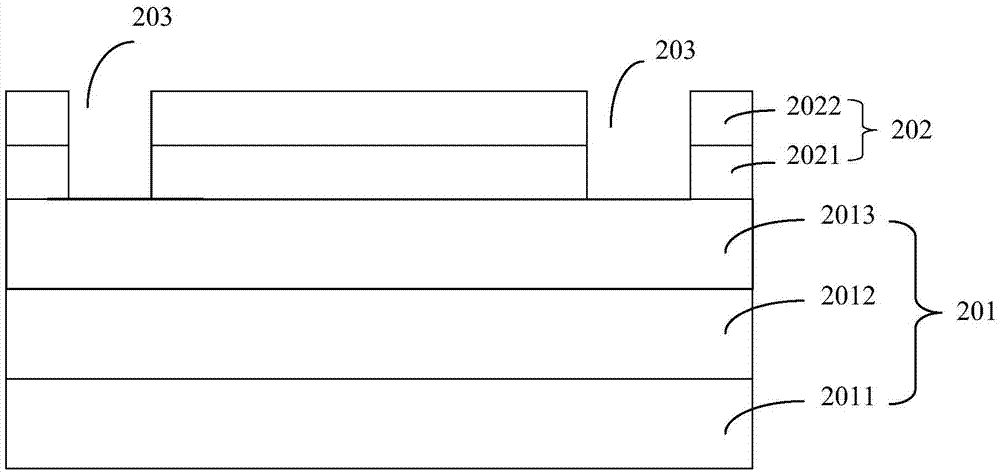

[0044] like Figure 2B As shown, an ohmic contact hole 203 is formed in the dielectric layer 202 to ex...

Embodiment 3

[0059] This embodiment provides a gallium nitride field effect transistor, which is specifically manufactured by the method of embodiment 1 or embodiment 2.

[0060] like Figure 2F As shown, the GaN field effect transistor of this embodiment includes a GaN substrate 201 , a dielectric layer 202 , an ohmic contact metal layer 205 and a gate 207 .

[0061] Wherein, the dielectric layer 202 is formed on the gallium nitride substrate 201; the ohmic contact metal layer 205 is formed in the dielectric layer 202, and the bottom of the ohmic contact metal layer 205 contacts the gallium nitride substrate 201; the gate 207 is formed in the dielectric layer 202, The bottom of the gate 207 is located in the gallium nitride substrate 201, the top 2071 of the gate 207 is higher than the dielectric layer 202 or flush with the dielectric layer 202, and the side 2073 of the gate 207 is connected to the bottom 2072 of the gate 207 and the gate 207 Between the top 2071 of the gate 207 and the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com