A kind of method for preparing SOI silicon chip with ultra-thick buried oxide layer

A technology of oxide layer and silicon wafer, which is applied in the manufacture of semiconductor/solid-state devices, electrical components, circuits, etc., can solve the problems of SOI wafer warping, poor film thickness uniformity, rough and not dense silicon dioxide layer surface, etc. Good strength, good density, and the effect of avoiding long-term high-temperature oxidation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

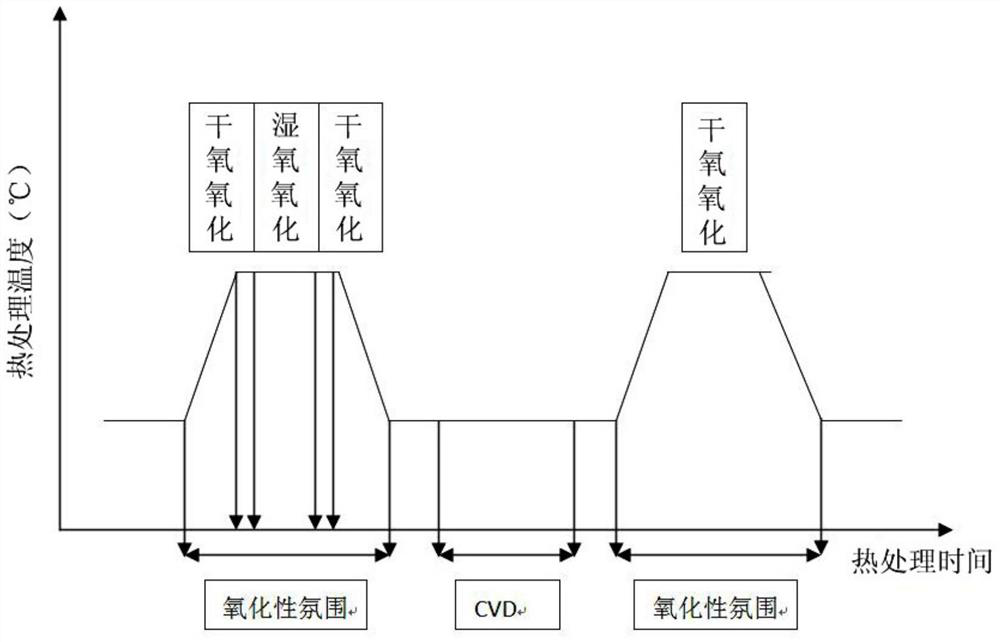

[0032] This embodiment is a method for preparing SOI silicon wafers with an ultra-thick buried oxide layer. Layer oxide layer SOI silicon chip; Wherein, the process flow of preparing buried layer oxide layer is as follows figure 1 As shown, the specific process is as follows:

[0033] 1) Loading the substrate monocrystalline silicon wafer into a sealed reaction chamber;

[0034] 2) The temperature of the reaction chamber is raised to 950°C-1100°C;

[0035] 3) Oxygen is fed into the reaction chamber (oxygen flow rate 5-10 liters / min), and the reaction time is 30-90 minutes to prepare a dense interface layer. The related reaction formula is: Si+O 2 → SiO 2 ;

[0036]4) The igniter is ignited, oxygen (oxygen flow rate 5-10 liters / min) and hydrogen (hydrogen flow rate 5-18 liters / min) are introduced into the reaction chamber, and the reaction time is 10-160 minutes to prepare a relatively dense interface layer. The related reaction formula for:

[0037] 2H 2 +O 2 →2H 2 o ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| surface roughness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com