A germanium silicon channel fin field effect transistor and its preparation method

A fin field effect, germanium-silicon channel technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of poor heat dissipation and high cost of devices, reduce area, improve heat dissipation problems, reduce cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

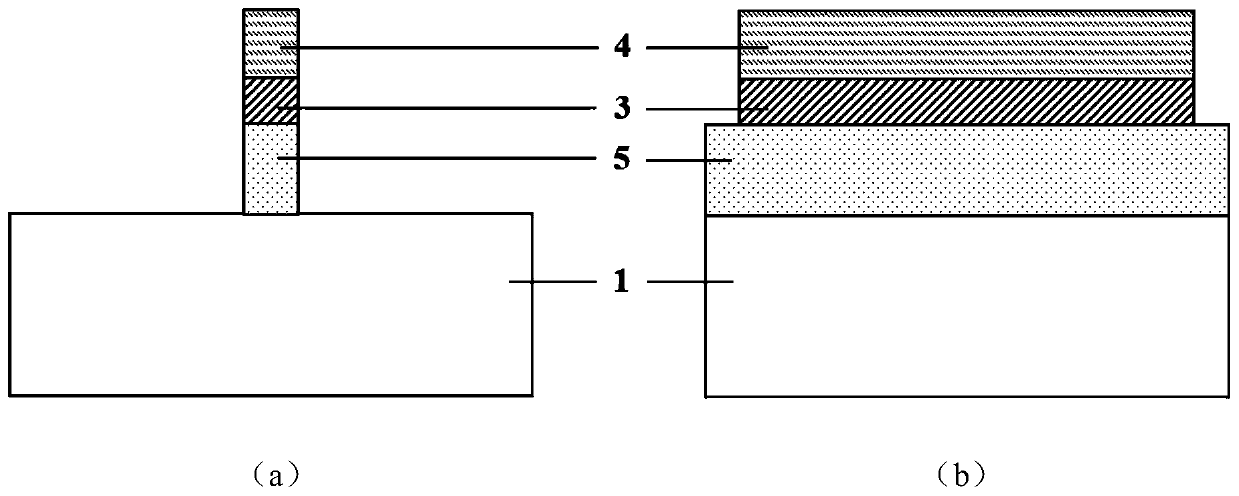

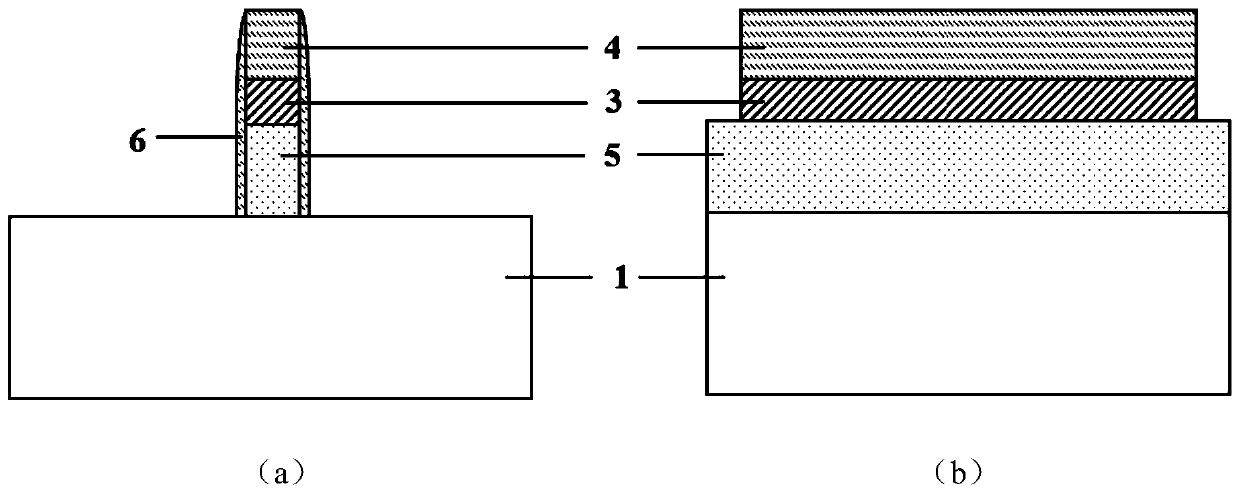

[0031] The invention forms a BOI structure through thermal oxidation, cuts off the leakage current channel between the source and the drain, can effectively suppress the leakage current of the device, and has a smaller buried oxide layer area than the SGOIFinFET, which can improve the heat dissipation effect. In addition, the use of germanium aggregation technology in the oxidation process is beneficial to increase the germanium composition in the channel, improve carrier mobility, and thus increase the on-state current. The present invention will be described in detail below in conjunction with the accompanying drawings.

[0032] A silicon germanium channel BOIFinFET can be realized according to the following steps:

[0033] Step 1. MBE grows a 50nm silicon germanium epitaxial layer 2 on a P-type (100) silicon substrate 1, deposits silicon oxide by PECVD, forms an active region by photolithography and RIE etching, and removes the glue;

[0034] Step 2. Deposit a 30nm silicon...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com