Negatron compression rate-ultra-steep sub-threshold slope field effect transistor and preparation method thereof

A field-effect transistor, sub-threshold slope technology, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve the problems of large hysteresis of ferroelectric NCFETs, easy material fatigue, high frequency dependence, etc., to reduce leakage The effect of electric current, avoiding direct contact, and simple preparation process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The present invention will be further elaborated below through specific embodiments in conjunction with the accompanying drawings.

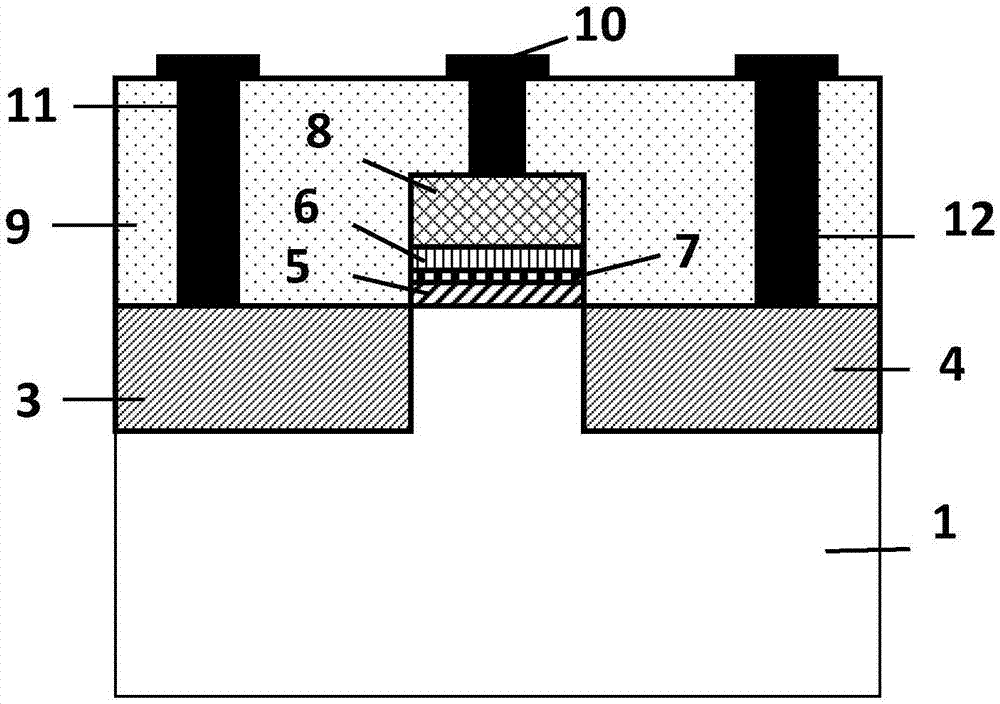

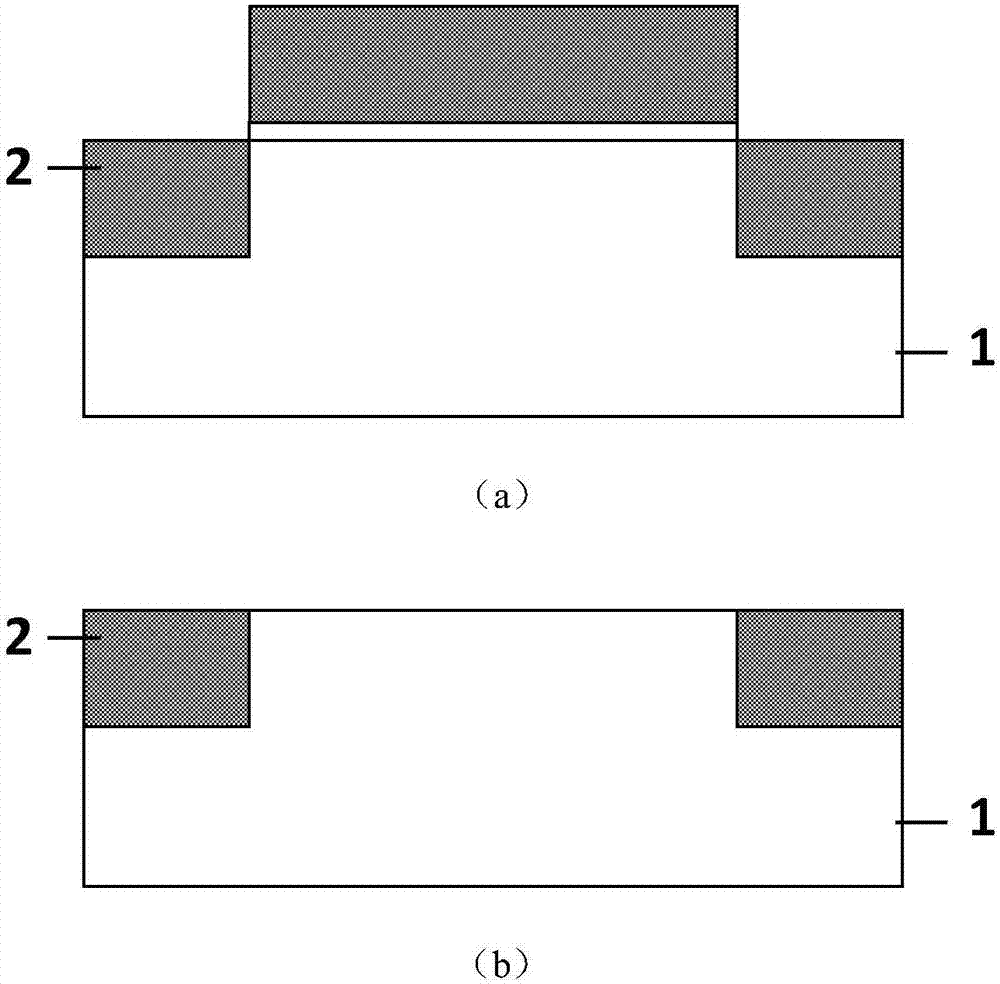

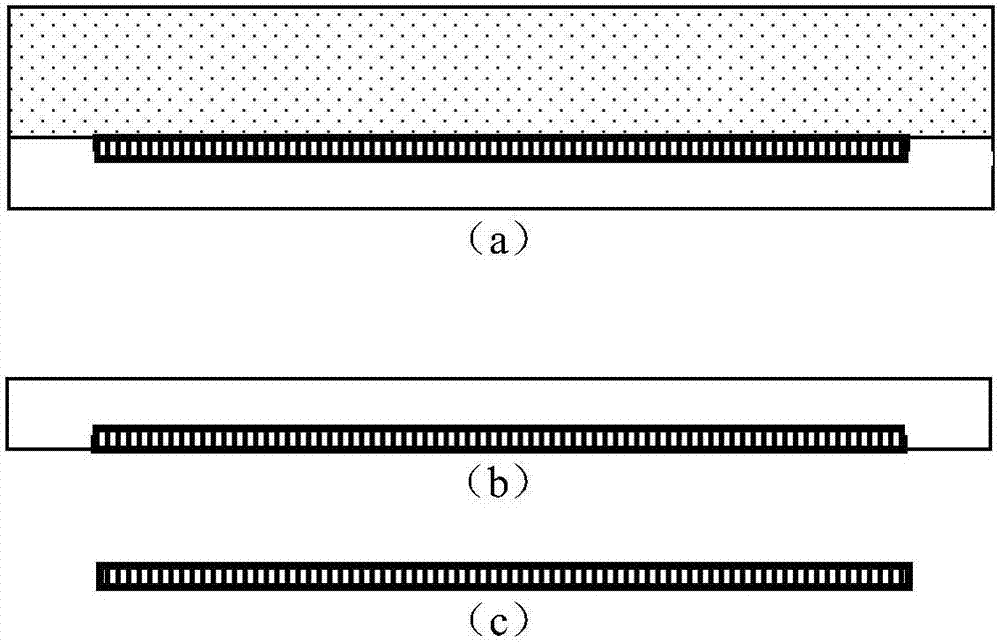

[0036] Such as figure 1As shown, the negative electron compressibility ultra-steep subthreshold slope field effect transistor of this embodiment includes: a substrate 1, a source region 3, a drain region 4, a first conventional gate dielectric layer 5, and a negative electron compressibility NEC gate dielectric layer 7 , a second conventional gate dielectric layer 6, a control gate 8, an isolation layer 9, a gate electrode 10, a source electrode 11 and a drain electrode 12; wherein, a conventional gate dielectric material is deposited on the substrate 1 to form a first conventional gate dielectric layer 5 The negative electron compressibility grid dielectric layer 7 is transferred to the first conventional grid dielectric layer 5, and the negative electron compressibility grid dielectric layer 7 adopts a negative electron compressibility m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com