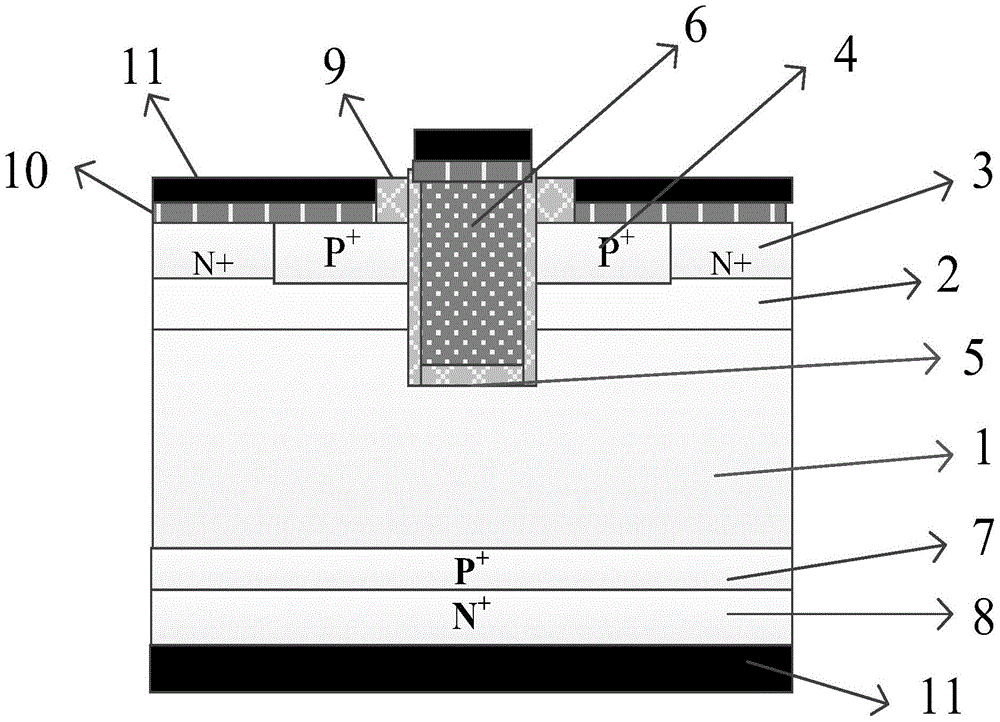

Preparation method of trench gate silicon carbide insulated gate bipolar transistor

A bipolar transistor and trench gate technology, applied in the field of microelectronics, can solve the problems of high manufacturing cost and difficult process, and achieve the effects of saving resources and energy, reducing manufacturing difficulty, and saving manufacturing cost and time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0027] Example 1: Dislocations in the base plane are 10 4 / cm -3 , the substrate concentration is 3×10 14 cm -3 Trench-gate silicon carbide insulated gate bipolar transistors were fabricated on P-type SiC substrates with zero micropipe structure.

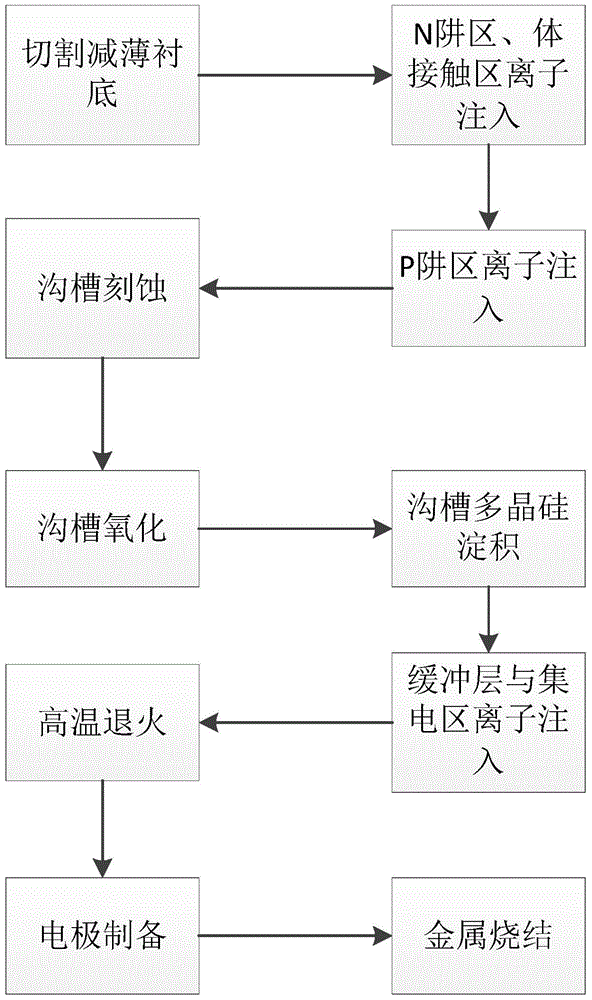

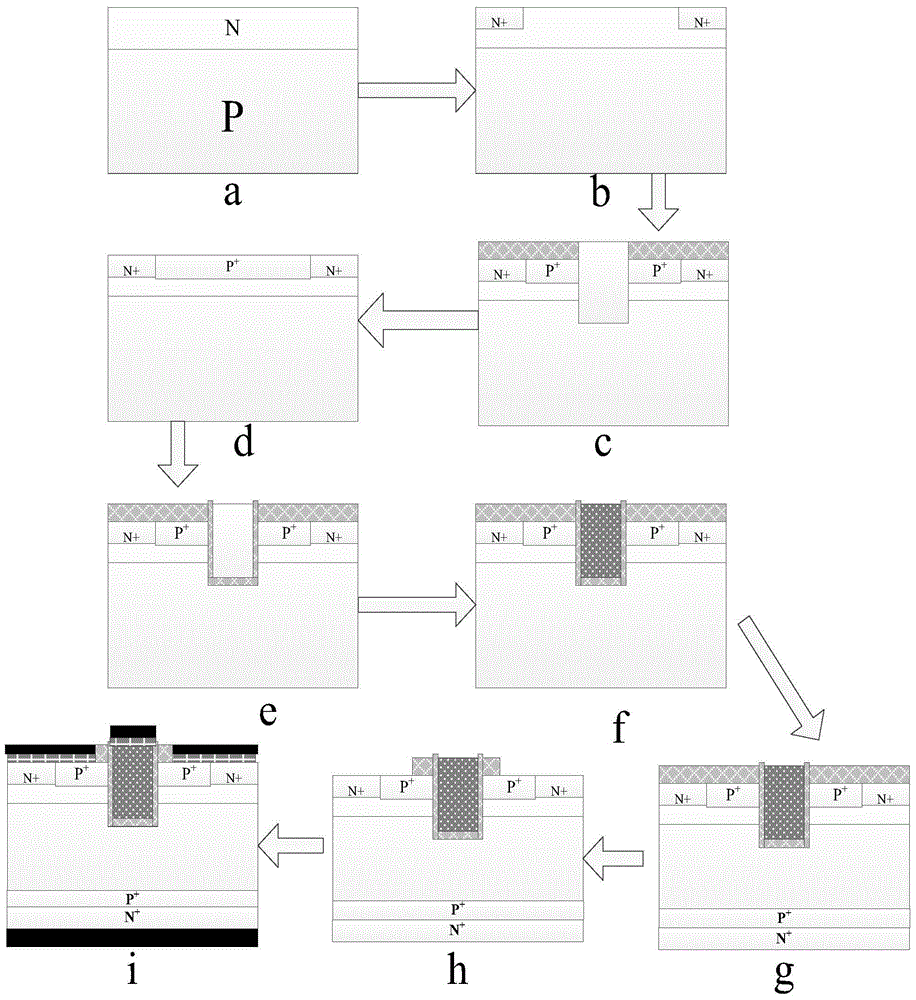

[0028] refer to figure 2 and image 3 , the implementation steps of this embodiment are as follows:

[0029] Step 1: Substrate processing.

[0030] The basal plane dislocation is chosen to be 10 4 / cm -3 , the substrate concentration is 3×10 14 cm -3 The P-type SiC substrate with zero micropipe structure is cut along the back surface of the P-type SiC substrate 1 to make it thinner to 100 μm; after polishing the cut surface, it is oxidized with wet oxygen at 950° C. for 20 minutes, and then the oxide layer is removed. Restore the cut surface structure and flatness.

[0031] Step 2: N well ion implantation.

[0032] (2.1) Deposit a layer of SiO with a thickness of 0.1 μm on the front side of the P-type SiC substrate afte...

Embodiment 2

[0059] Example 2: Dislocations in the base plane are 10 4 / cm -3 , the substrate concentration is 6×10 14 cm -3 Trench-gate silicon carbide insulated gate bipolar transistors were prepared on a micropipe-free P-type SiC substrate.

[0060] refer to figure 2 and image 3 , the implementation steps of this embodiment are as follows:

[0061] Step A: Substrate treatment.

[0062] This step is the same as Step 1 of Example 1.

[0063] Step B: N well ion implantation.

[0064] (b1) This step is the same as the step (2.1) of Example 1;

[0065] (b2) Perform two ion implantations on the window of the N well implantation region: at 650°C, first use 500Kev implantation energy, 4.5×10 12 cm -2 Implantation dose of nitrogen ion implantation, and then use the implantation energy of 350Kev, 1 × 10 12 cm -2 Implantation dose of the second nitrogen ion implantation, forming the N well region 2, such as image 3 Middle a.

[0066] Step C: Apply glue on the front side of the P-t...

Embodiment 3

[0081] Example 3: Dislocations in the base plane are 10 4 / cm -3 , the substrate concentration is 8×10 14 cm -3 Trench gate silicon carbide insulated gate bipolar transistors were prepared on the micropipe-free P-type SiC substrate.

[0082] refer to figure 2 and image 3 , the implementation steps of this embodiment are as follows:

[0083] The first step: substrate processing.

[0084] This step is the same as Step 1 of Example 1.

[0085] Step 2: Deposit a layer of Al with a thickness of 1.2 μm on the front of the above-treated P-type SiC substrate by low-pressure chemical vapor deposition as a barrier layer for nitrogen ion implantation, and coat the N well implantation area by photolithography Window: Perform two ion implantations on the window of the N well region at 650°C, that is, first use 700Kev implantation energy, 7.5×10 12 cm -2 Implantation dose of nitrogen ion implantation is performed once, and then with implantation energy of 450Kev, 4×10 12 cm -2 Im...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com