Full back side contact crystalline silicon cell and preparation method thereof

A back-contact, crystalline silicon cell technology, applied in circuits, photovoltaic power generation, electrical components, etc., can solve the problems of inability to take into account the movement of electrons and holes, increase the complexity of the process, and reduce the recombination of the battery body and the optical loss. , the effect of uniform doping energy and doping depth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

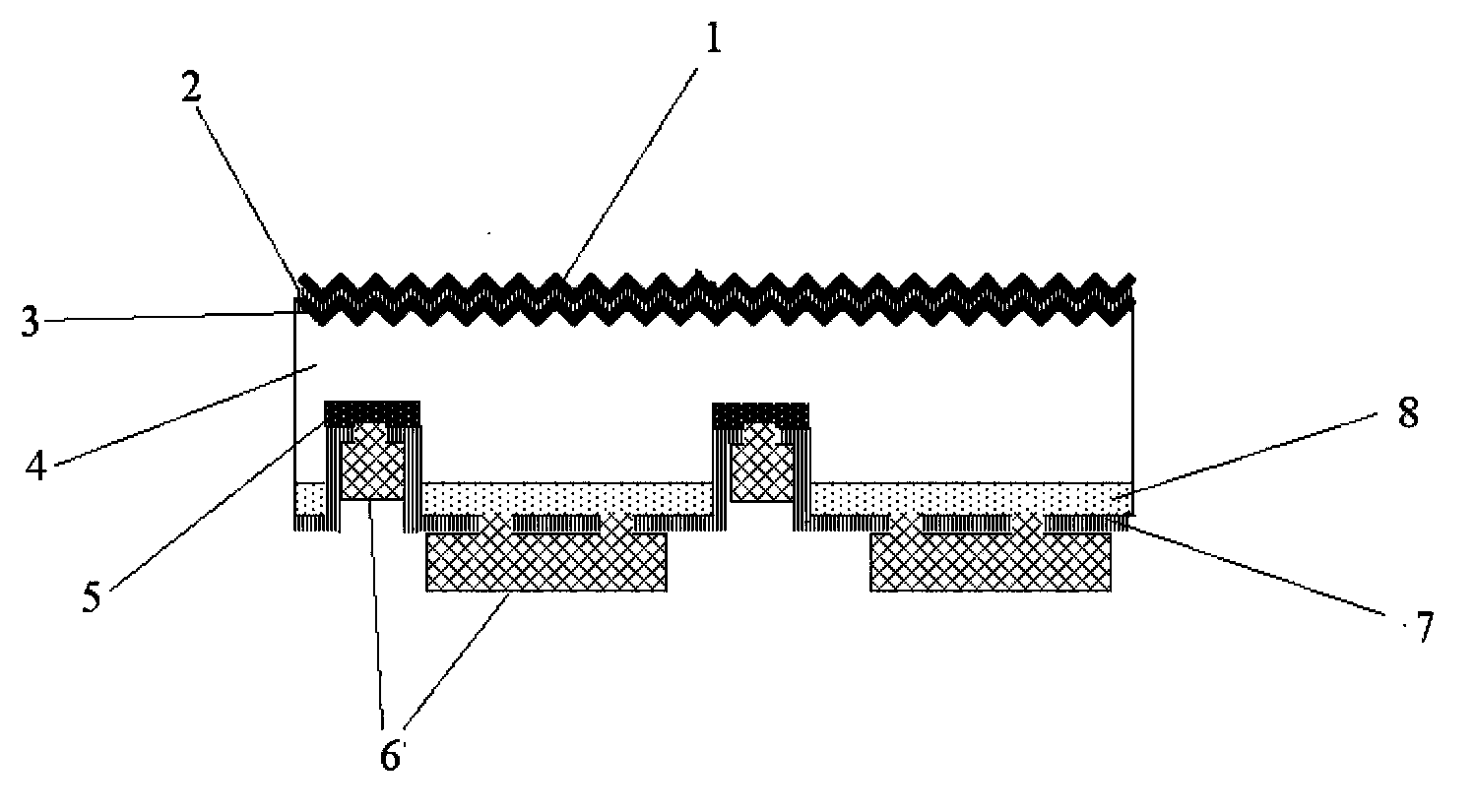

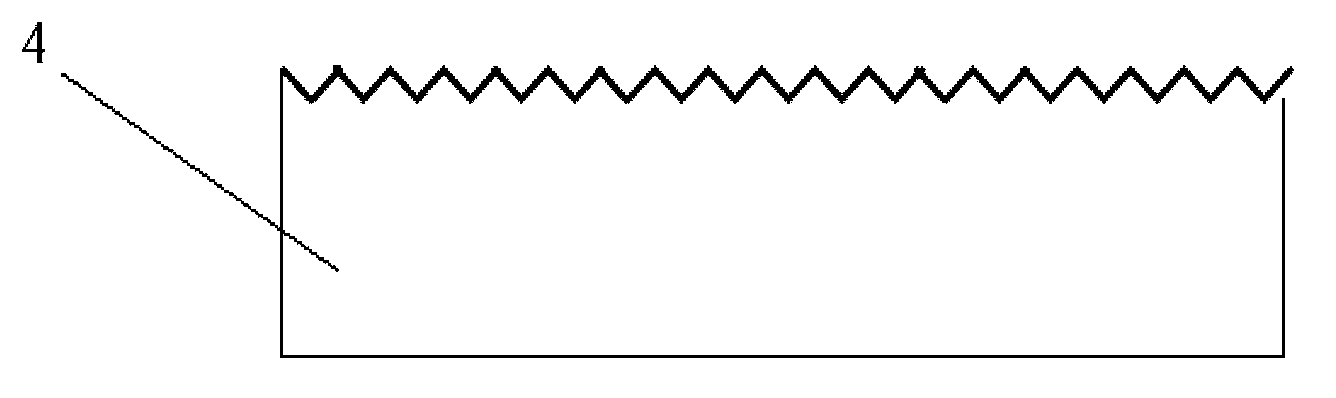

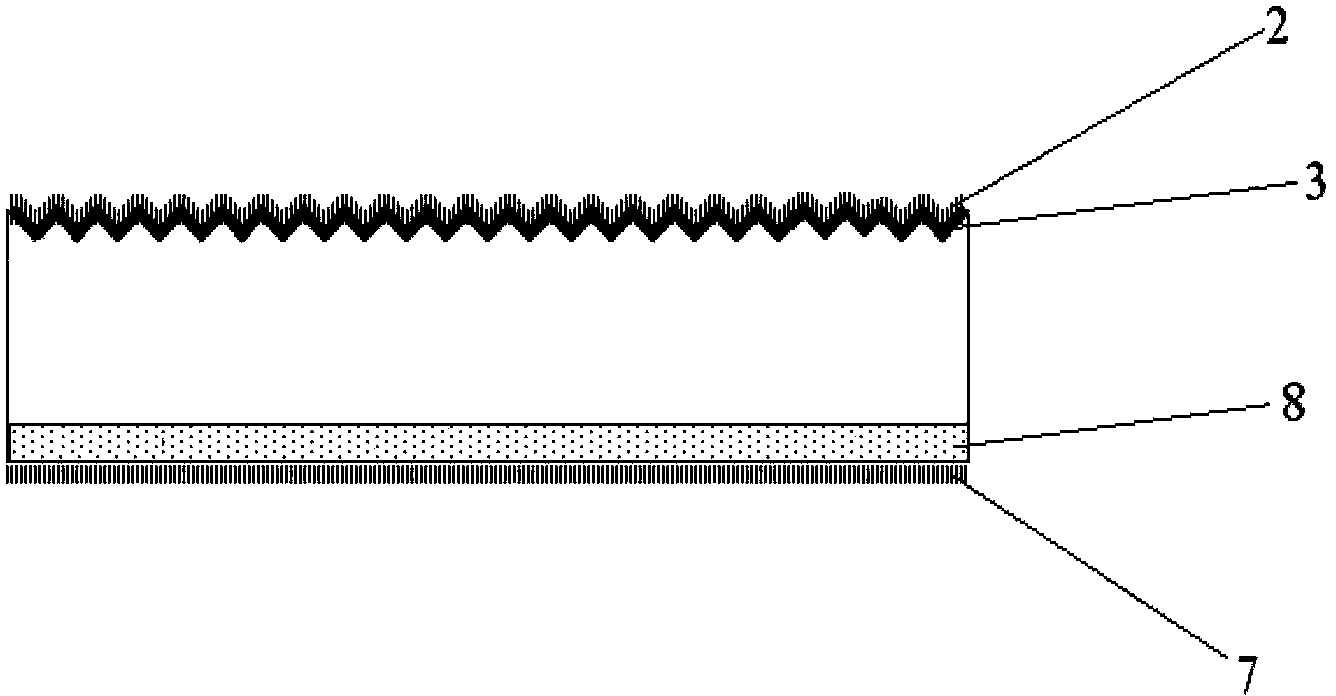

[0036] A full back contact crystalline silicon cell, such as figure 1 As shown, the battery includes: an n-type silicon substrate 4 with a thickness of 200 μm, a minority carrier lifetime of 1000 microseconds, and a resistance of 50 ohm / square. The reverse layer 1, the front oxide layer 2, the front surface electric field FSF3 formed by the lightly doped region on the front surface, and the silicon substrate 4. On the back side, there are P+ emitters 8 formed by non-patterned heavily doped regions, patterned grooves, and n+ bases 5 formed by patterned heavily doped regions at the bottom of the grooves. There is a rear oxide layer 7 on the back, and there are openings in the oxide layer in the regions of the emitter 8 and the base 5, and metal grid lines 6 are formed in the opening regions of the emitter 8 and the base 5 to connect, and the metal connections of different poles are insulated disconnect.

[0037] For the preparation method of full back contact crystalline silic...

Embodiment 2

[0046] A full back contact crystalline silicon cell, such as figure 1 As shown, the battery includes: an n-type silicon wafer substrate 4 with a thickness of 160 μm, a minority carrier lifetime of 1000 microseconds, a resistance of 20 ohm / square, and a pyramid texture structure on the front light-receiving surface, which is covered with a light-receiving surface from top to bottom. The reverse layer 1, the front passivation layer 2, the n+ type front surface electric field FSF3 formed by the lightly doped region on the front surface, and the silicon substrate 4. On the back side, there are P+ emitters 8 formed by non-patterned heavily doped regions, patterned grooves, and n+ bases 5 formed by patterned heavily doped regions at the bottom of the grooves. There is a back passivation layer 7 on the back, and there are openings in the passivation layer in the region of the emitter 8 and the base 5, and metal grid lines 6 are formed in the opening regions of the emitter 8 and the b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com