Back process method of IGBT (insulated gate bipolar transistor) device

A backside process and device technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of shallow junction, no obvious improvement, and low activation rate of the surface layer, and achieve high activation efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

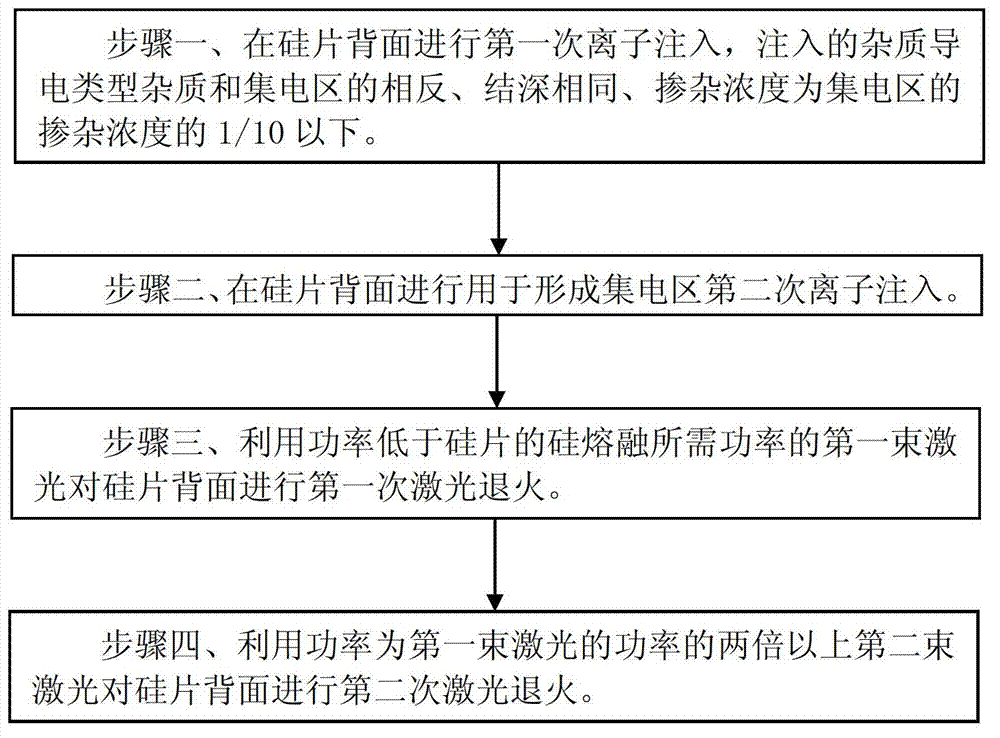

[0033] Such as figure 2 As shown, it is a flow chart of the method of the embodiment of the present invention; the backside process method of the IGBT device of the embodiment of the present invention adopts the following steps to form the collector region with P-type doping of the IGBT device:

[0034] Step 1. Perform the first ion implantation on the back of the silicon wafer. The impurities of the first ion implantation are N-type impurities. The implantation depth of the first ion implantation and the subsequent formation of the second ion implantation of the collector region The implantation depths are the same, and the doping concentration of the N-type impurity in the first ion implantation is less than 1 / 10 of the doping concentration of the P-type impurity in the collector region. The implantation energy of the first ion implantation is 1kev-50kev, and the implantation dose is 1e12 atoms / cm 2 ~1e14 atoms / cm 2 1. The impurity implanted is phosphorus or arsenic, and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com