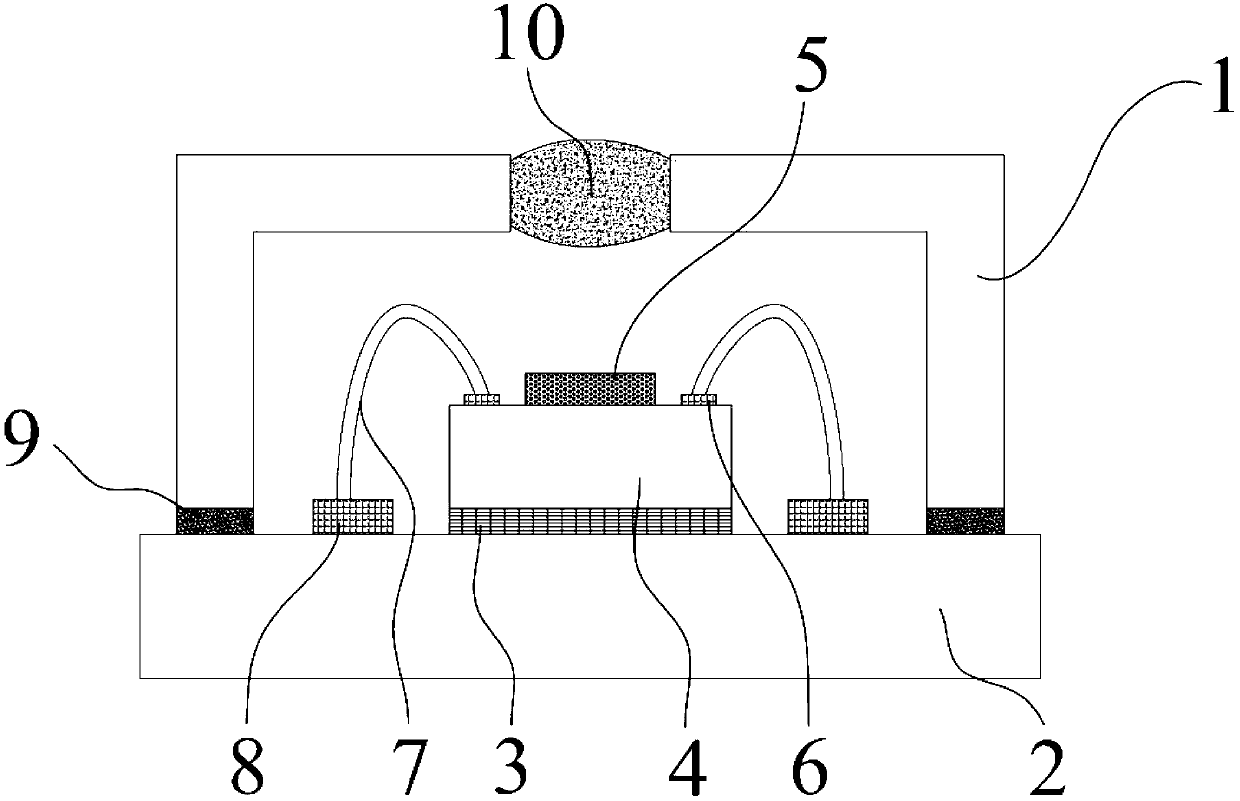

Packaging structure and manufacture method for complementary metal-oxide-semiconductor transistor (CMOS) image sensors

An image sensor and packaging structure technology, applied in radiation control devices and other directions, can solve the problems of delamination of glass and silicon substrate, inability to use cost wafer-level processing and surface mounting technology, etc., to improve product reliability and production Efficiency, warpage improvement, cost reduction effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

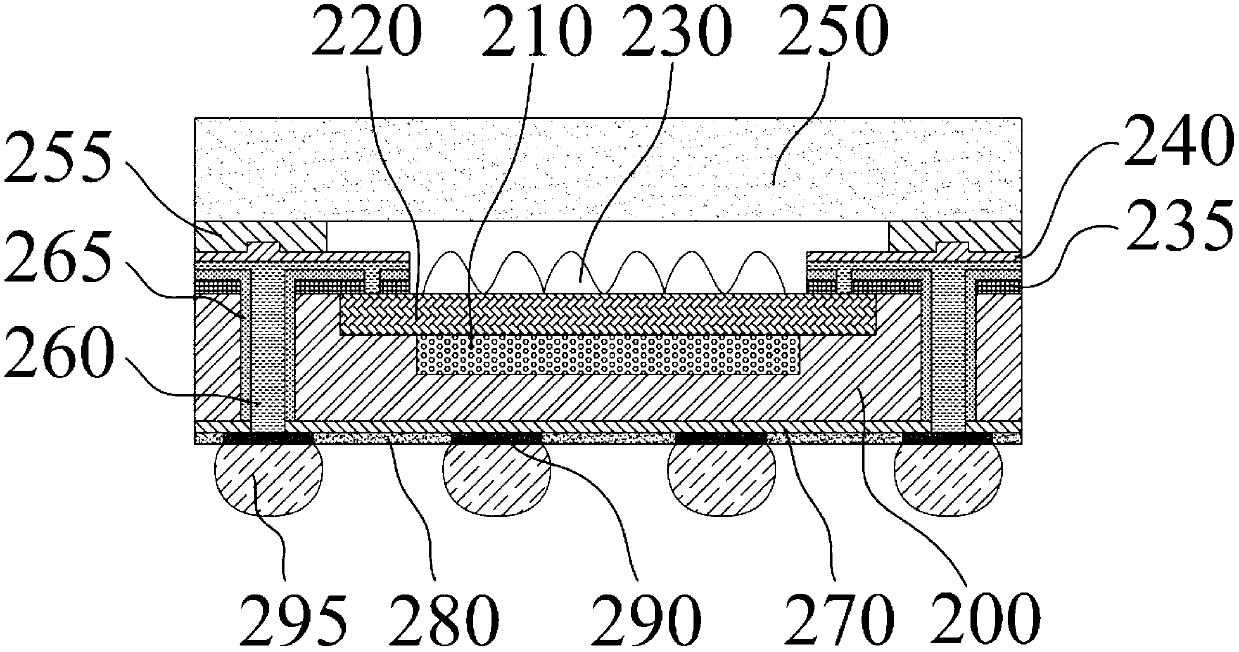

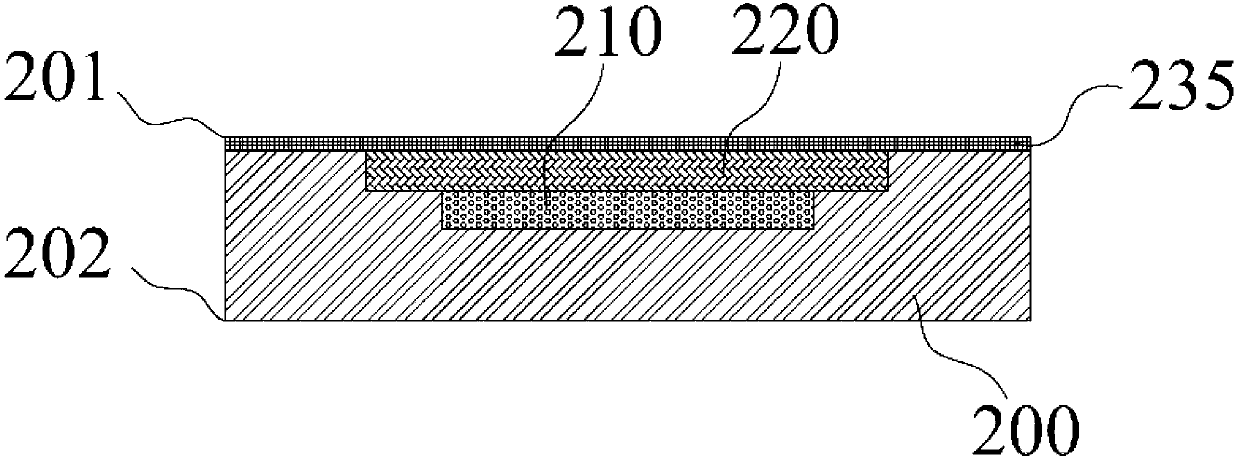

[0038] The present invention enhances the bonding force between the glass sheet 250 and the silicon substrate 200 by making a stepped protrusion or groove structure on the first surface 201 of the silicon substrate 200, and improves the delamination problem between the glass and the silicon substrate , which improves the reliability of the package and is suitable for CMOS image sensor (CIS) packages with larger chip sizes. figure 2 It is a schematic diagram of a CIS package of a stepped protrusion structure fabricated on the first surface 201 of the silicon substrate 200 according to an embodiment of the present invention.

[0039] by figure 2 As shown, the CMOS image sensor (CIS) according to the embodiment of the present invention includes: a silicon substrate 200, and the front side of the silicon substrate 200 is a first surface 201 formed with a microlens 230, a metal interconnection layer 220 and an optical interaction region 210 , the back surface of the silicon subs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com