Processing method of double-mask heavy boron-doped silicon on insulator (SOI) micro electro mechanical system (MEMS)

A processing method and double-mask technology, which are applied in metal material coating process, process for producing decorative surface effects, decorative arts, etc. The effect of small footing effect, uniform thickness and precise thickness control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

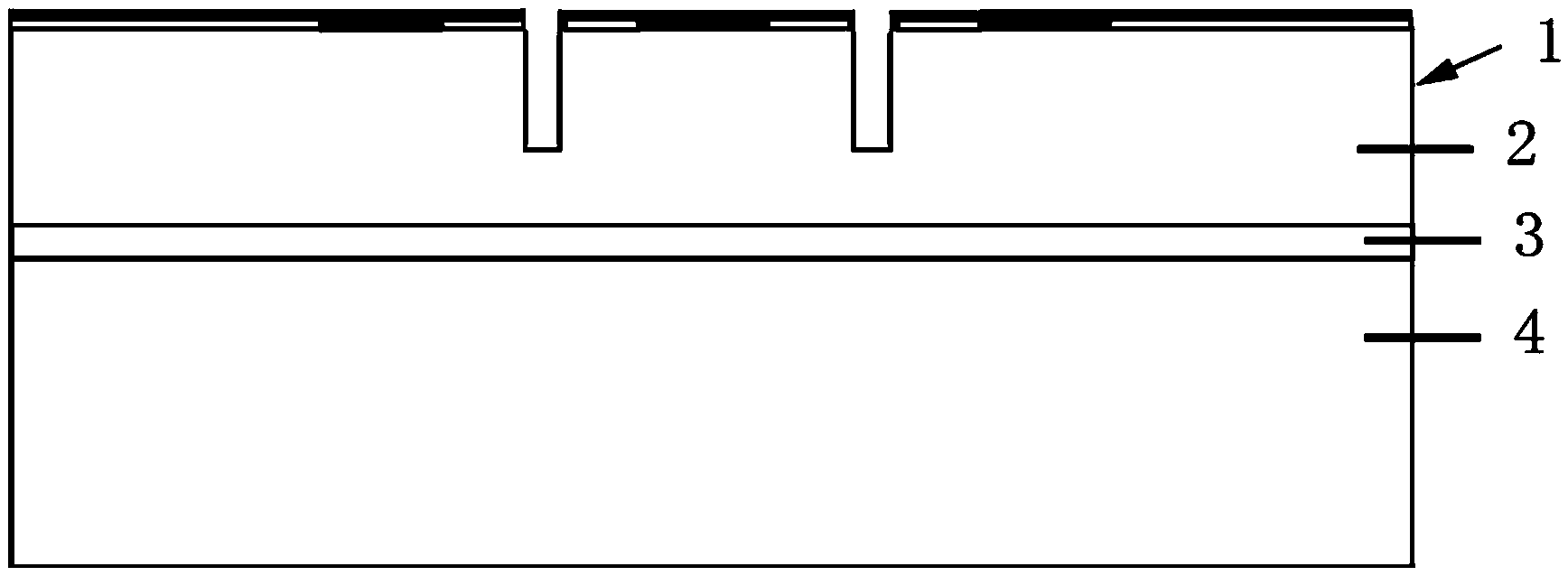

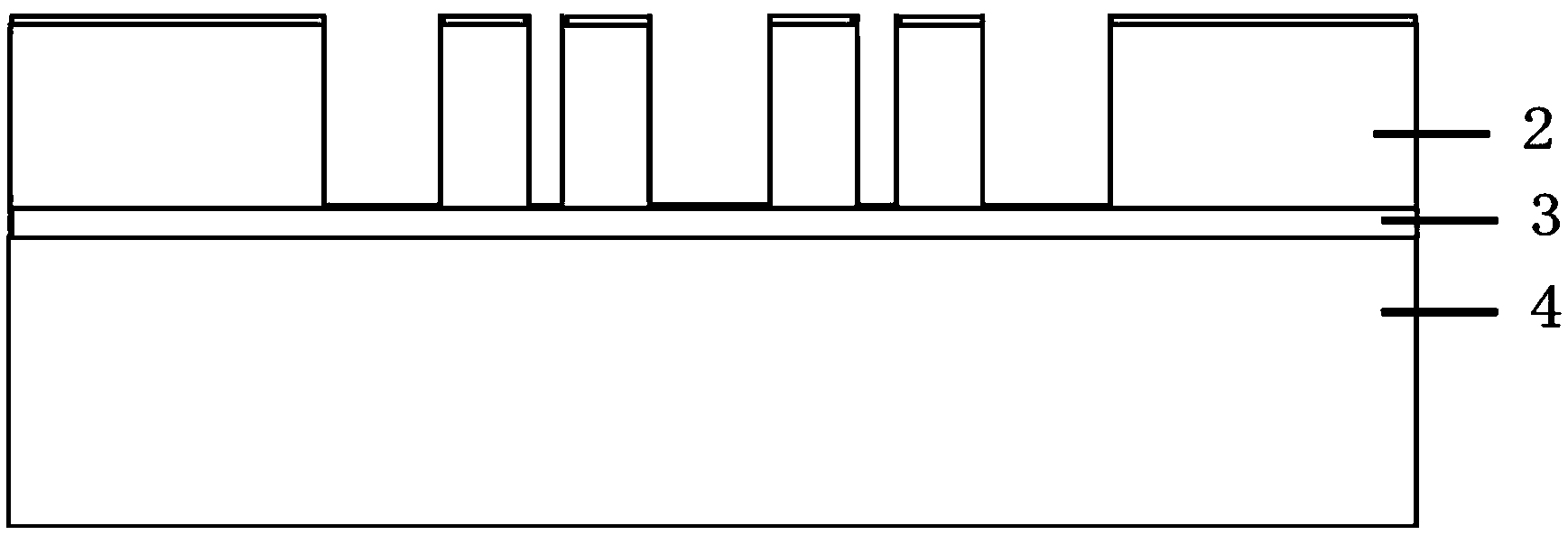

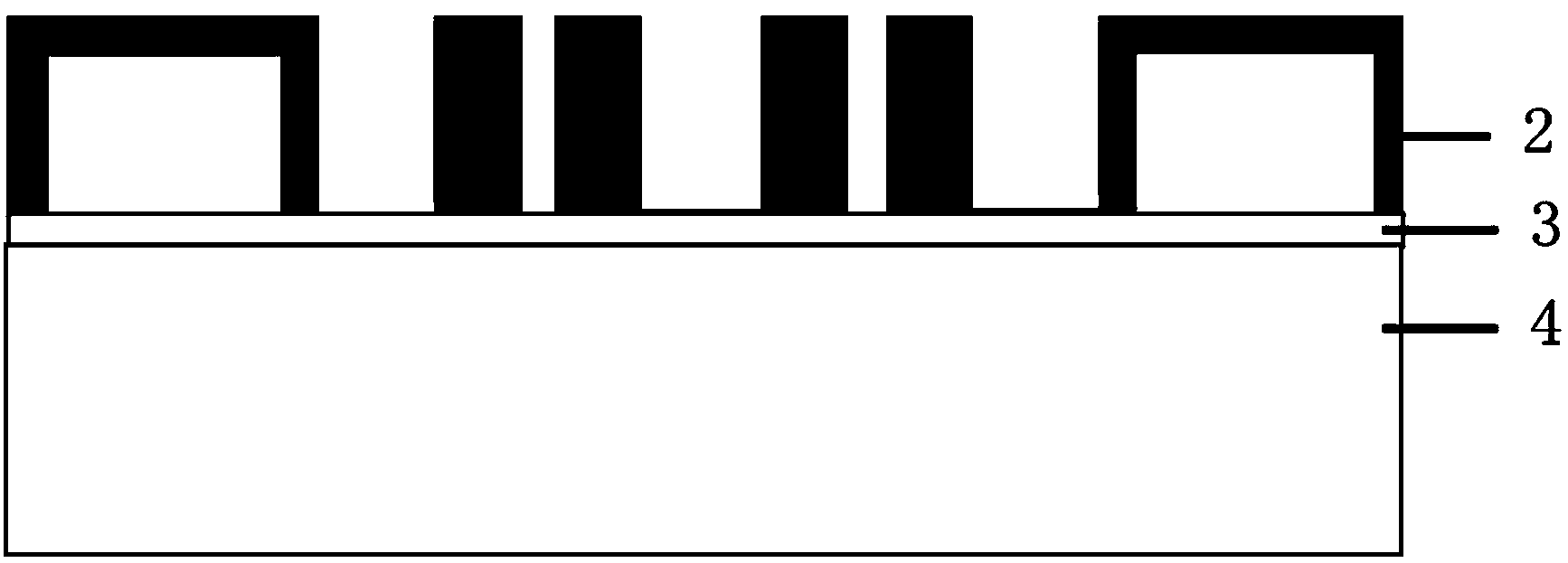

[0016] Figure 1-Figure 5 It is a schematic diagram of the processing flow of the double-mask boron-doped SOI MEMS processing method. The processing method of the present invention uses one piece of SOI wafer to manufacture MEMS devices, adopts double mask and concentrated boron doping technology, can effectively reduce the Footing effect at the bottom of the silicon structure layer 2 and reduce the weight and mass on the silicon structure layer 2 Parasitic capacitance between other structures and the silicon substrate layer 4 .

[0017] exist figure 1 Among them, the SOI wafer 1 includes a layer of silicon dioxide (SiO2) layer 3 between the silicon structure layer 2 and the silicon substrate layer 4, and the processing method is realized through the following process steps:

[0018] (1) Sputter a layer of aluminum on the front of the silicon wafer, photolithography, etch the aluminum, and define a complete MEMS structure pattern on the silicon wafer;

[0019] (2) Use lith...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com