Method for manufacturing split gate flash by reducing writing interference

A fabrication method and separation gate technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as easy generation of tunneling current, separation gate flash memory write interference, etc., to avoid write interference, reduce Tunneling current, effect of preventing write variation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

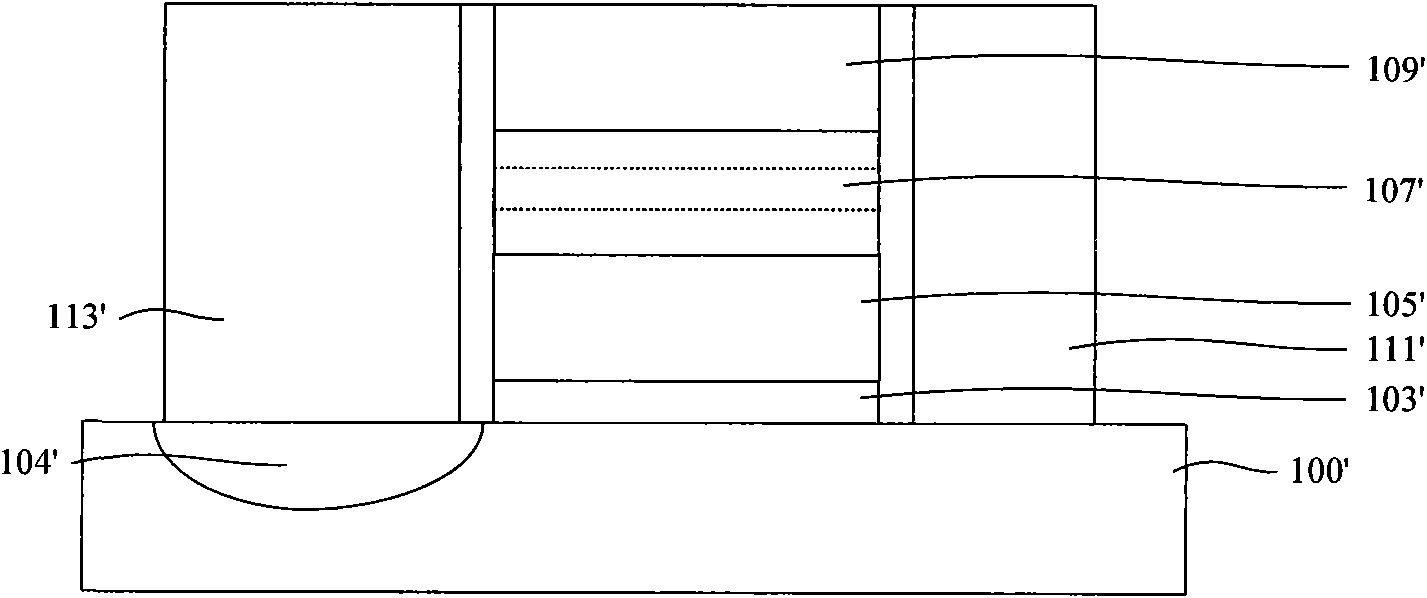

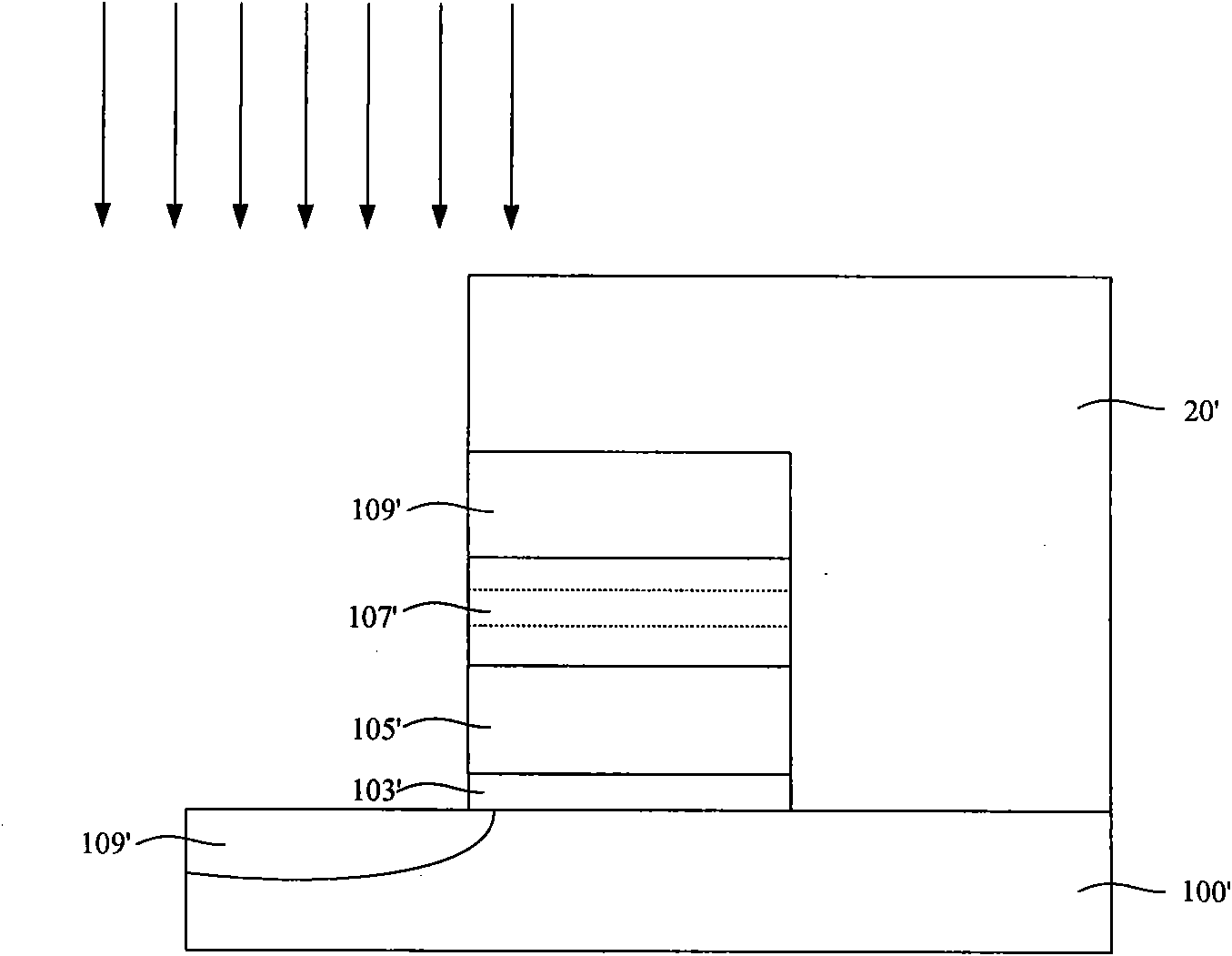

[0031] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be further described below in conjunction with the accompanying drawings.

[0032] In the following description, specific details are set forth in order to provide a thorough understanding of the present invention. Of course, the present invention is not limited to this specific embodiment, and general replacements known to those skilled in the art are also covered within the protection scope of the present invention. Accordingly, the present invention is not limited to the specific examples disclosed below.

[0033] Next, the above and other objects, features and advantages of the present invention will be more apparent through a more specific description of preferred embodiments of the present invention shown in the accompanying drawings. Like reference numerals designate like parts throughout the drawings. The drawings are not intended t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com