Preparation for SiGe HBT transistor

A transistor and polysilicon layer technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as the deterioration of the cut-off frequency of the device performance, and achieve the effect of reducing the composite current of the base region, optimizing the effect, and achieving a good effect.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

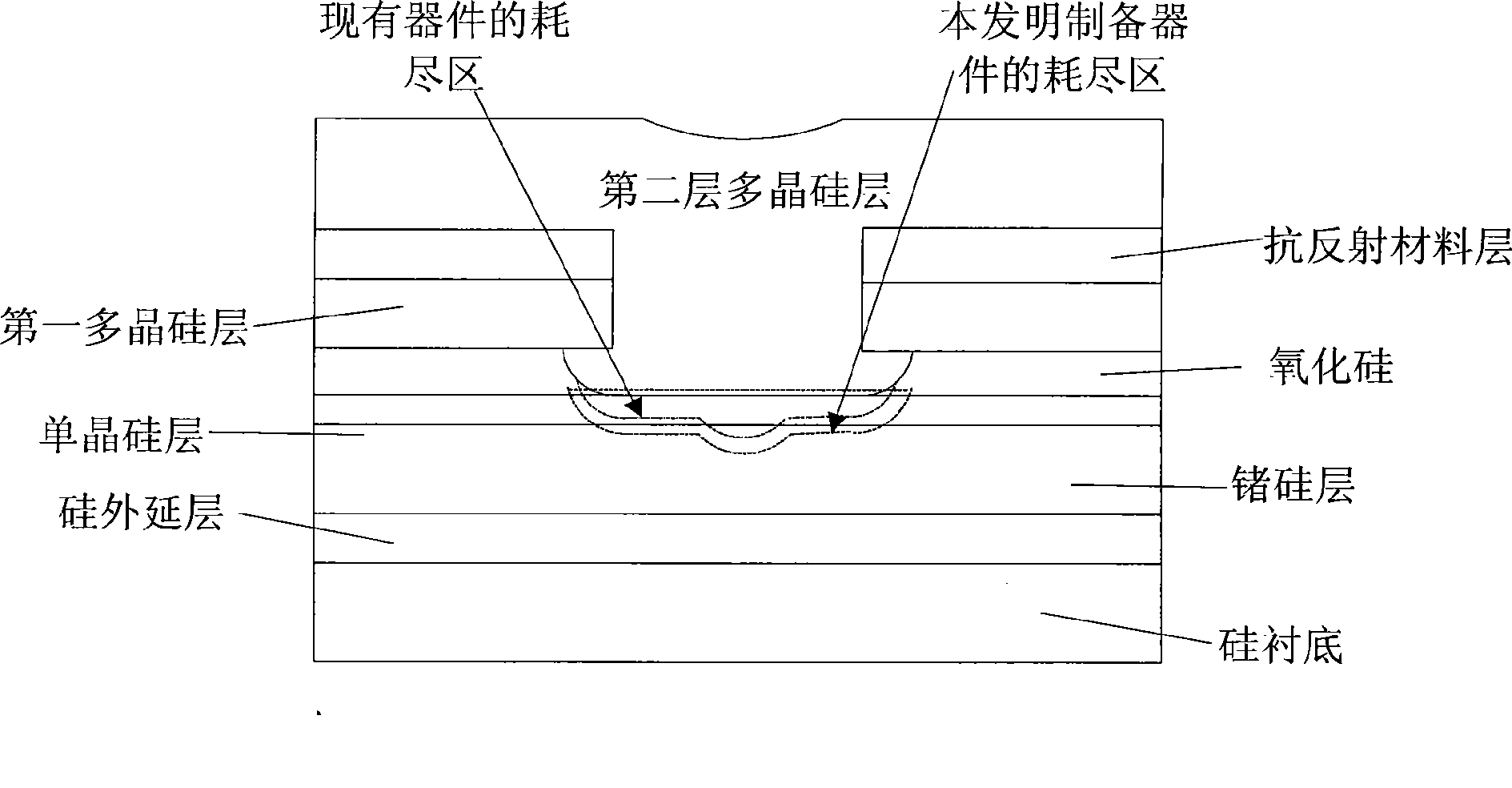

[0013] figure 1 It is a partial cross-sectional schematic diagram of the SiGe HBT transistor structure. The SiGe HBT transistor consists of an emitter polysilicon, an interface oxide layer between polysilicon and monocrystalline silicon, an emitter monocrystalline silicon (also called a capping layer), a silicon germanium base, and a collector. not shown). The silicon germanium base includes: the base layer of silicon (i.e., the silicon epitaxial layer), which is mainly used for the buffering of the silicon substrate to reduce defects; the silicon germanium core layer is used as the base area, wherein the silicon germanium core layer includes the germanium concentration rapid rise region, There are three parts, the platform area and the step-down area. The emitter single crystal silicon located on the contact surface between the base and the emitter is used for doping impurity arsenic ions in the polycrystalline silicon to diffuse to the single crystal silicon to form a singl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com