A Method of On-Chip Interconnection Based on Crossbar Structure

A crossbar and bus technology, applied in the computing field, can solve problems such as limiting the communication bandwidth between processing elements and shared resources, not being able to obtain authorized processing elements, and affecting the processing rate of system packets, so as to alleviate access contention, ensure parallel execution, The effect of improving the data throughput rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

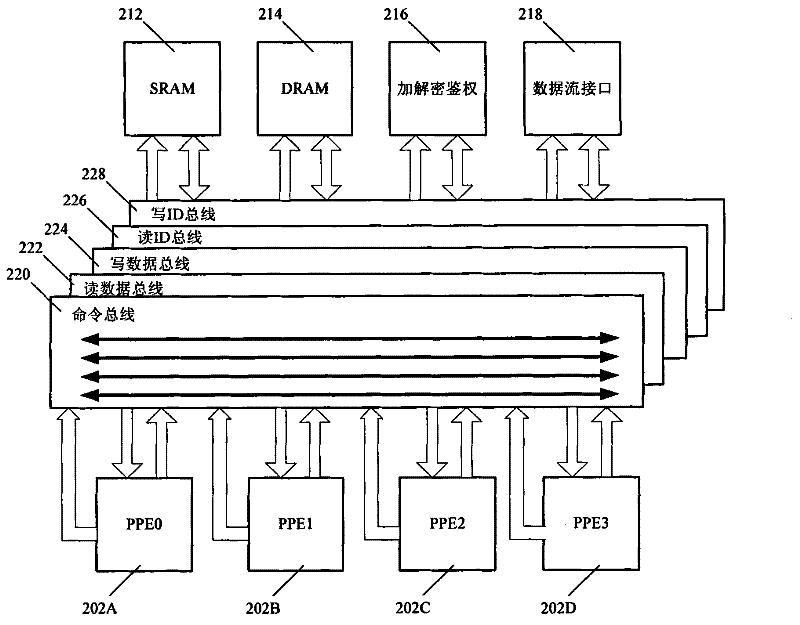

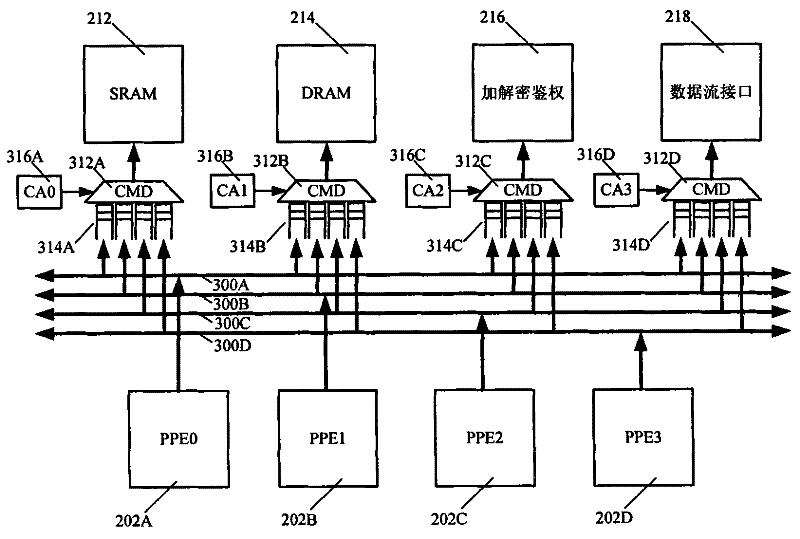

[0030] refer to figure 2 An embodiment of the network processor architecture is shown. In this architecture, four packet processing units 202A, 202B, 202C, 202D are included. It should be noted that the present invention is not limited thereto. For example, other embodiments include (but not limited to) six or eight packet processing units; the packet processing units can perform the same or different functions according to the requirements of the system designer. As the core component of network processor packet processing, the packet processing unit frequently exchanges data with other data processing units in the system. The packet processing unit initiates a transaction as the master control end and accesses the target resource.

[0031] as figure 2 As shown, the network processor of this embodiment also includes a variety of typical shared resources. In sequence, the SRAM unit 212 , the DRAM unit 214 , the encryption / decryption authentication unit 216 and the data s...

Embodiment 2

[0052] According to one embodiment, Figure 5 The details of the write bus are shown. The write buses include write data buses 400A, 400B, 400C, and 400D for data transfer, and write ID buses 402A, 402B, 402C, and 402D for transfer of identification information. as Figure 5 As shown, each shared resource is permanently connected to a write ID bus, and each master is coupled to the horizontal write ID bus through an ID multiplexer. The ID multiplexers used to support the crossbar are sequentially 412A, 412B, 412C and 412D. Each multiplexer is controlled by a lightweight write arbiter (WA). The write arbiter monitors the information in the write ID bus and responds to the request for accessing the master. These arbitrators are 422A and 422B in turn. , 422C and 422D.

[0053] exist Figure 5 In the illustrated embodiment, the writing of data is completed through the transmission of the write data bus, and each master control terminal, as a provider of data, is fixedly conne...

Embodiment 3

[0068] According to one embodiment, Figure 7 Shows the details of the read bus. The read buses include read data buses 500A, 500B, 500C, and 500D for data transfer, and read ID buses 502A, 502B, 502C, and 502D for transferring identification information. and Figure 5 The write ID bus is shown similarly, with each shared resource permanently connected to a read ID bus. The difference is that in the read data bus, each shared resource is fixedly connected to a read data bus, and the master control terminal is coupled to the read data bus through a data multiplexer. The read data multiplexers for supporting the crossbar include 512A, 512B, 512C, 512D. Another difference from the write bus is that in order to solve the problem of access competition caused by multiple shared resources returning data to the same master at the same time node, this embodiment also provides a node cache on each crossbar node , that is, a set of data buffer FIFOs is provided for each multiplexer, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com