Semiconductor package for printing bonding material on lead frame and wafer and manufacturing method thereof

A lead frame and bonding material technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of chip cracks, small chip size, high stress, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

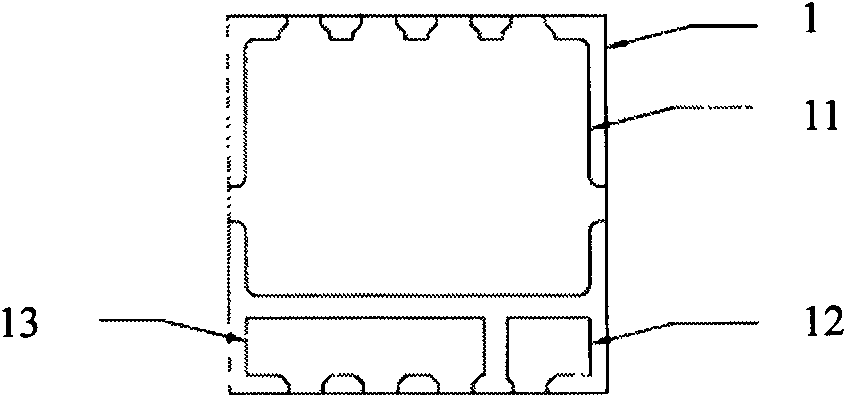

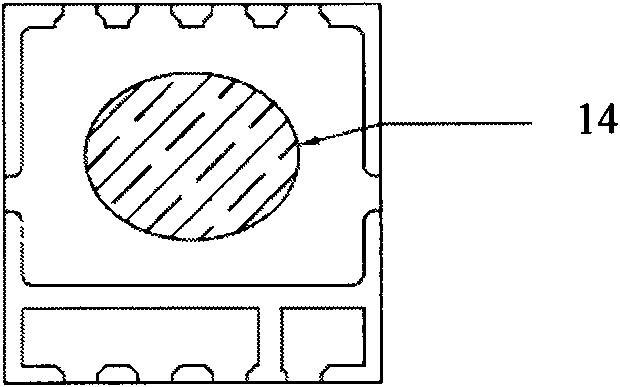

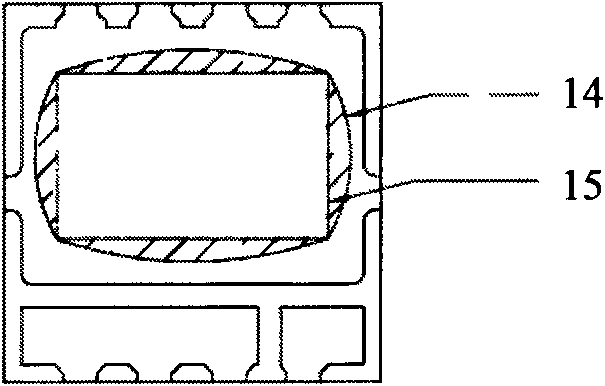

[0100] Such as Figure 2E As shown, it is a schematic structural diagram of a semiconductor package for printing adhesive materials on a lead frame provided in this embodiment, which includes: a chip stage 21 and pins 21' electrically connected to the chip stage 21 , and a lead frame 2 with two pins 22 and 23 electrically isolated from the stage 21 (such as Figure 2A shown); and a MOSFET 25 having a top gate and a top source (not shown) on its upper surface and a bottom drain (not shown) on its back. The bottom drain of the MOSFET 25 is bonded to the wafer stage 21 , and the top gate and top source of the MOSFET 25 are bonded to pins 22 and 23 respectively through several metal leads 26 . Wherein, the printing adhesive material 24 formed by printing (such as Figure 2B shown), and the printed bonding material 24 and the MOSFET 25 have the same size and shape, by Figure 2C It can be seen that the MOSFET 25 completely covers the printed adhesive material 24 . The adhesive ...

Embodiment 2

[0103] Such as Figure 3A-3E As shown, there is provided another specific embodiment of the semiconductor package in which the adhesive material is printed on the lead frame of the present invention. its with Figure 2A-2E The illustrated embodiment is similar, and the only difference is that the printed bonding material 34 formed in this embodiment and the chip stage 31 on the lead frame 3 have the same size and shape (such as Figure 3B shown), by Figure 3C It can be seen that when the MOSFET 35 is pasted on the printed adhesive material 34 , a part of the surrounding area of the slide table 31 where the adhesive material 34 is printed is still exposed. Afterwards, it is the same as the process described in Example 1, as Figure 3D As shown, a number of metal leads 36 are respectively connected to the front electrode of MOSFET 35 and pins 32 and 33 by wire bonding technology to form connection bonds between MOSFET 35 and pins 32 and 33 . Such as Figure 3E As shown, ...

Embodiment 3

[0105] Such as Figures 4A-4E As shown, there is provided another specific embodiment of the semiconductor package in which the adhesive material is printed on the lead frame of the present invention. its with Figure 2A-2E and the embodiments shown in 3A to 3E are similar, and the only difference is that the printed bonding material 44 formed in this embodiment has the same shape and slightly larger size than the MOSFET 45. Figure 4B and 4C It can be seen that when the MOSFET 45 is pasted on the printed adhesive material 44, there is still a very small area of the printed adhesive material 44 exposed around it. Afterwards, the process described in Example 1 and Example 2 is the same, as Figure 4D As shown, a number of metal leads 46 are respectively connected to the front electrode of MOSFET 45 and pins 42 and 43 by wire bonding technology to form connection bonds between MOSFET 45 and pins 42 and 43 . Such as Figure 4E As shown, the lead frame 4, MOSFET 45 and meta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com