Integrated circuit layout structure and manufacturing method thereof

A layout structure and integrated circuit technology, which is applied to circuits, electrical components, and electrical solid devices, can solve problems such as uneven copper metal thickness of wide and thin lines, improve planarization capabilities, avoid hot spots, and reduce burdens Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

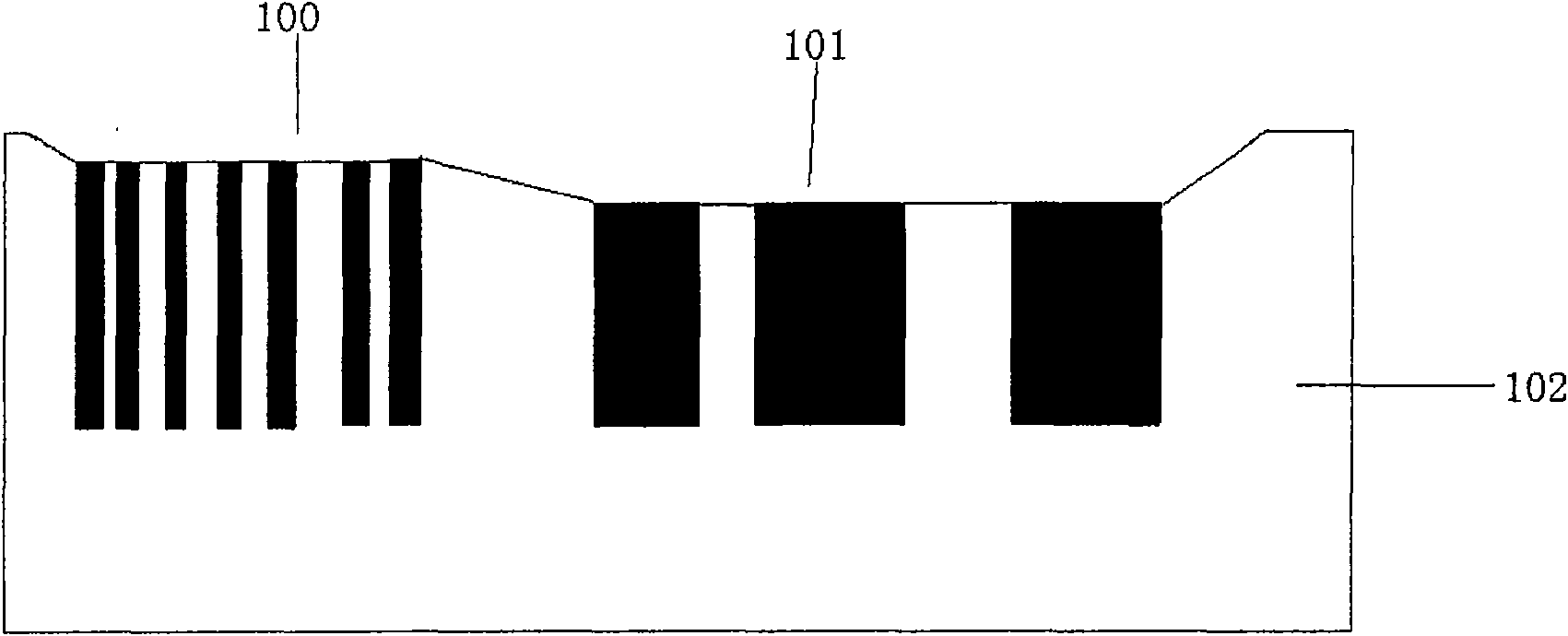

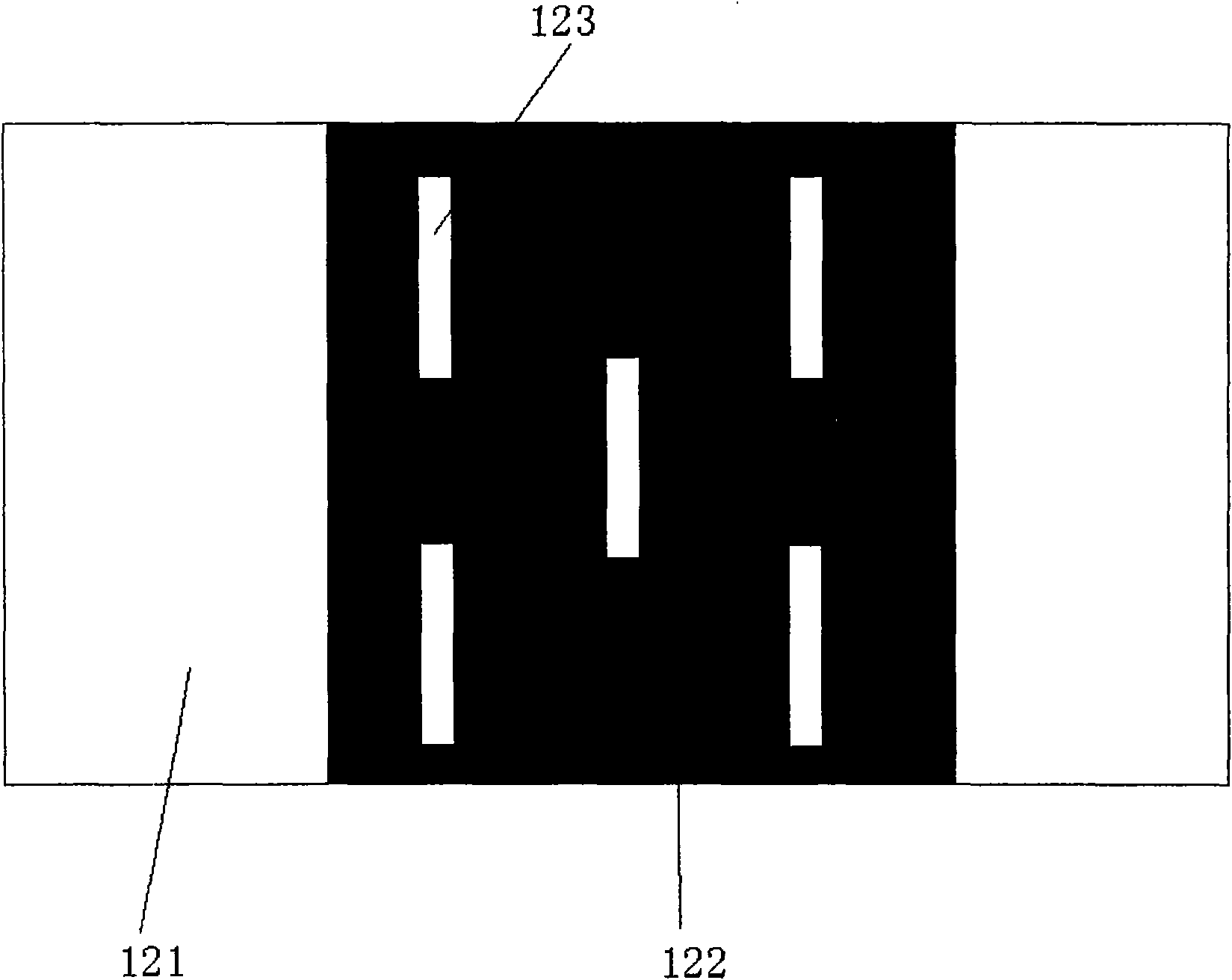

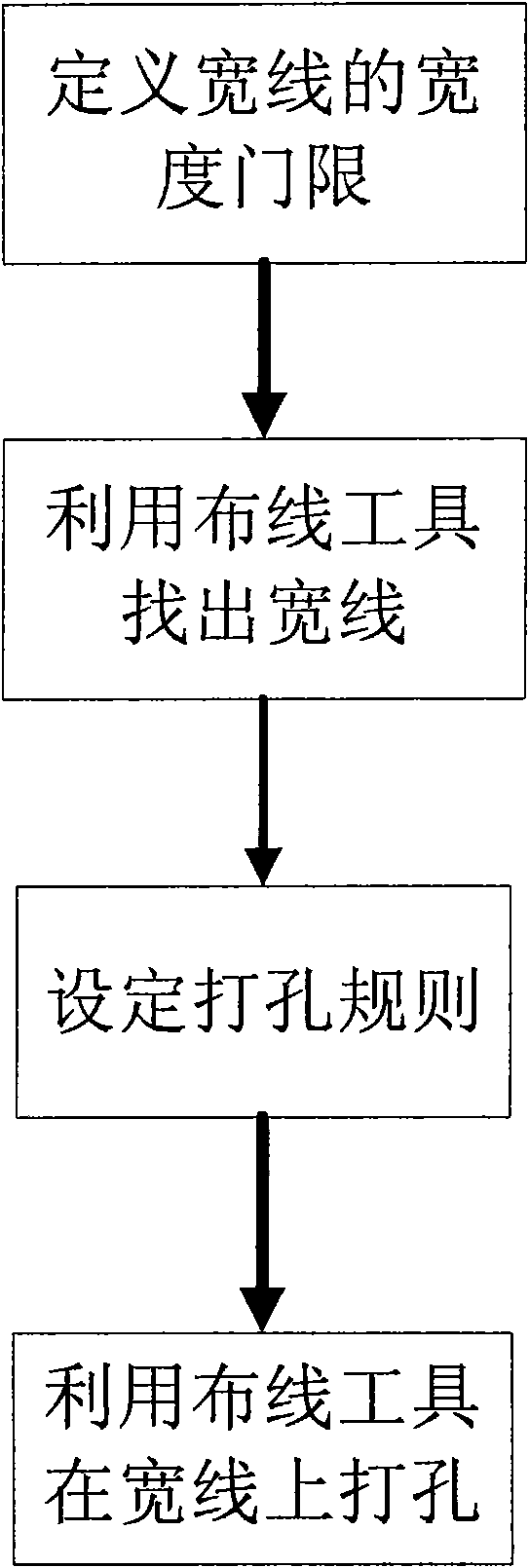

[0029] see figure 2 , figure 2 A top view of an integrated circuit layout structure is proposed for the present invention. The integrated circuit layout structure provided by the present invention includes: a dielectric; a wide copper wire grown in the dielectric, and a wide copper wire is a copper wire with a width greater than a certain threshold; and a wide copper wire grown on the wide copper wire. Evenly distributed small holes are punched. The small holes punched on the wide copper wire shall adopt the minimum wire width and be evenly distributed on the copper wire. The wide line of holes reduces the removal rate of copper in chemical mechanical polishing. This structure makes the growth of copper in wide and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com