Method for manufacturing transistor by using silicon single crystal slices

A transistor and silicon single crystal technology, which is applied in the field of lightly doped/heavily doped structure silicon substrate manufacturing, can solve problems such as crystal defects, difficult operation, and stress, and achieve the effect of reducing defects and improving device performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

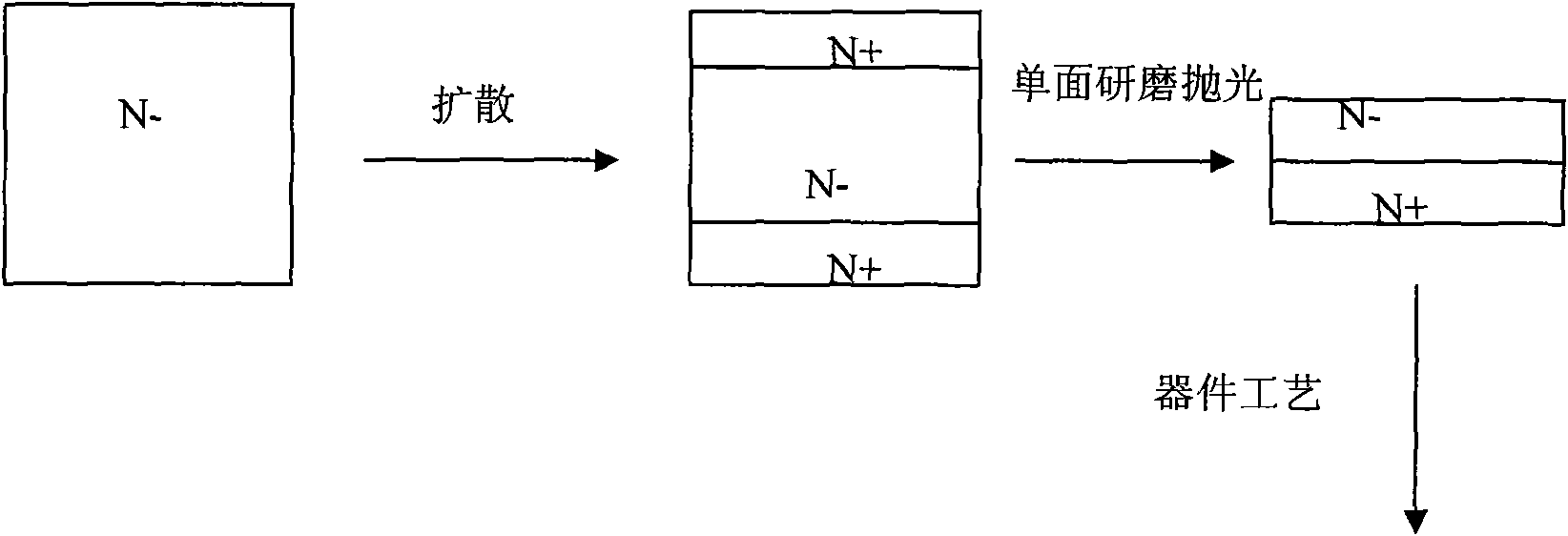

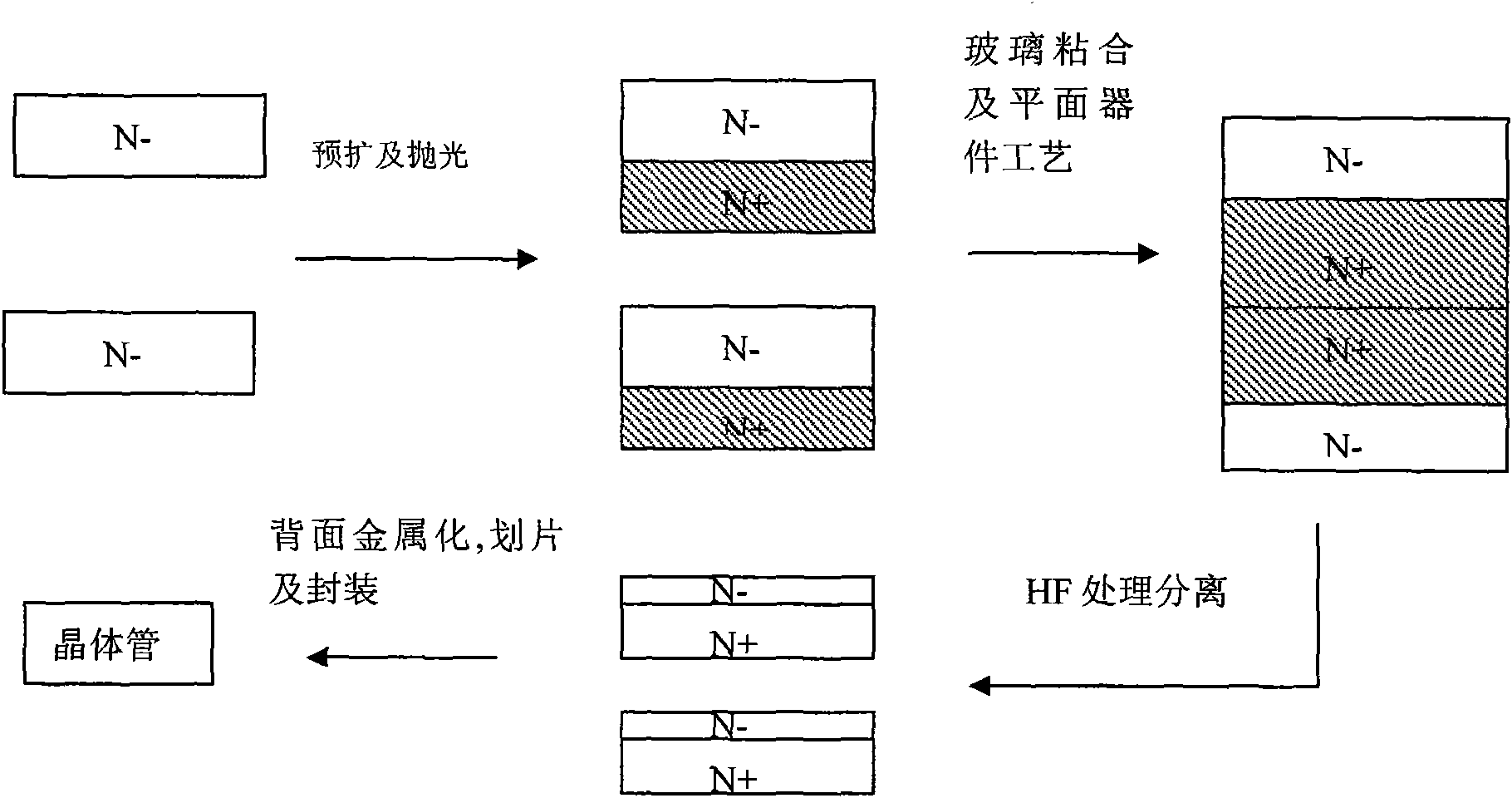

Method used

Image

Examples

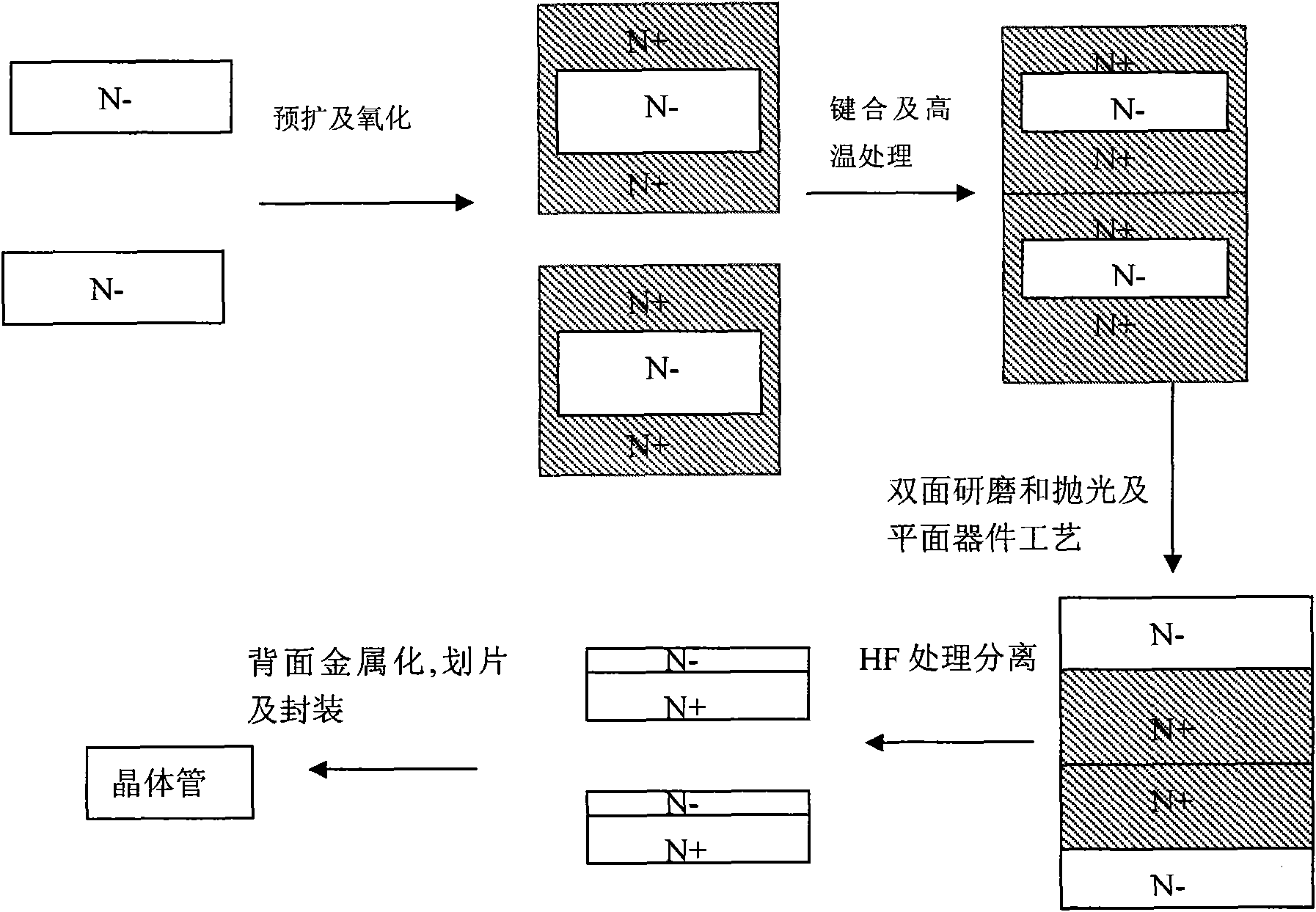

Embodiment 1

[0033] Embodiment 1, image 3 A method for bonding and separating silicon wafers is provided, and the following steps are performed in sequence:

[0034] 1) Choose 2 pieces of single crystal polished silicon wafers, the crystal orientation of the single crystal silicon wafers is , the doping type is N type, the dopant is phosphorus, and the resistivity is 33 ohm.cm to 35 ohm.cm , the front side of the single crystal polished silicon wafer is a polished surface with a surface roughness of 0.5nm, the thickness of the single crystal silicon wafer is 230um, and the diameter is 100mm.

[0035] 2), each silicon wafer is carried out as follows:

[0036] Place the silicon wafer in a high-temperature diffusion furnace, adopt a conventional phosphorus pre-expansion process, and pass a phosphorus source (POCL 3 ), and do impurity (N+) on the surface of the silicon wafer for pre-deposition and diffusion for 4 hours.

[0037] Then adopt the conventional thermal oxidation method, the pro...

Embodiment 2

[0052] Embodiment 2, a method for bonding and separating silicon wafers, the following steps are carried out successively:

[0053] 1) Choose 2 pieces of single crystal polished silicon wafers, the crystal orientation of the single crystal silicon wafers is , the doping type is N type, the dopant is phosphorus, and the resistivity is 33 ohm.cm to 35 ohm.cm , the front side of the single crystal silicon wafer is a polished surface with a surface roughness of 0.5nm, the thickness of the single crystal silicon wafer is 170um, and the diameter is 125mm.

[0054] 2), with embodiment 1.

[0055] 3) Put the above-mentioned polished silicon wafers with an oxide layer that meet the requirements in pairs, and then perform room temperature bonding on the bonding machine. The bonding method adopts the conventional silicon wafer room temperature direct bonding method, and the air in the bonding area is clean The grade is 10, and the bonded silicon wafer group is obtained.

[0056] Then p...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Surface roughness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com