Preparation method for complementary metal oxide semiconductor element with dual metal grid

An oxide semiconductor and double metal gate technology, which is applied in the field of complementary metal oxide semiconductor components, can solve the problems of complex integration technology and process control, and strict requirements for material thickness and composition control.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

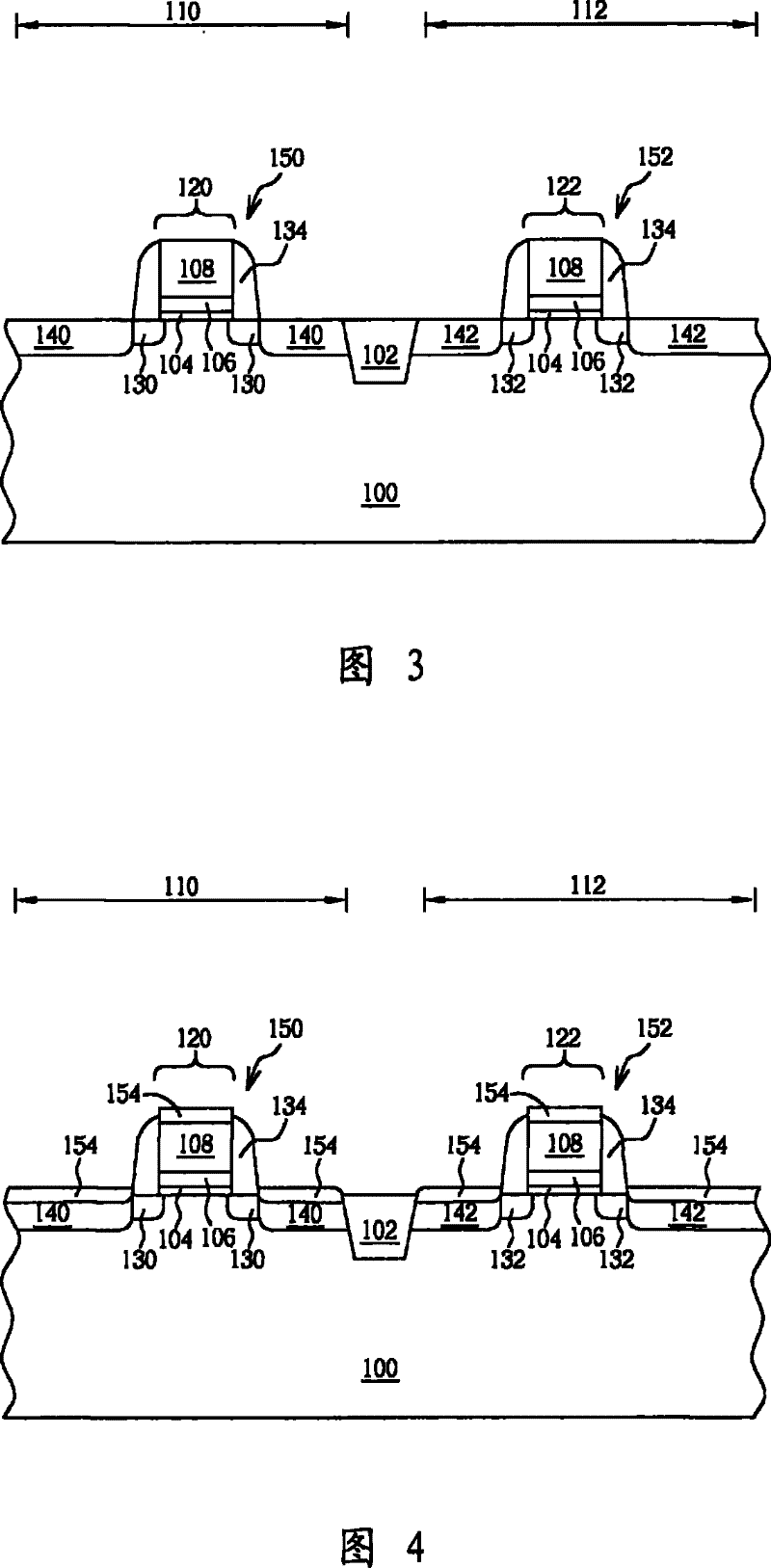

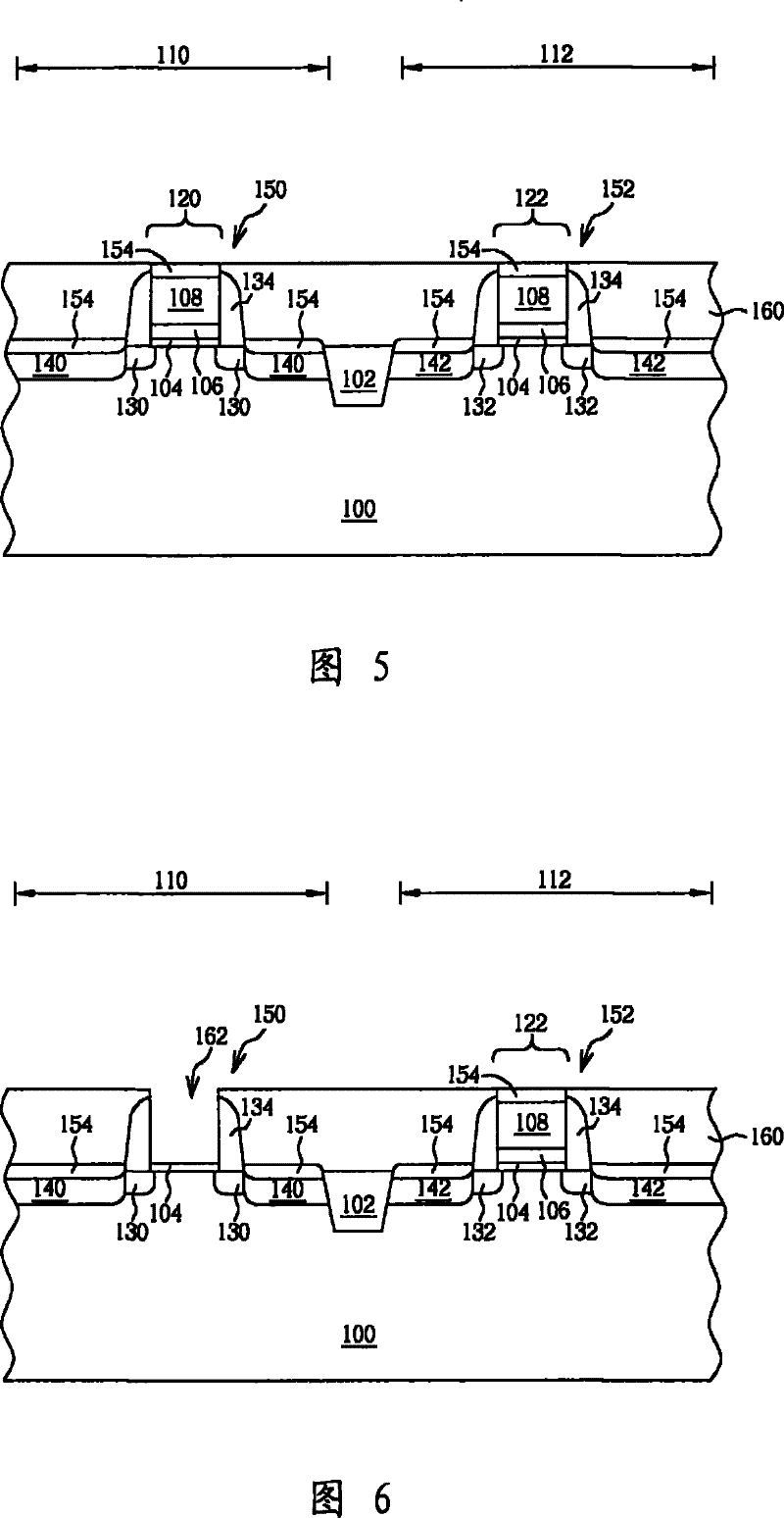

[0041] see Figure 2 to Figure 8 , Figure 2 to Figure 8 It is a schematic diagram of the first preferred embodiment of the method for manufacturing a CMOS device with a double metal gate provided by the present invention. Such as figure 2As shown, a substrate 100 is firstly provided, such as a silicon substrate, a silicon-containing substrate, or a silicon-on-insulator (hereinafter referred to as SOI) substrate, etc., and a first active region 110 and a second active region 110 are defined on the surface of the substrate 100. The active region 112 , and a shallow trench isolation (STI) 102 for electrically isolating the first active region 110 and the second active region 112 is formed in the substrate 100 . Next, a high dielectric constant (hereinafter referred to as High-K) gate dielectric layer 104 , a tantalum carbide (TaC) layer 106 , and a polysilicon layer 108 are sequentially formed on the substrate 100 . In addition, in the first embodiment, a protection layer (n...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com