Parasitic vertical PNP and manufacturing process thereof in BiCMOS process

A process, N-type technology, used in semiconductor/solid-state device manufacturing, electrical components, transistors, etc., can solve the problems of inability to meet chip integration requirements, low cut-off frequency, long transit time, etc., to eliminate adverse effects, improve Effect of Amplification Factor and Cutoff Frequency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] combine Figure 7 , the embodiment of the present invention includes the following steps:

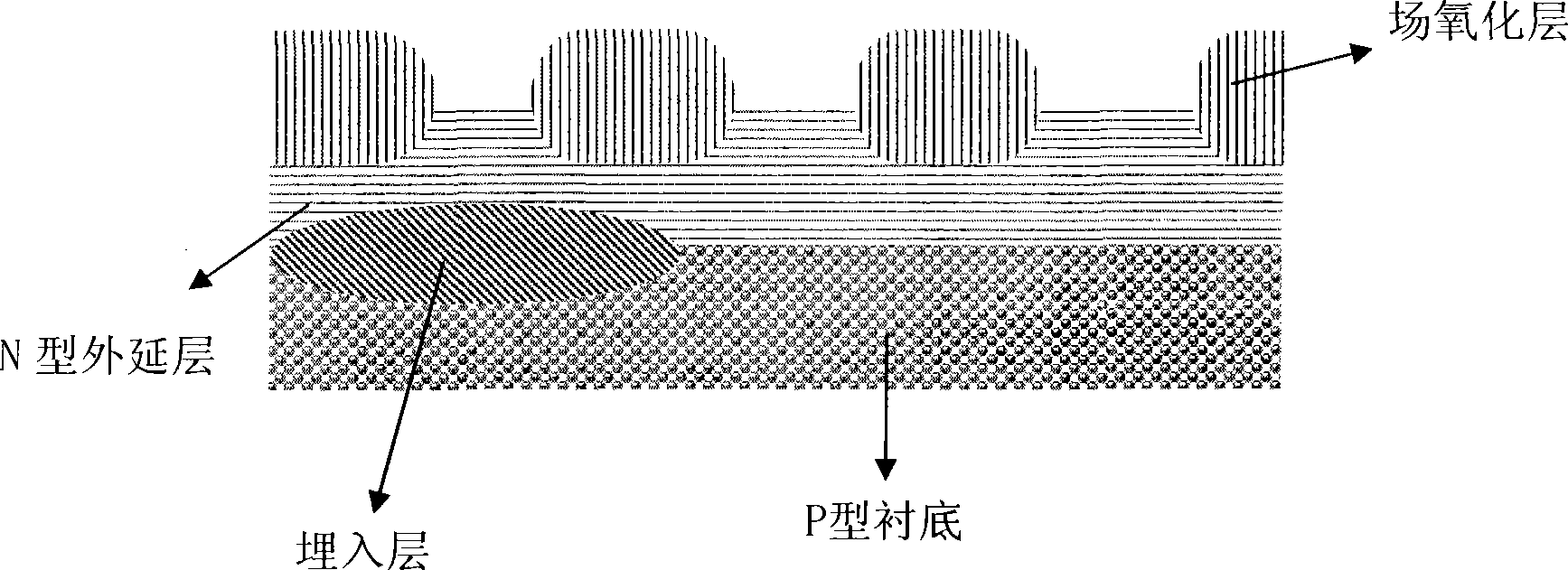

[0016] Such as figure 1 As shown, firstly, ion implantation of the buried layer is performed on the P-type substrate as the buried layer, N-type epitaxial growth and the formation of the active region.

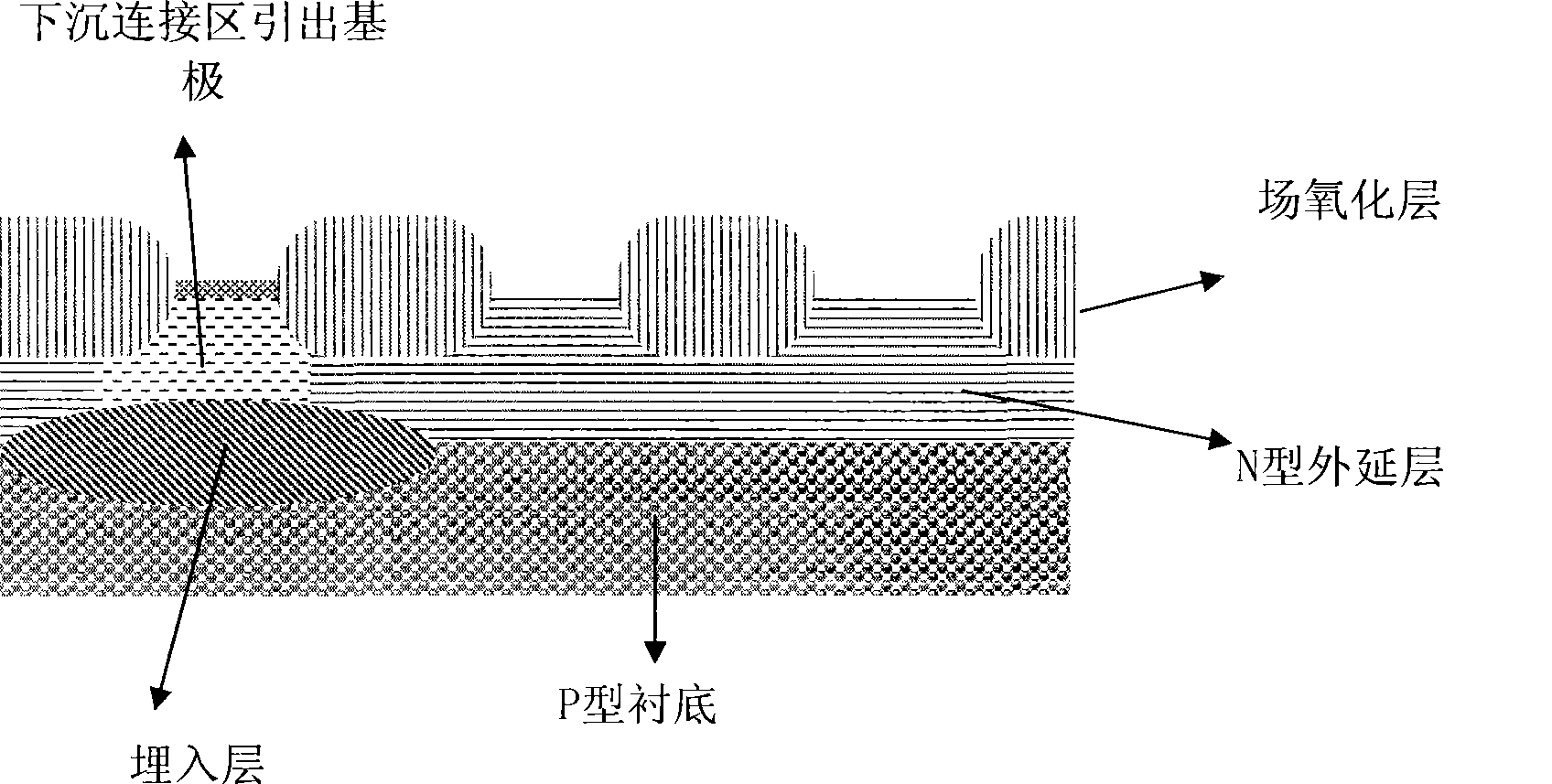

[0017] Secondly, if figure 2 As shown, ion implantation is carried out in the sinking connection layer. This layer is used as the vertical NPN collector and the parasitic lateral PNP base lead-out region in the BiCMOS process to connect with the outside world, and in the present invention as the base lead-out region of the vertical PNP.

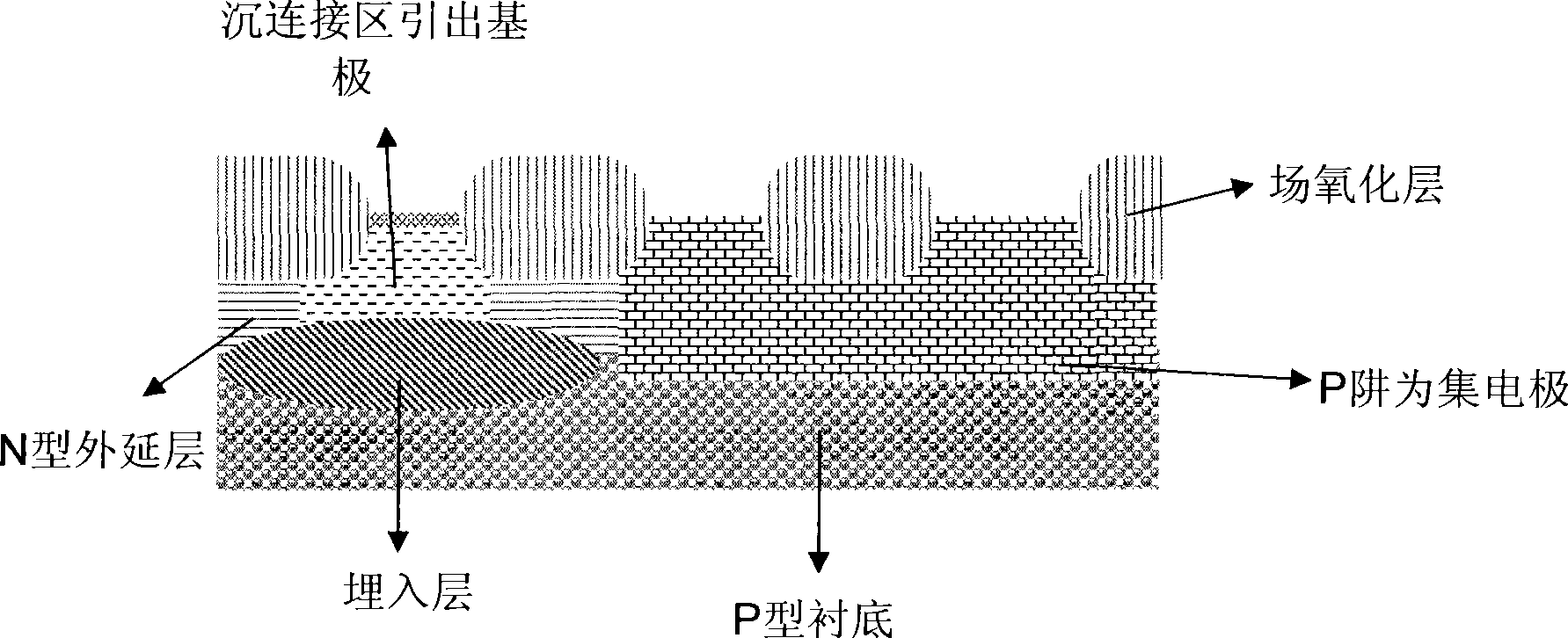

[0018] Then, if image 3 As shown, the CMOS P-well isolation ion implantation is performed while the vertical PNP region is opened for implantation, thereby forming a vertical PNP collector. The ion implantation depth penetrates the field oxide layer and the N-type epitaxial layer. At this time, the implanted ions are B, the energy is 400k...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com