Memory error-detecting and error-correcting coding circuit and method for reading and writing data utilizing the same

An error correction coding and memory reading technology, applied in static memory, instruments, etc., can solve the problems of affecting speed, complex and huge circuits, and large circuit delays.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

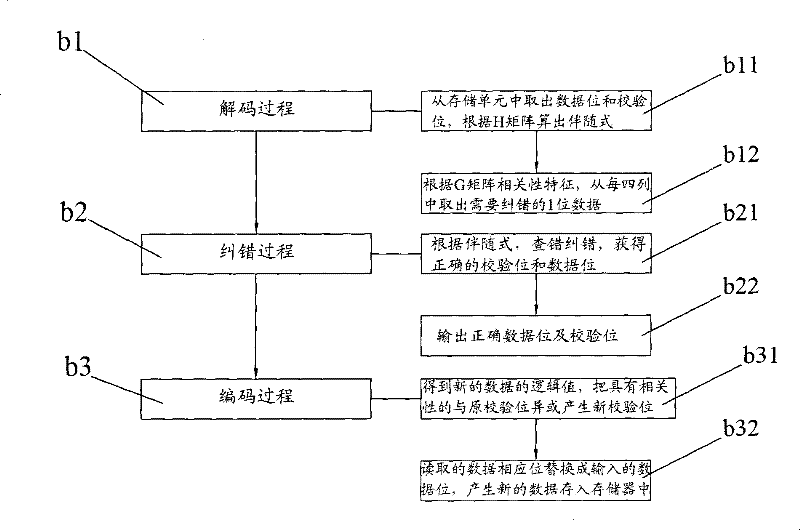

[0047]The above and other technical features and advantages of the present invention will be described in more detail below in conjunction with the accompanying drawings.

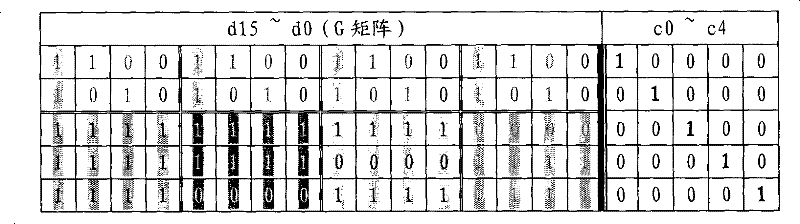

[0048] Specific embodiments of the present invention specifically disclose the method and circuit structure, and the corresponding number of stored data for verification is 4 bits;

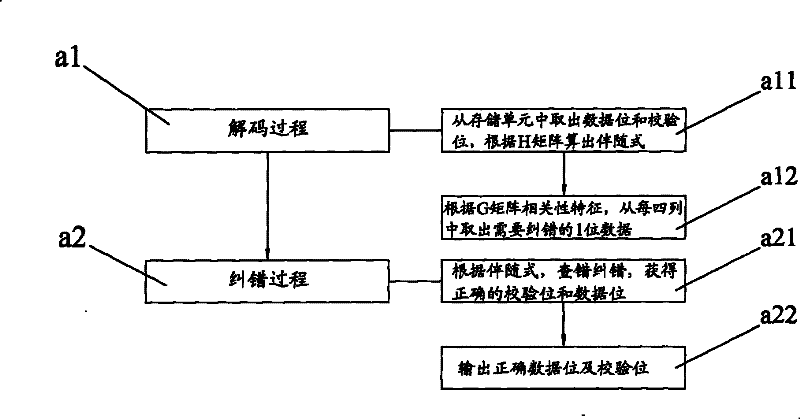

[0049] see figure 1 As shown, it is a flow chart of the steps of the error checking and error correction method for reading data from the memory in the present invention. The steps it includes are:

[0050] Step a1: a decoding process, wherein the decoding process includes the following steps:

[0051] Step a11: take out the data bit and check bit from the storage unit, and calculate the adjoint formula according to the H matrix;

[0052] Step a12: According to the correlation characteristics of the G matrix, the extracted data bits and check bits are controlled by address information, and the 1-bit data that needs to be corr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com