Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

51results about How to "Minimizes shifting" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

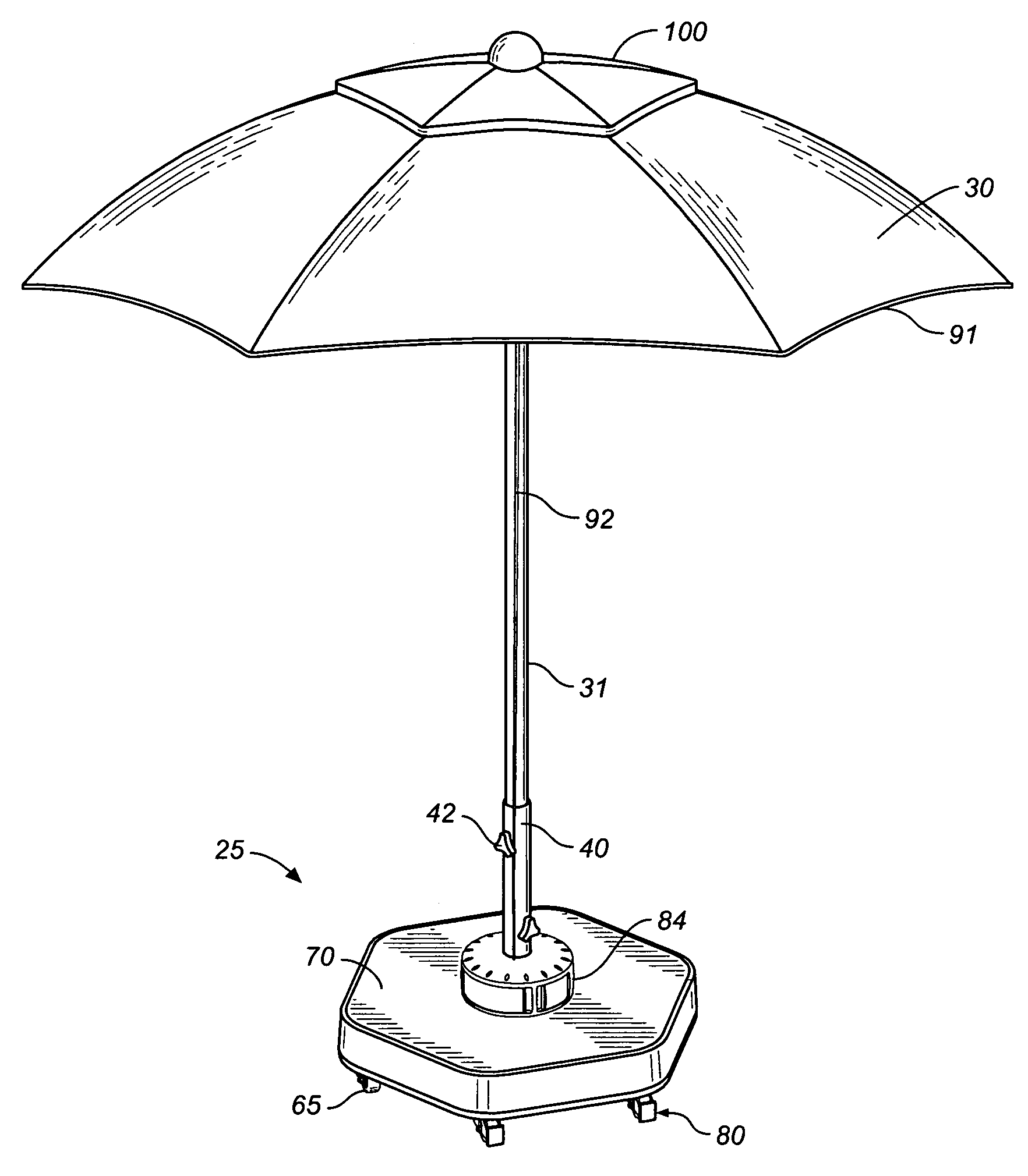

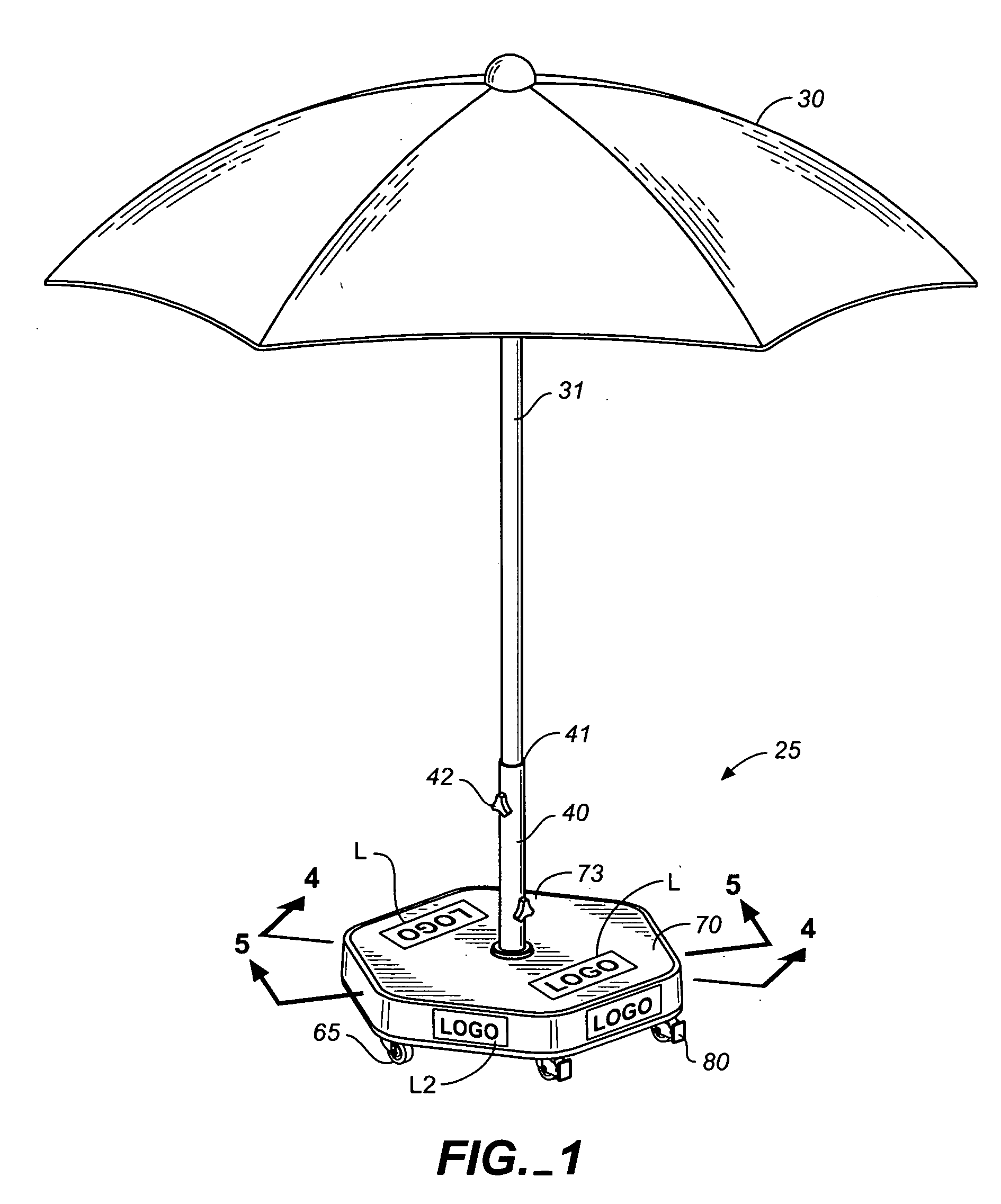

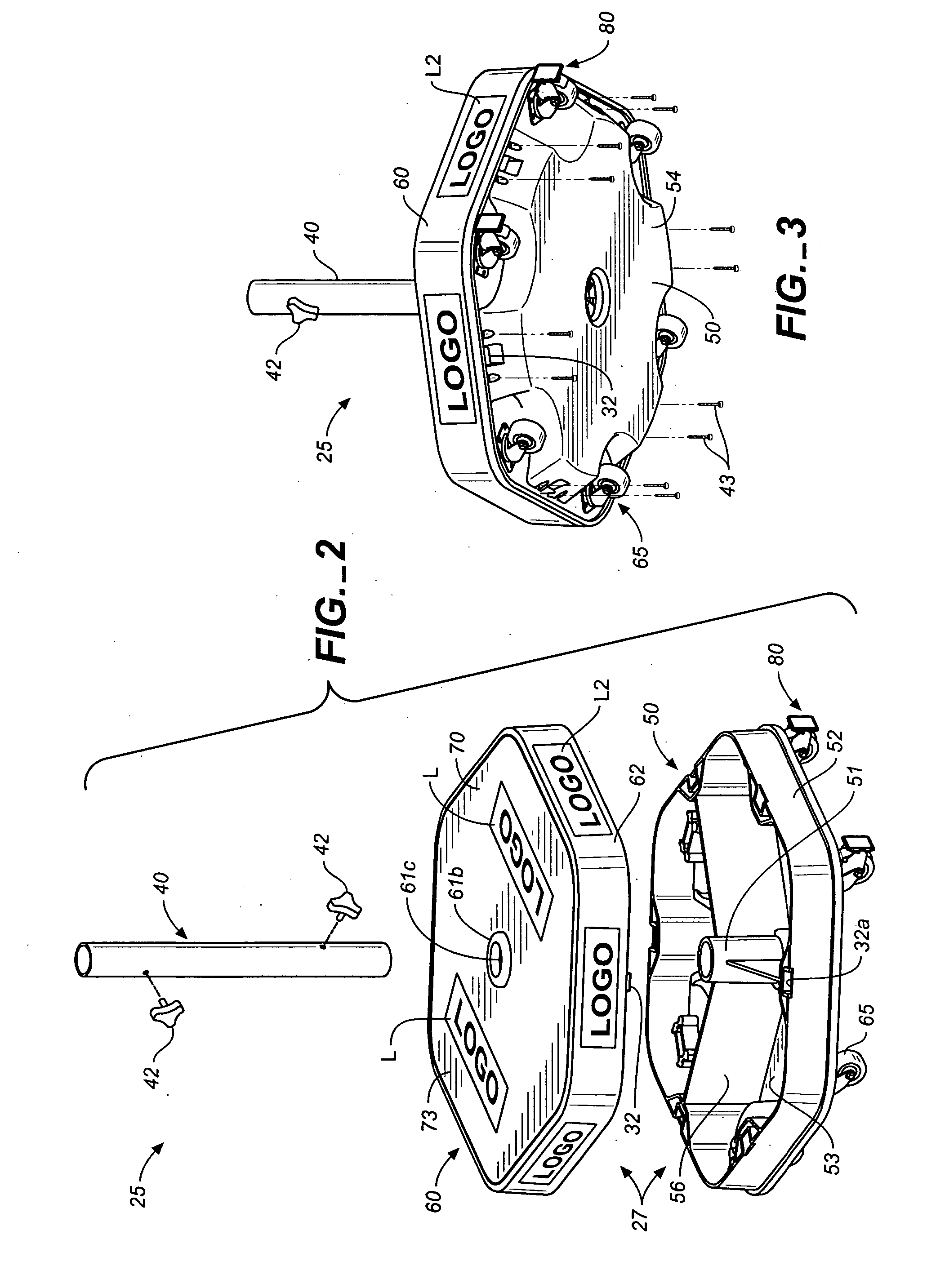

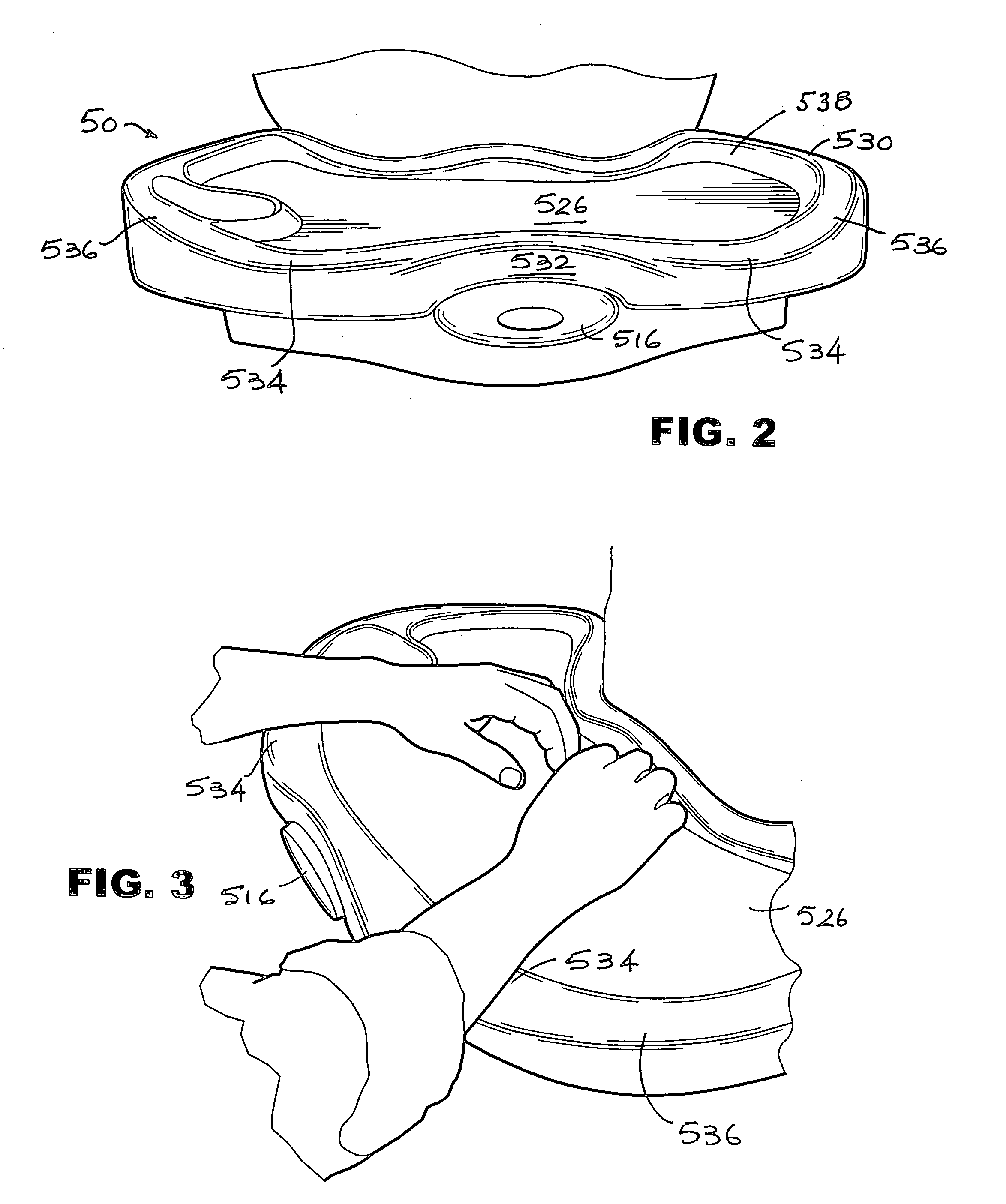

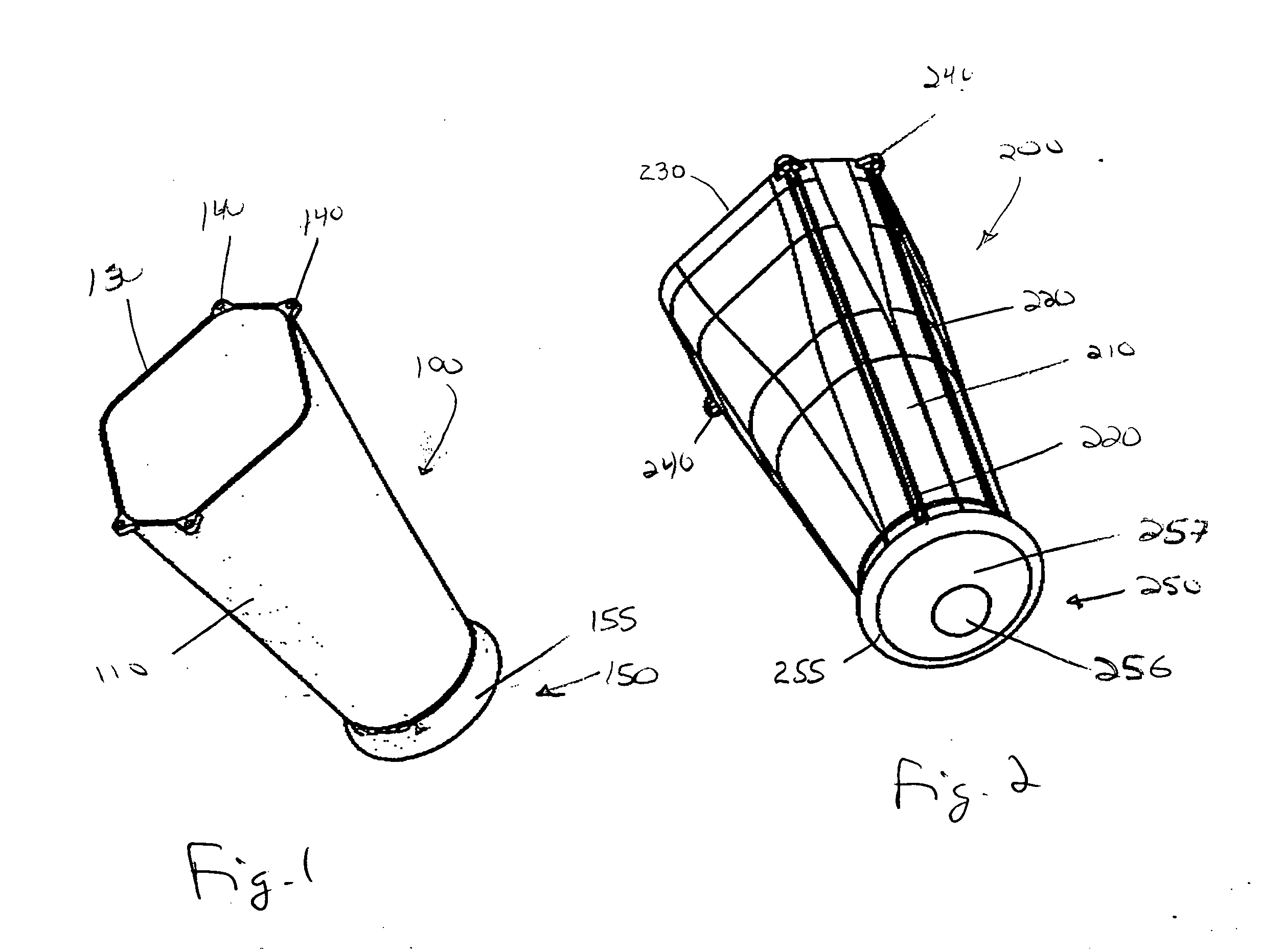

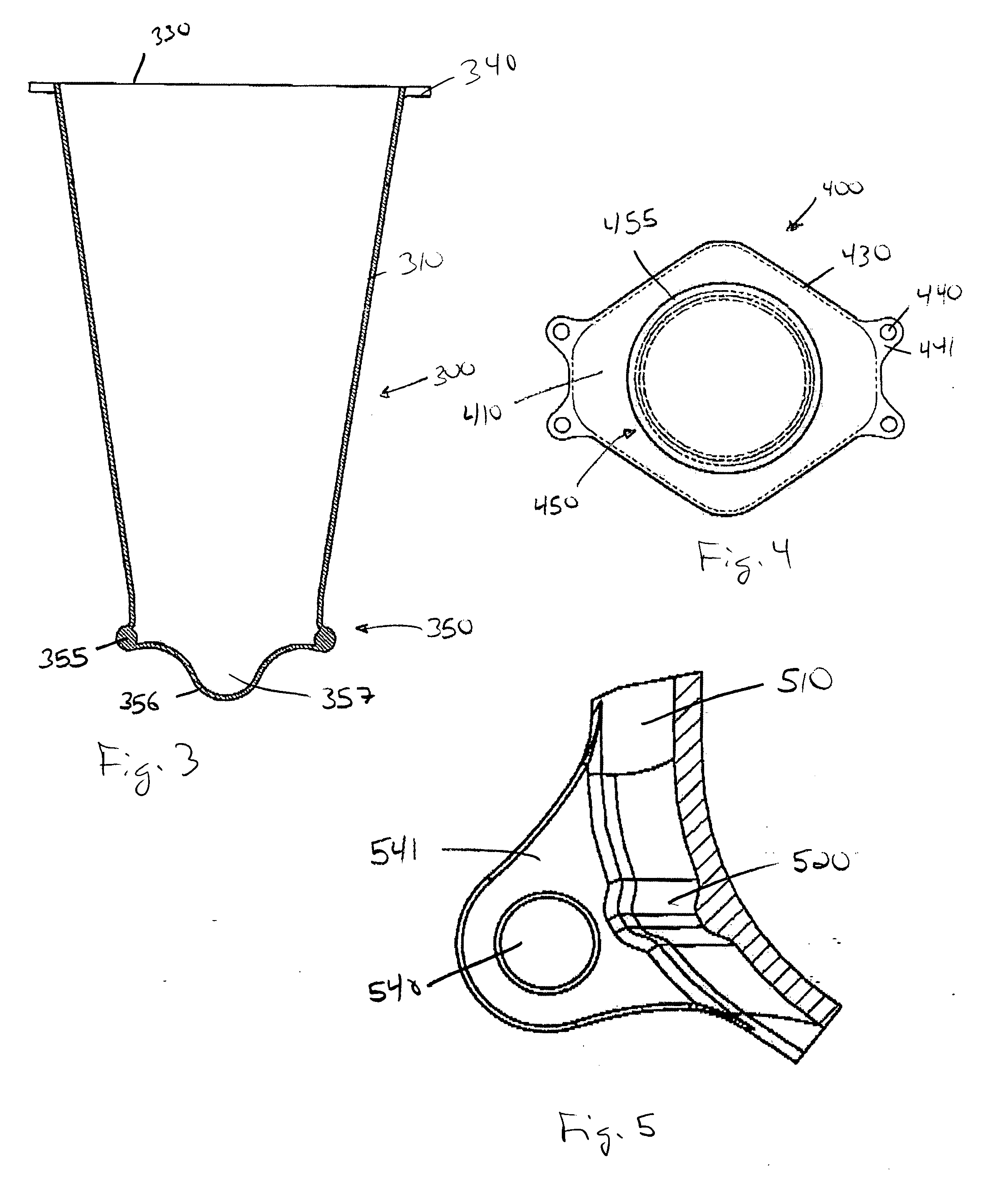

Umbrella base with power supply

InactiveUS7614600B1Promotes even distributionMinimizes shiftingWalking sticksUmbrellasElectrical devicesEngineering

An umbrella base is comprised of a body portion containing a power source for powering umbrella lights or electrical devices or appliances used around the umbrella or other furniture accessory held by the base. A power console is provided for use on or above the base to provide connectivity to the power supply.

Owner:ROLLING UMBRELLAS INC

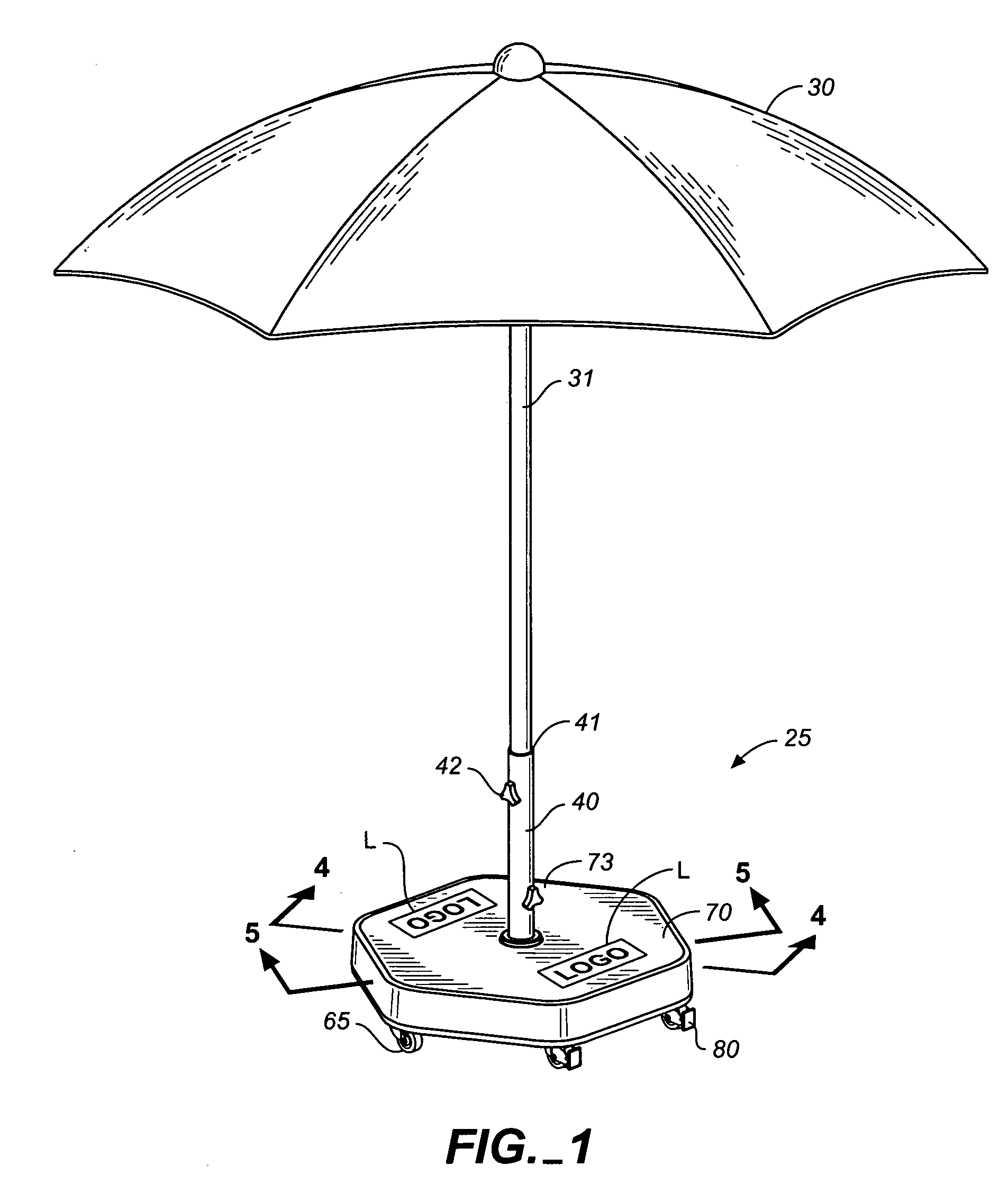

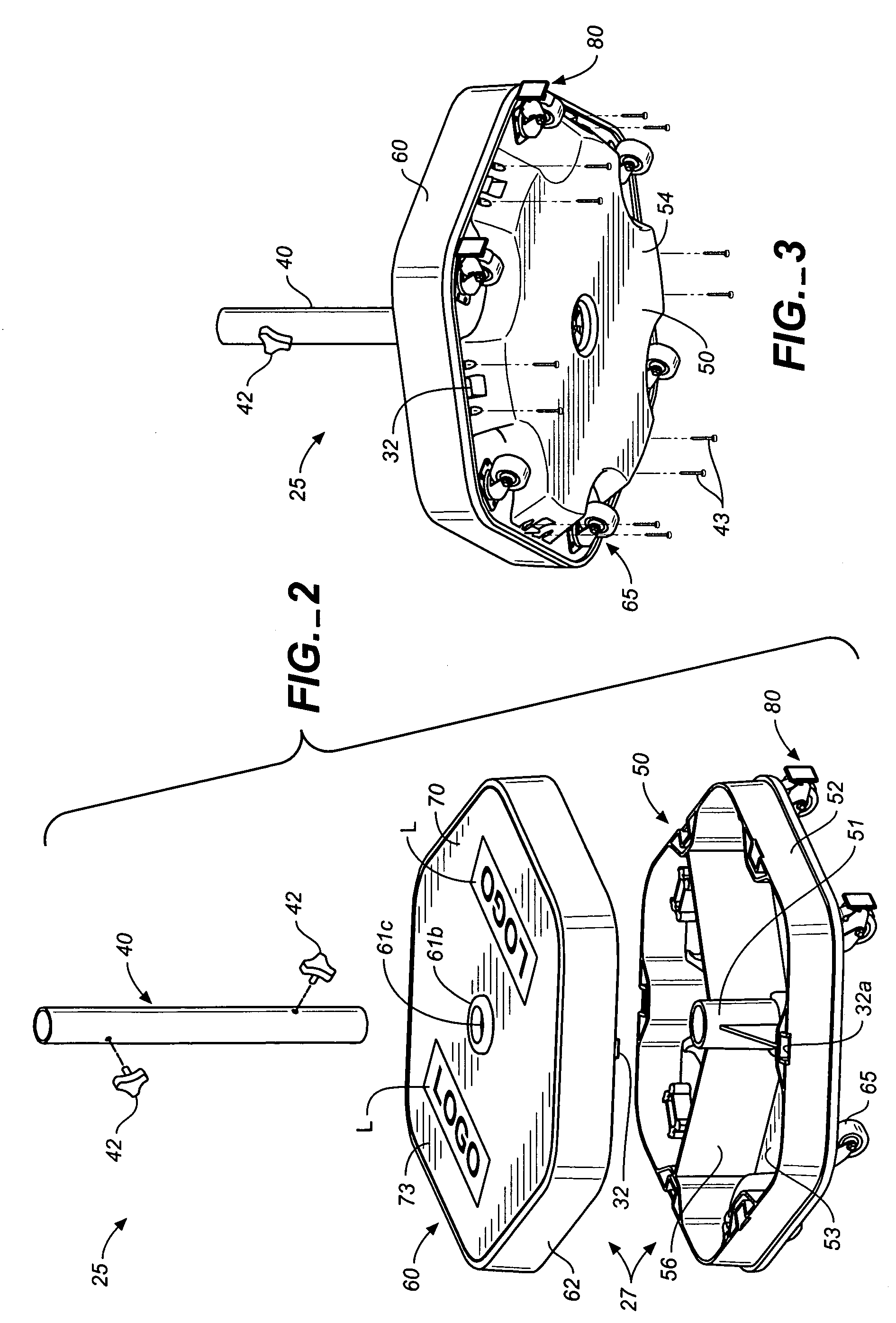

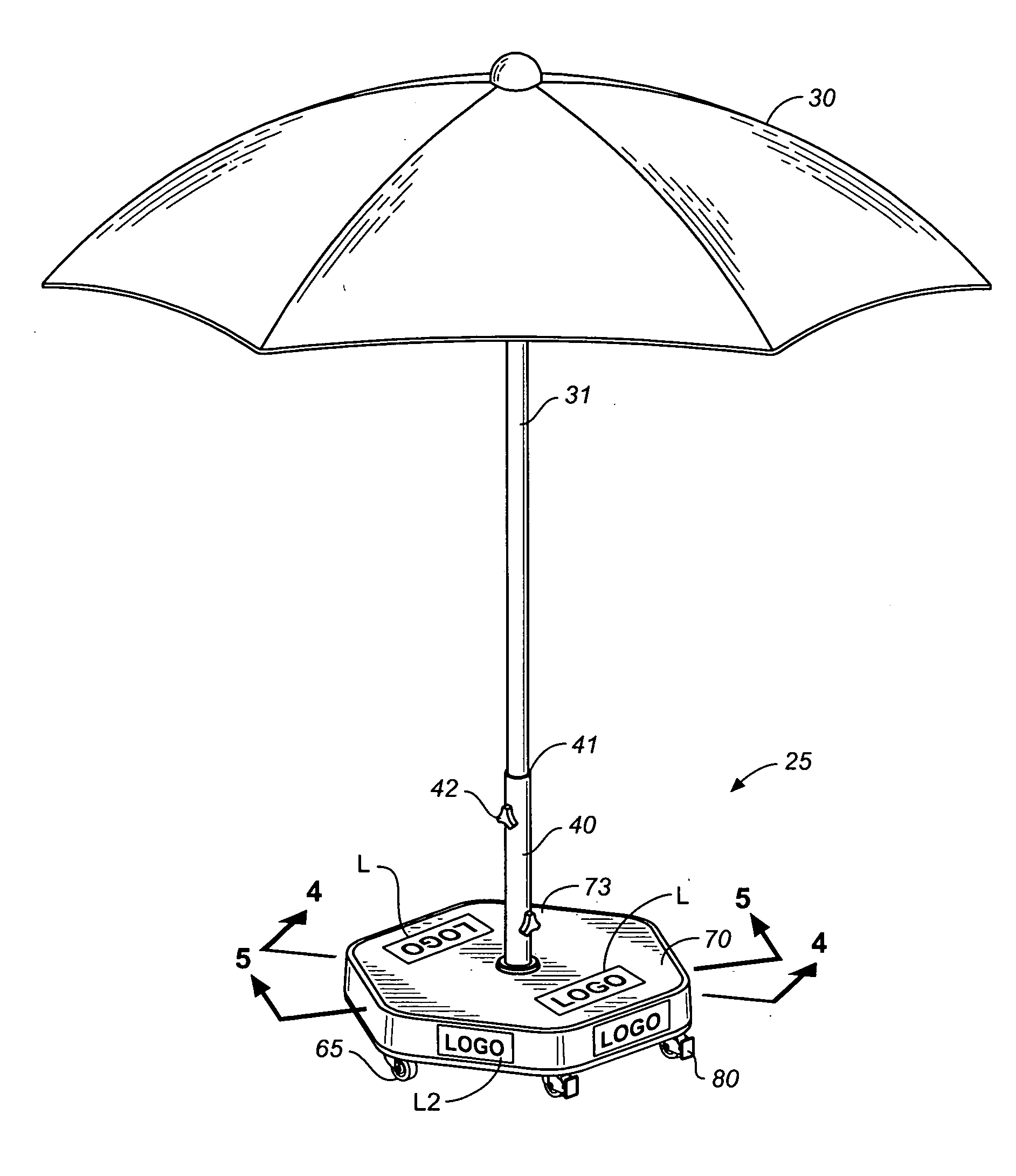

Umbrella base

An umbrella base is comprised of a body portion having a billboard surface for advertising a company, organization, products, service or the like. The billboard surface can be provided on a separate removable billboard plate placed on the top of the body portion, which allows the advertising message to be easily changed. In its preferred construction, the body portion has at least one ballast cavity, and preferably multiple ballast cavities, and is constructed in separable parts to permit a selected ballast to be added to the ballast cavities in order to add a desired ballast weight to the umbrella base. The umbrella base can also be provided with casters, including locking casters, so that the umbrella base and its advertising message can be easily moved across a surface from one location to the another.

Owner:ROLLING UMBRELLAS

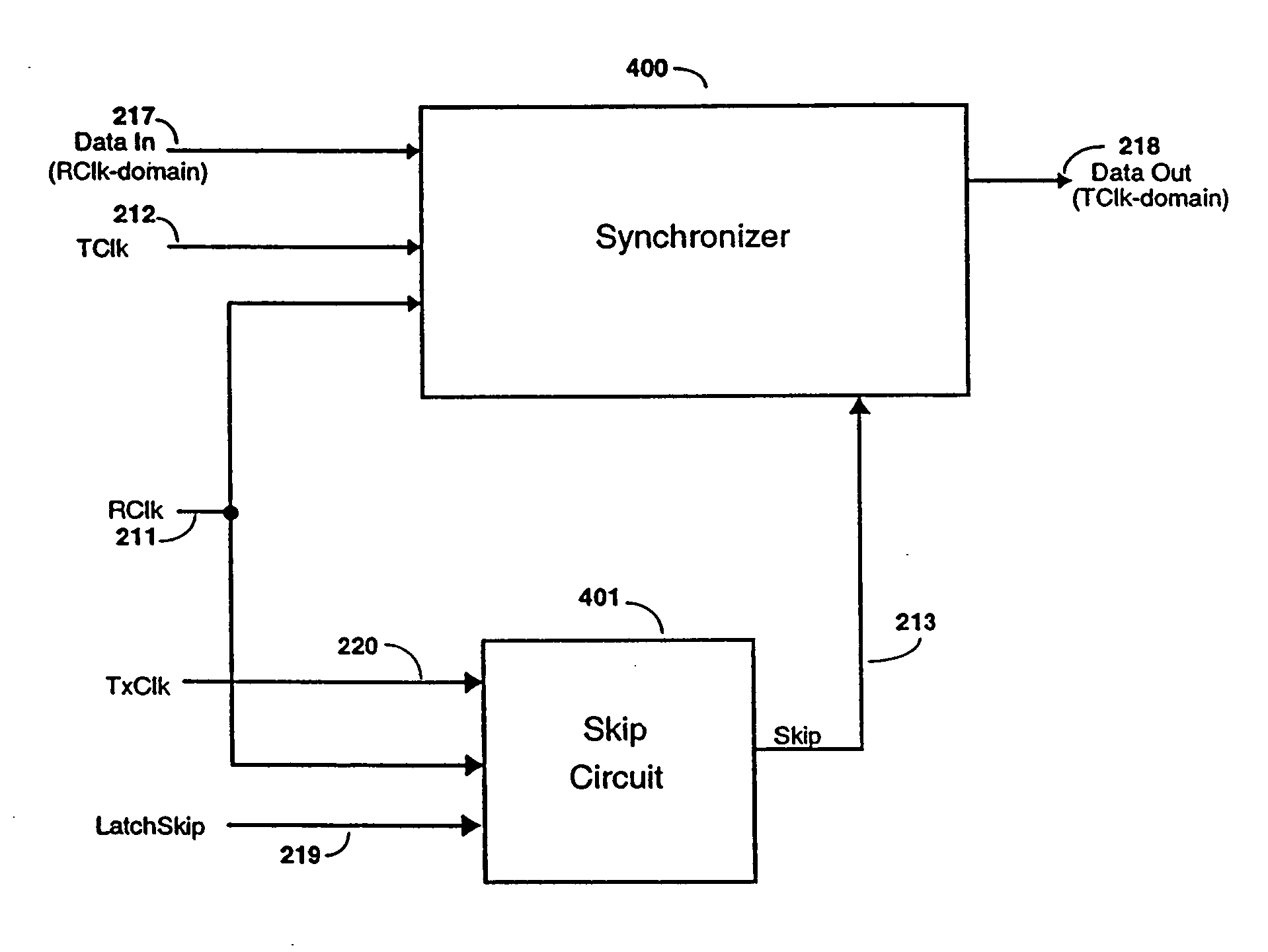

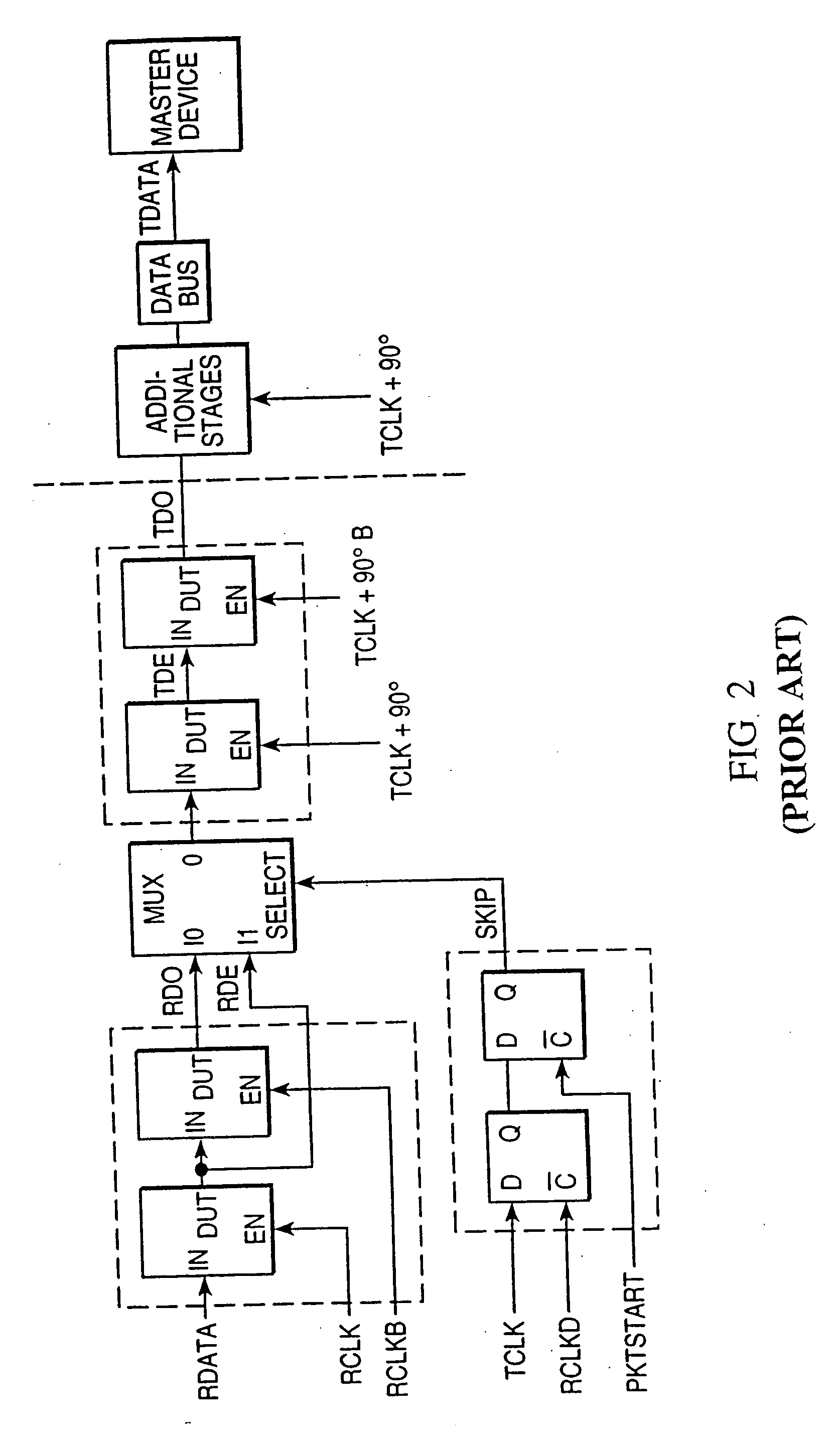

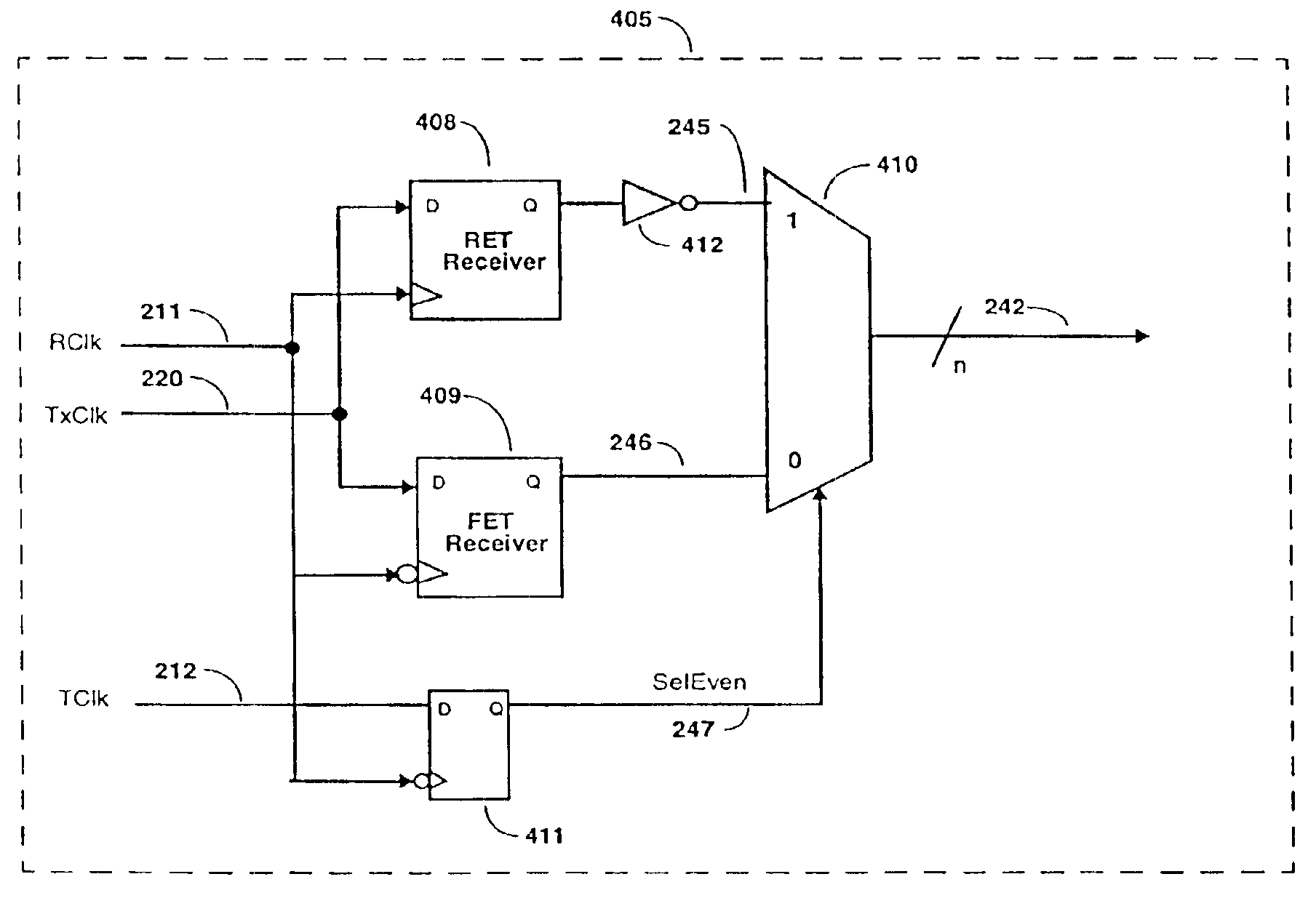

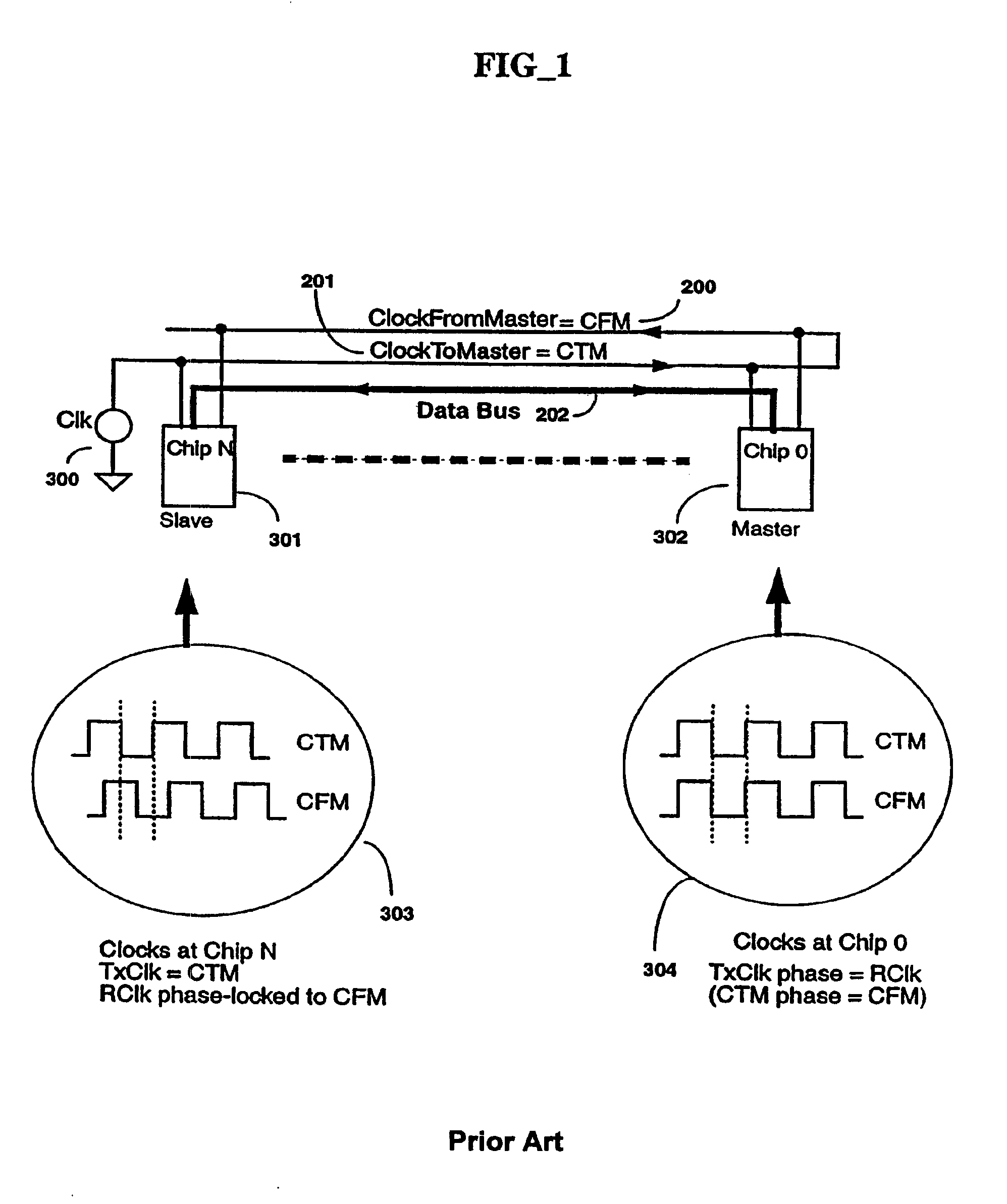

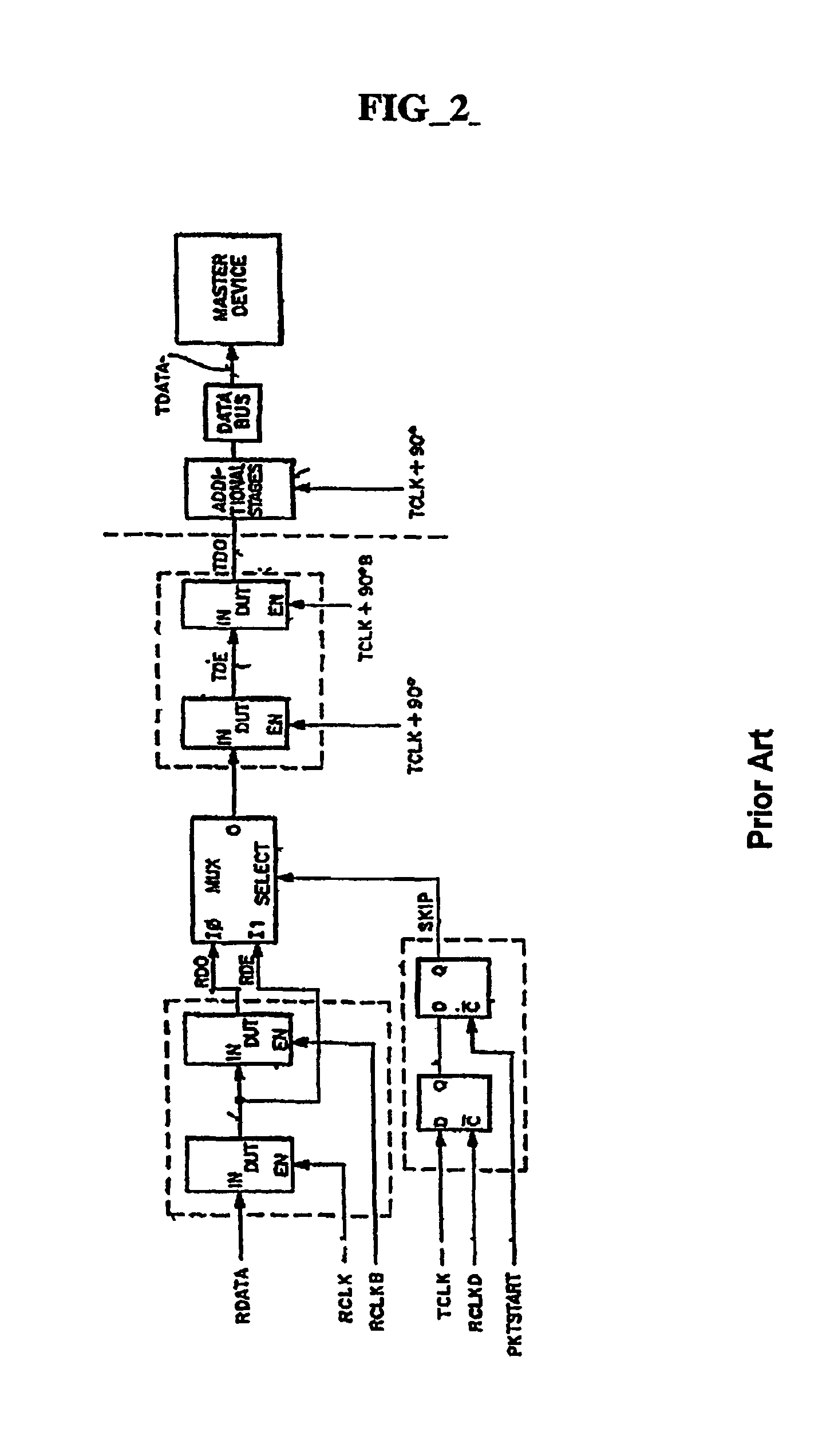

Method and apparatus for fail-safe resynchronization with minimum latency

InactiveUS20060022724A1Guaranteed uptimeMinimizes shiftingSynchronisation information channelsPulse automatic controlData latencyVoltage shift

Owner:RAMBUS INC

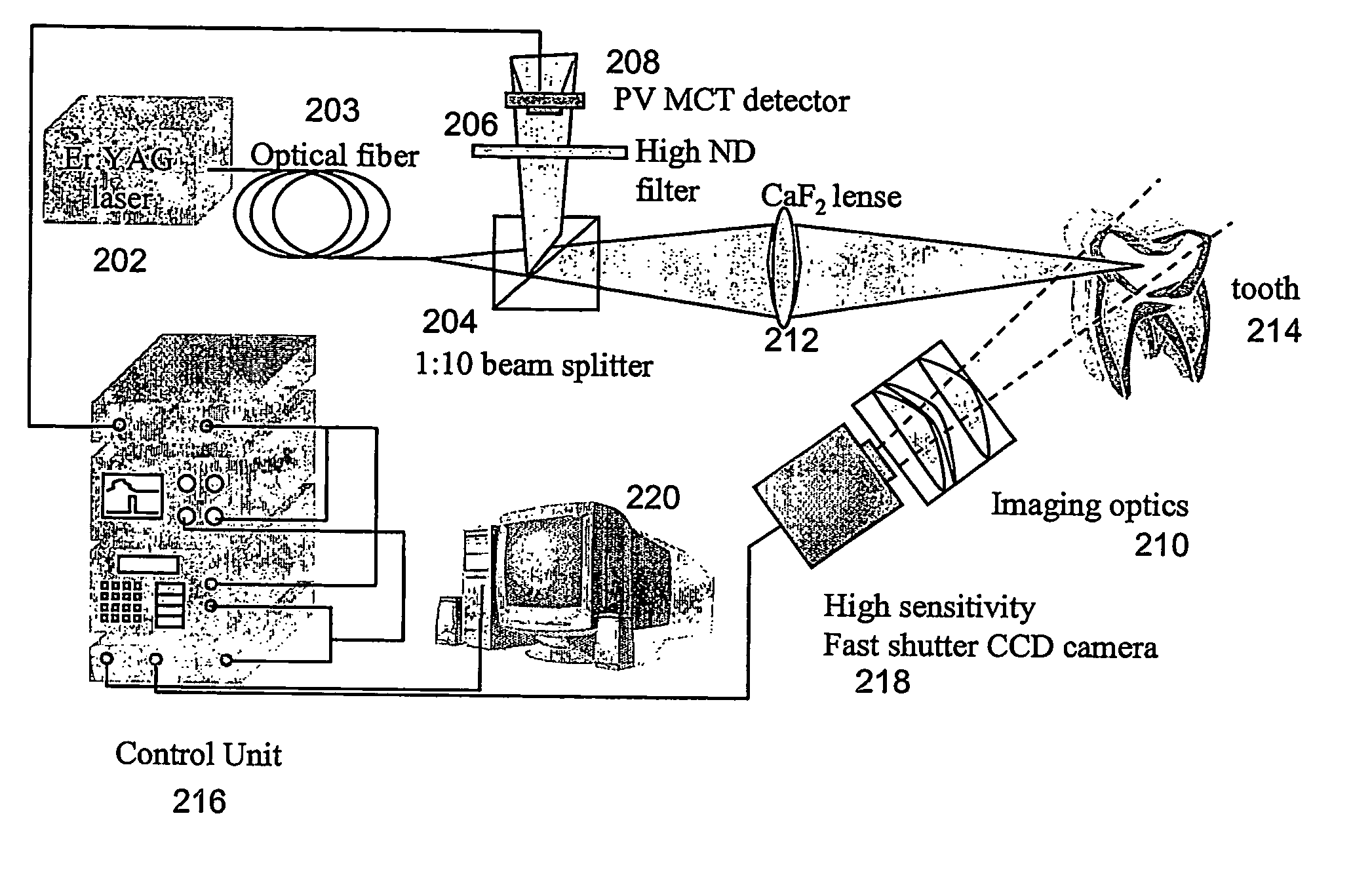

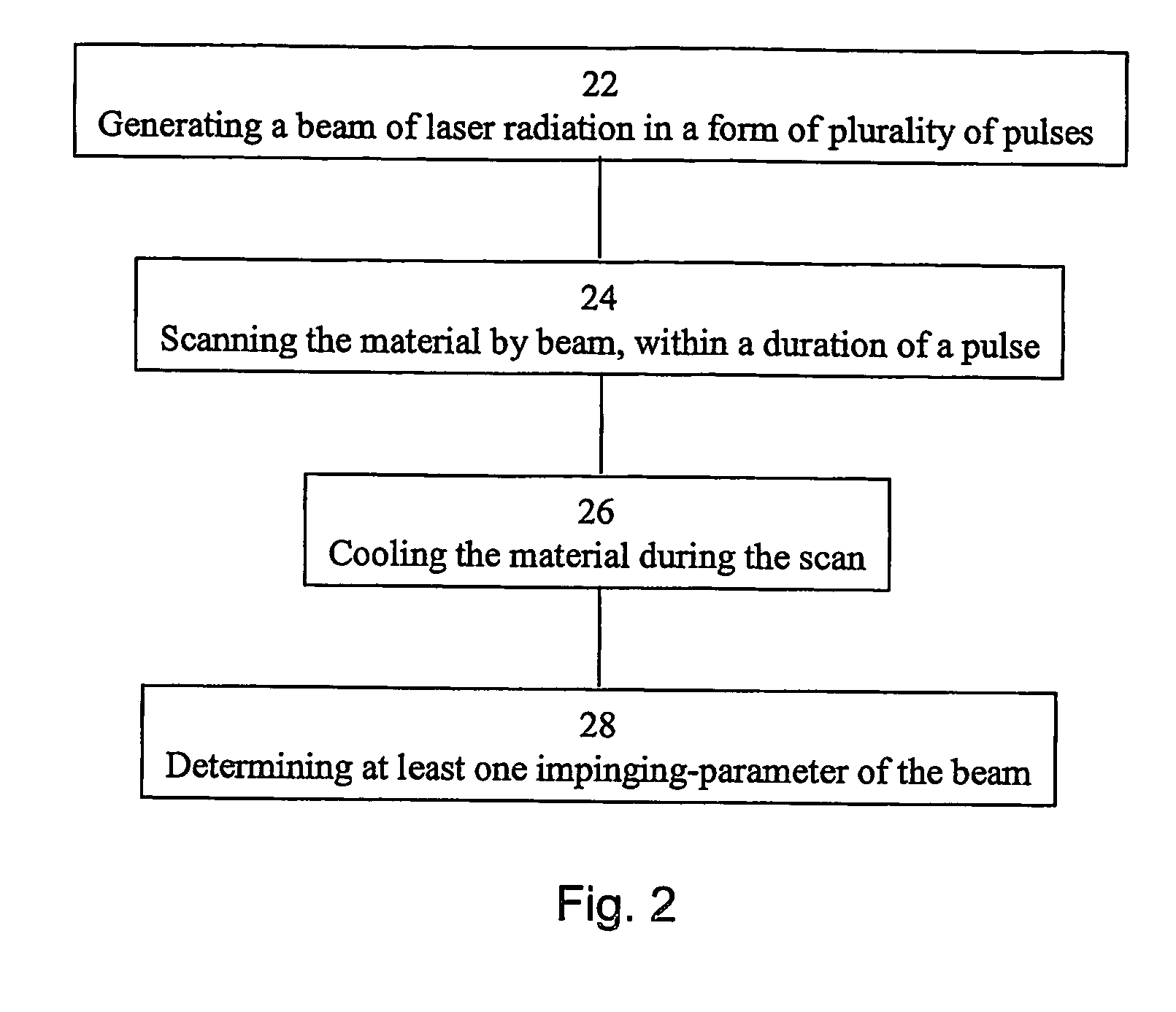

System,apparatus and method for large area tissue ablation

InactiveUS20060189965A1Reduce heatMinimizes shiftingDiagnosticsSurgical instrument detailsLight beamLength wave

A method of ablating a material, the method comprising: (a) generating a beam of laser radiation in a form of plurality of pulses, the laser radiation having a wavelength suitable for ablating the material; and (b) within a duration of a pulse of the plurality of pulses, scanning the material by the beam, so as to transfer a predetermined amount of energy to each one of a plurality of locations of the material, the predetermined amount of energy being selected so as to ablate the material.

Owner:B E D LASER TECH

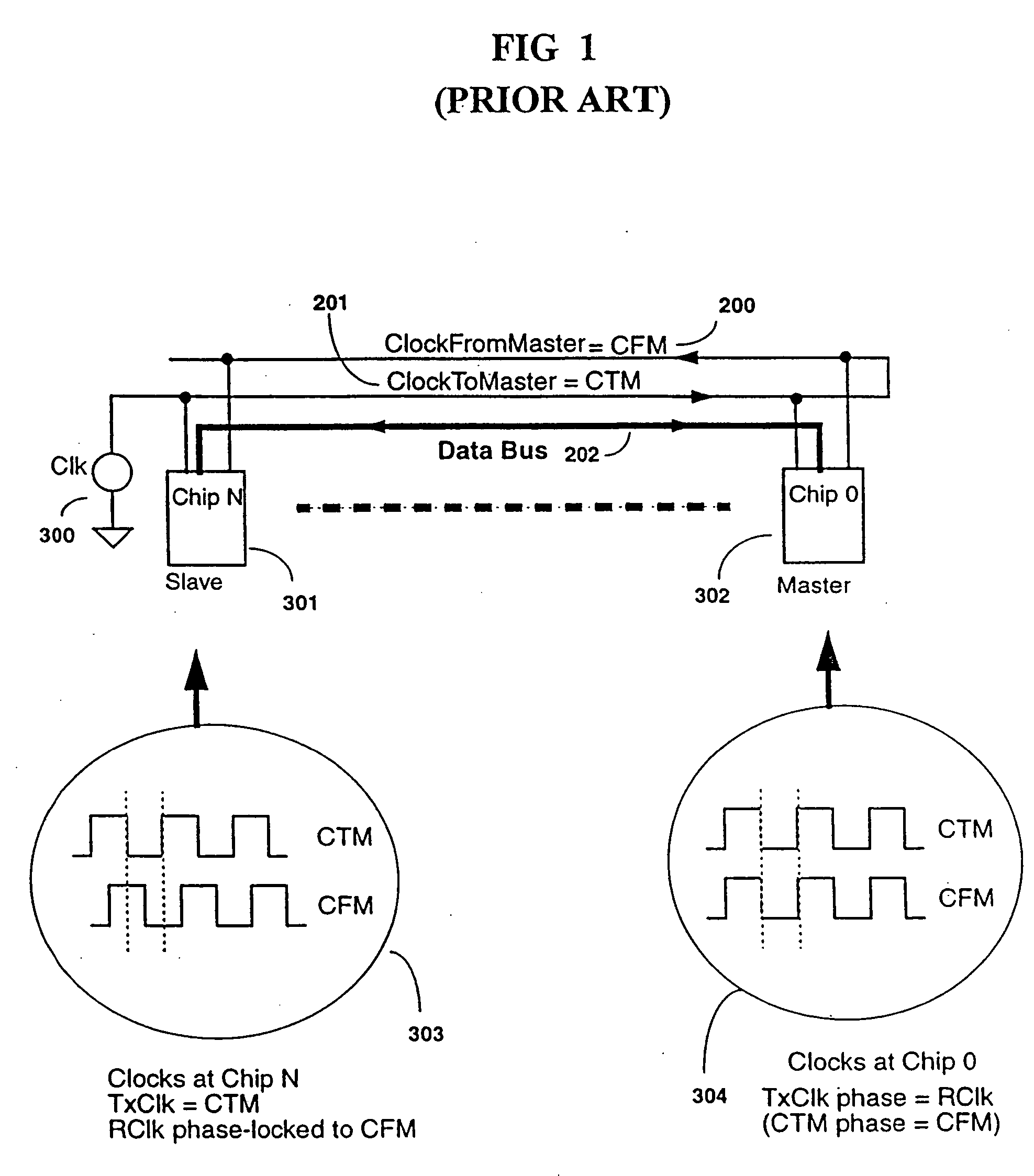

Phase comparator capable of tolerating a non-50% duty-cycle clocks

InactiveUS6949958B2Stable operating configurationGuaranteed uptimeSynchronisation information channelsPulse automatic controlInfinite busMinimum latency

A method and circuit for achieving minimum latency data transfer between two mesochronous (same frequency, different phase) clock domains is disclosed. This circuit supports arbitrary phase relationships between two clock domains and is tolerant of temperature and voltage shifts after initialization while maintaining the same output data latency. In one embodiment, this circuit is used on a bus-system to re-time data from receive-domain, clocks to transmit-domain clocks. In such a system the phase relationships between these two clocks is set by the device bus location and thus is not precisely known. By supporting arbitrary phase resynchronization, this disclosure allows for theoretically infinite bus-length and thus no limitation on device count, as well as arbitrary placement of devices along the bus. This ultimately allows support of multiple latency-domains for very long buses.

Owner:RAMBUS INC

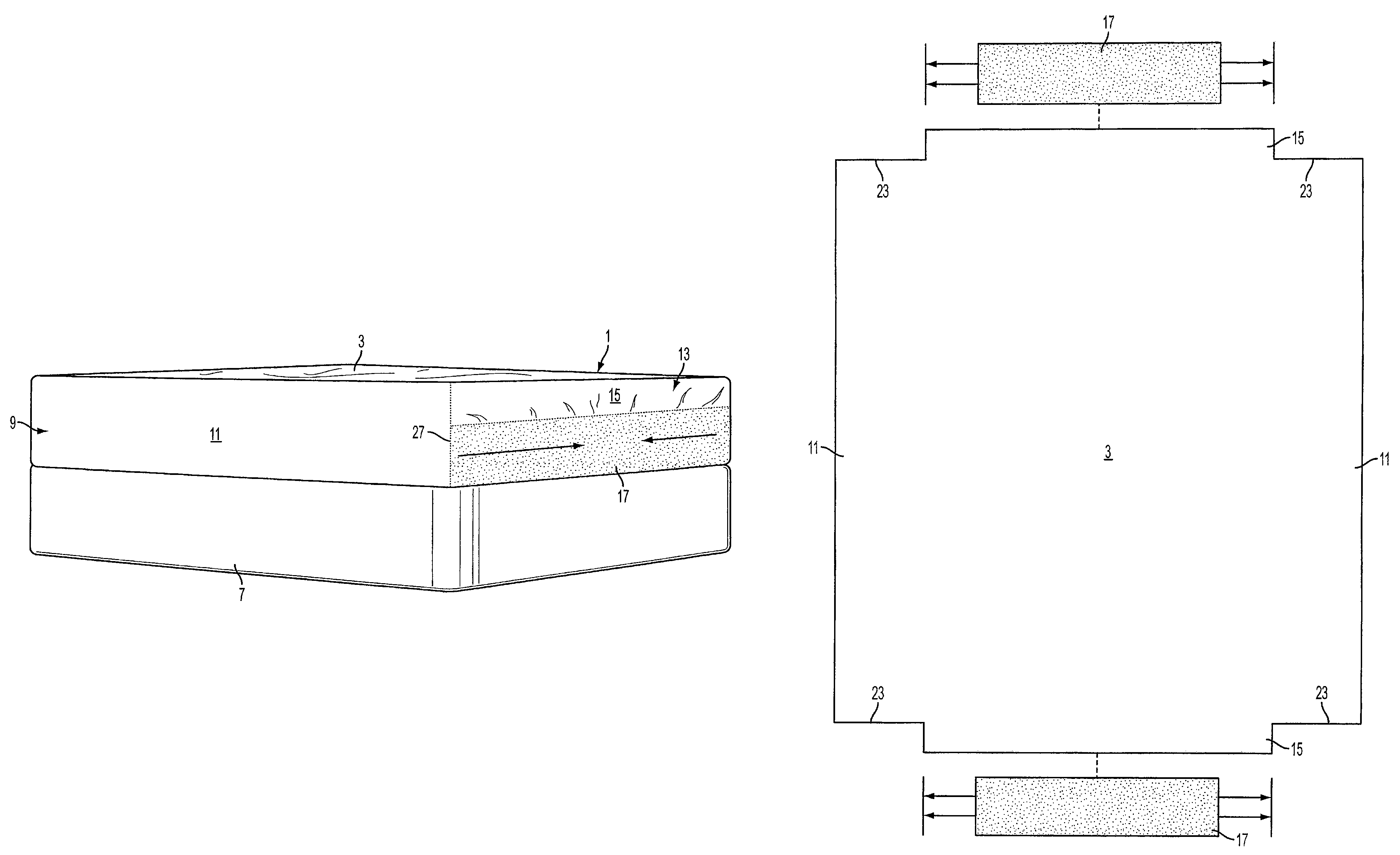

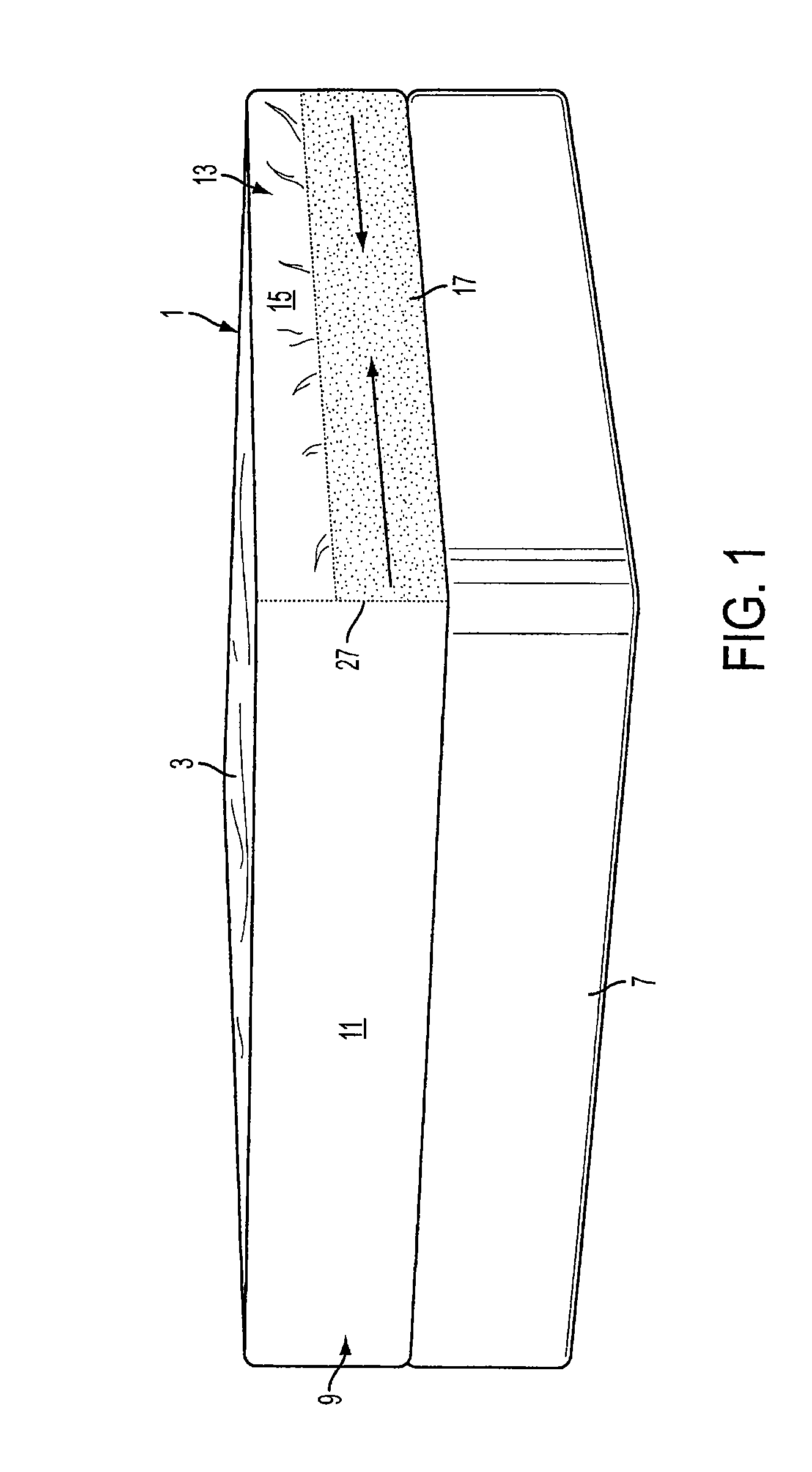

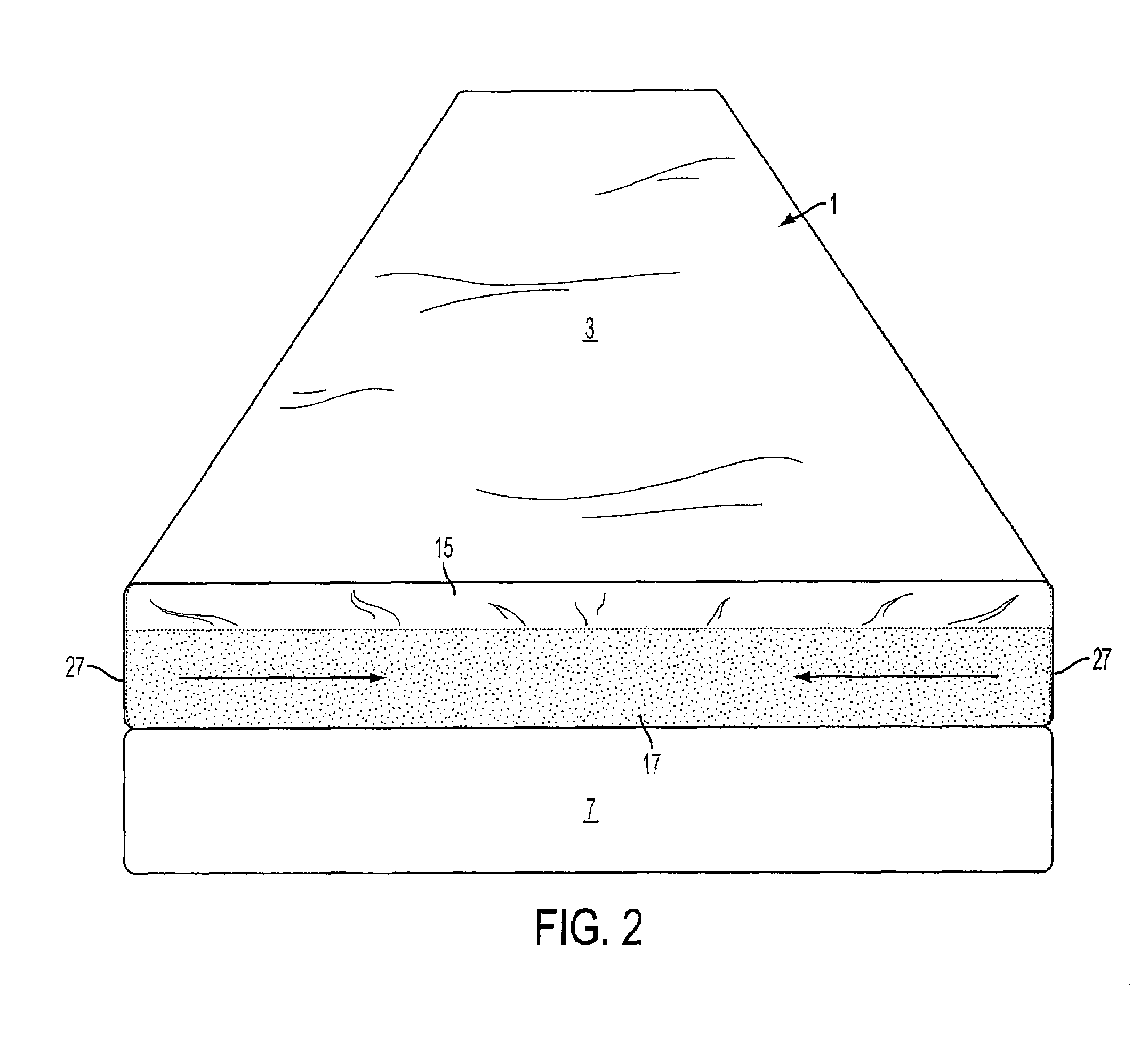

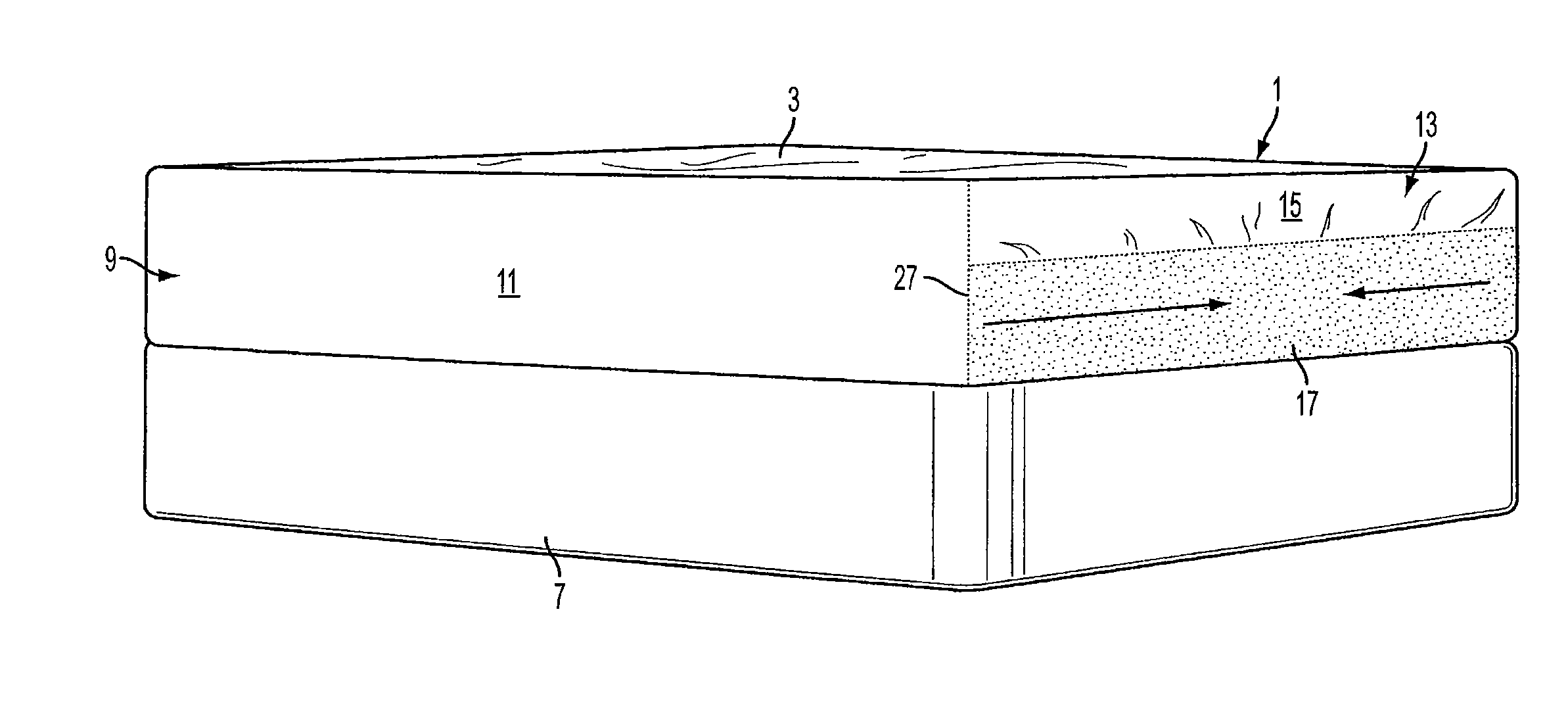

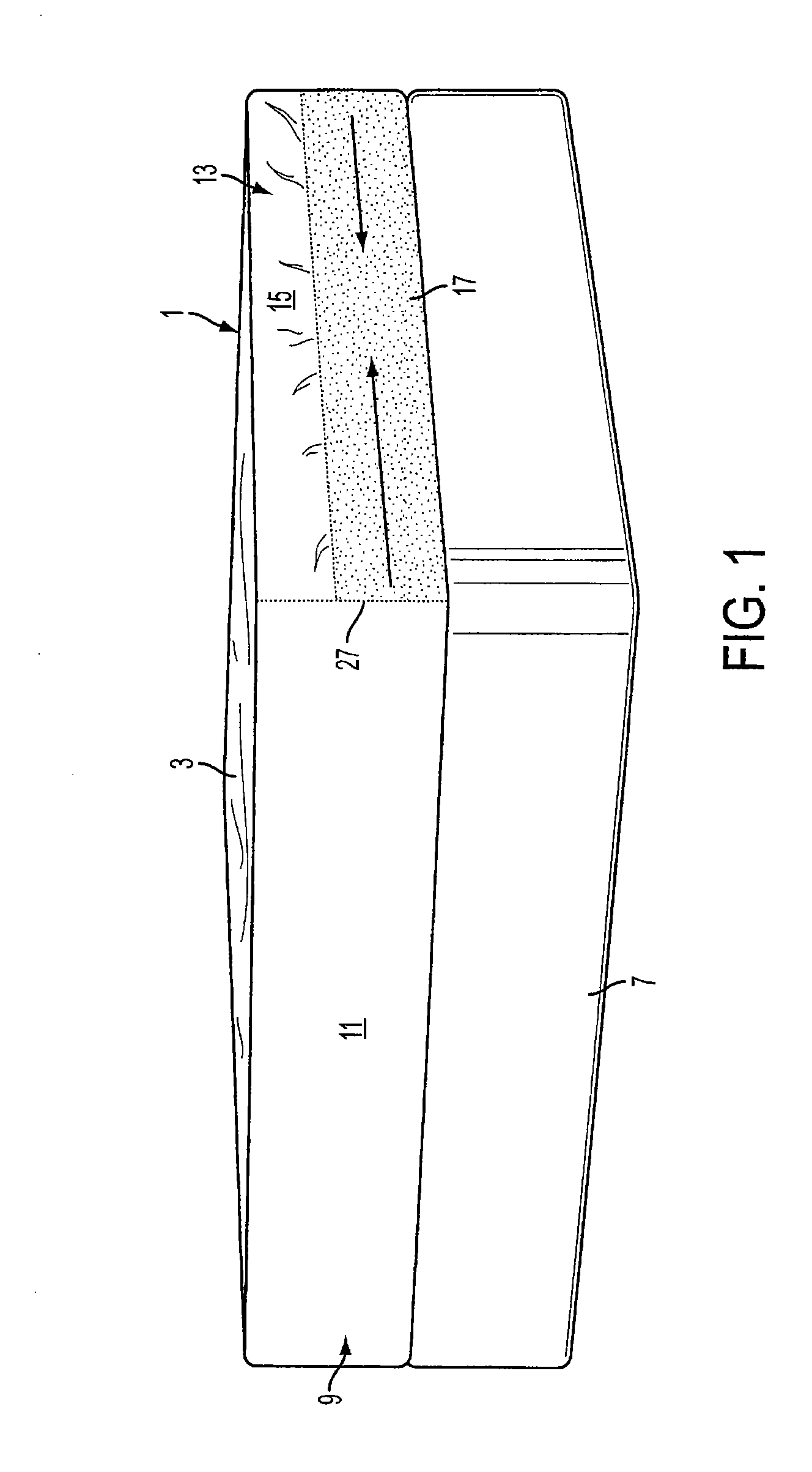

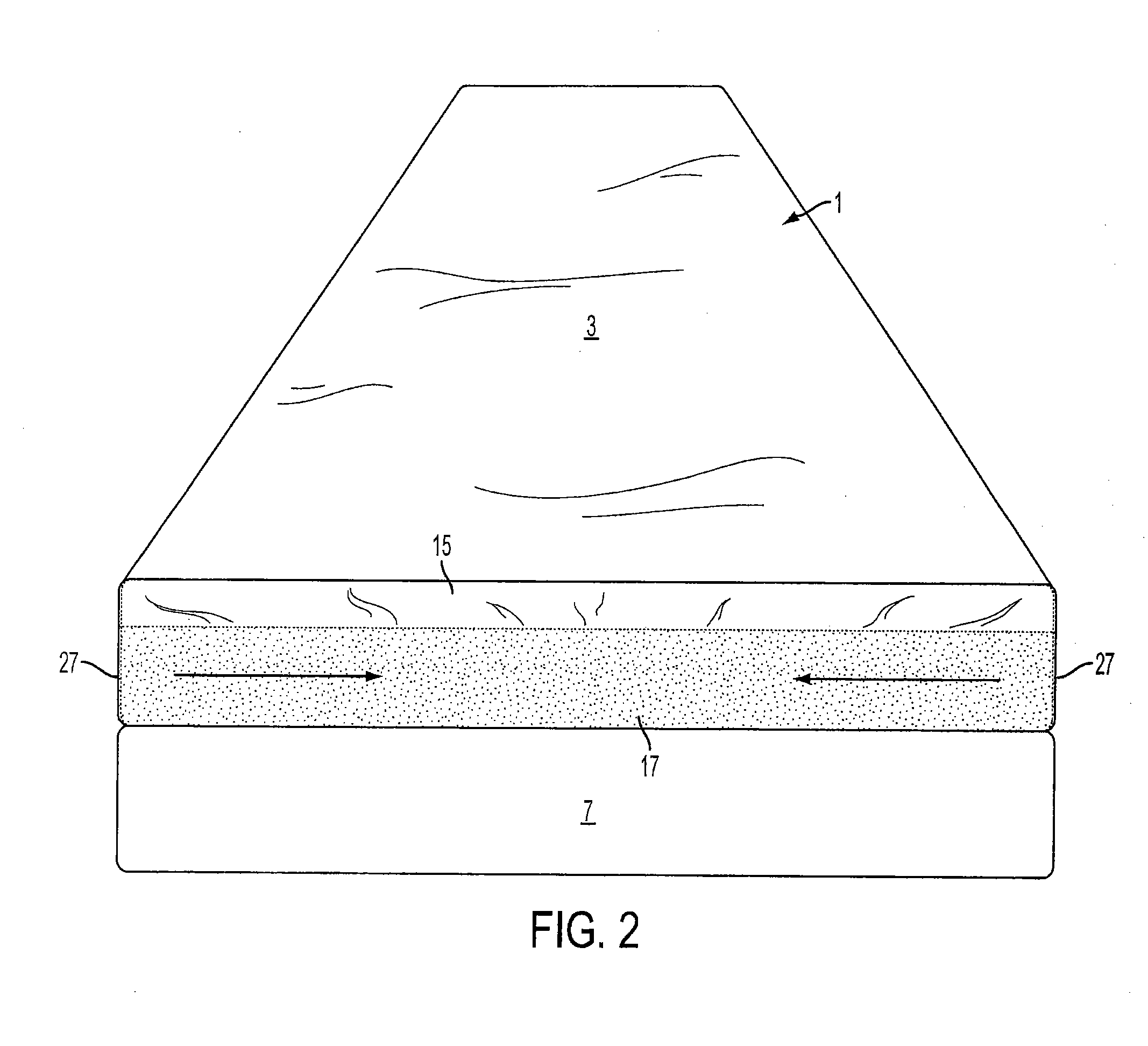

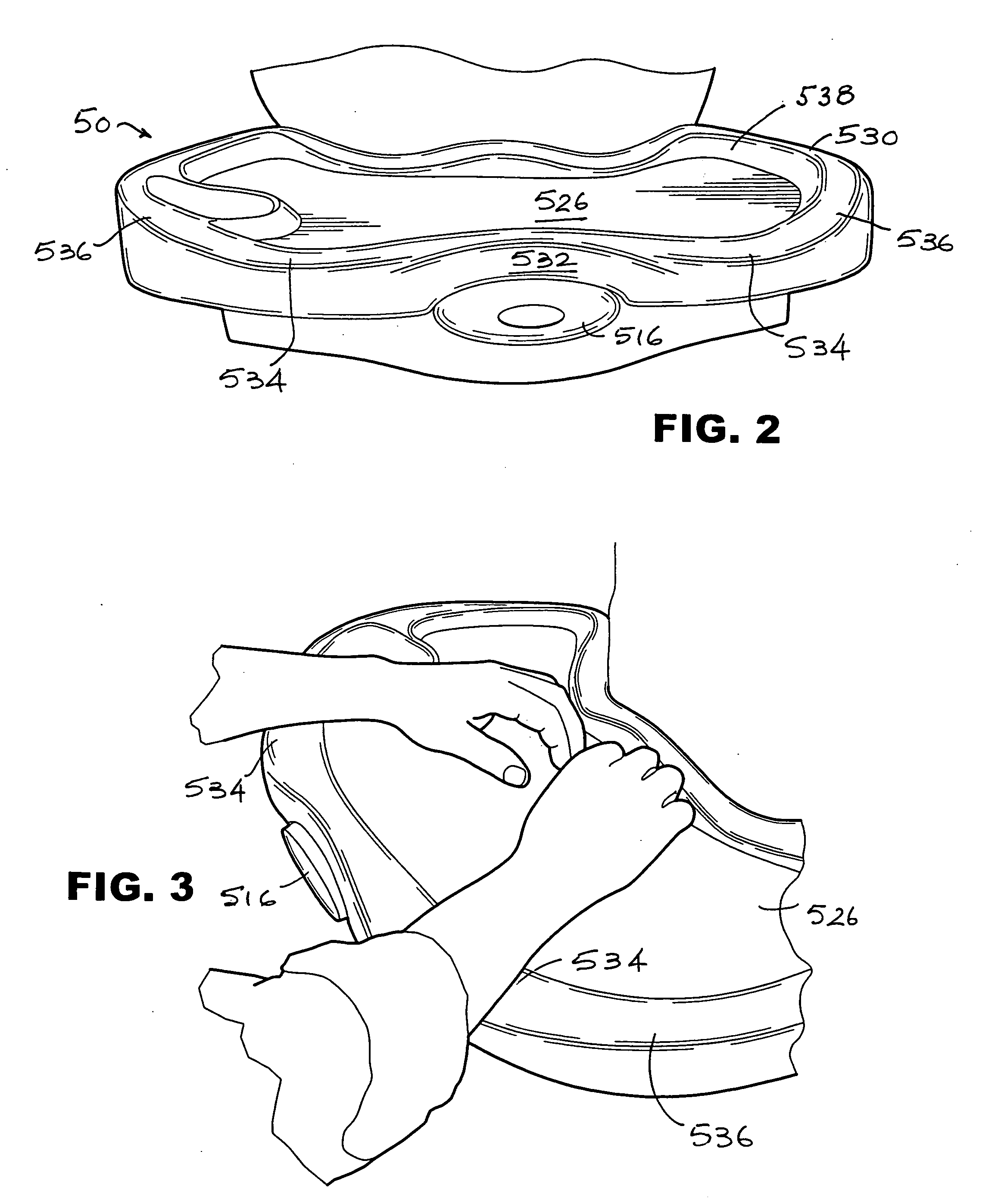

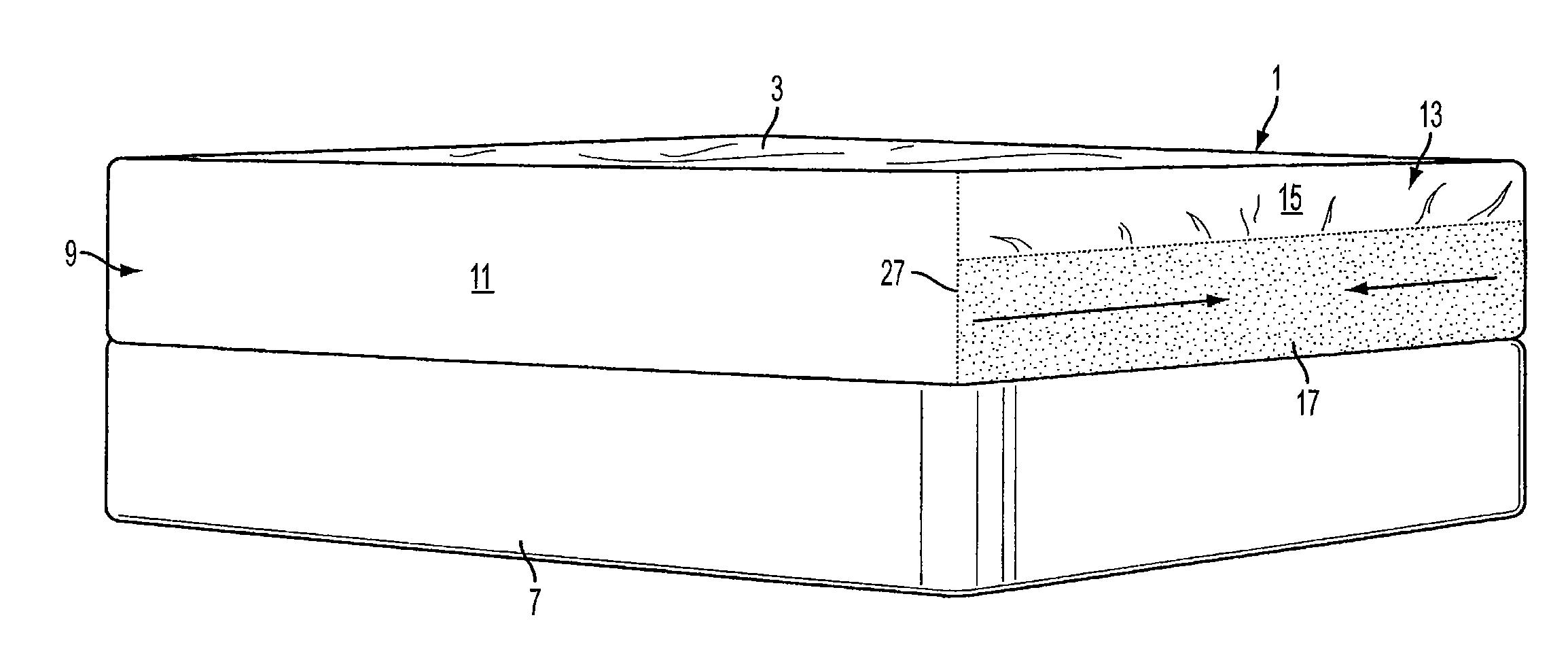

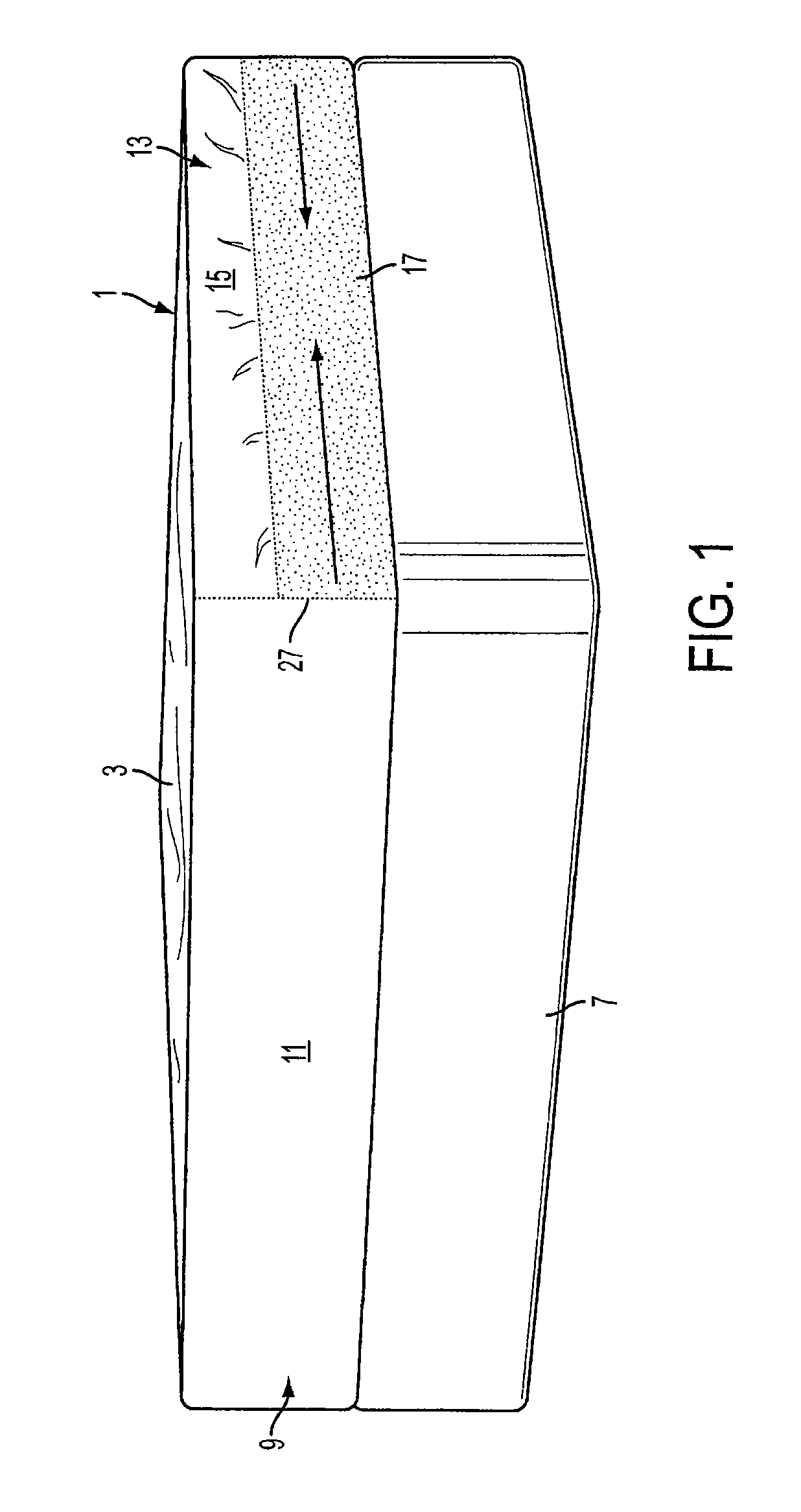

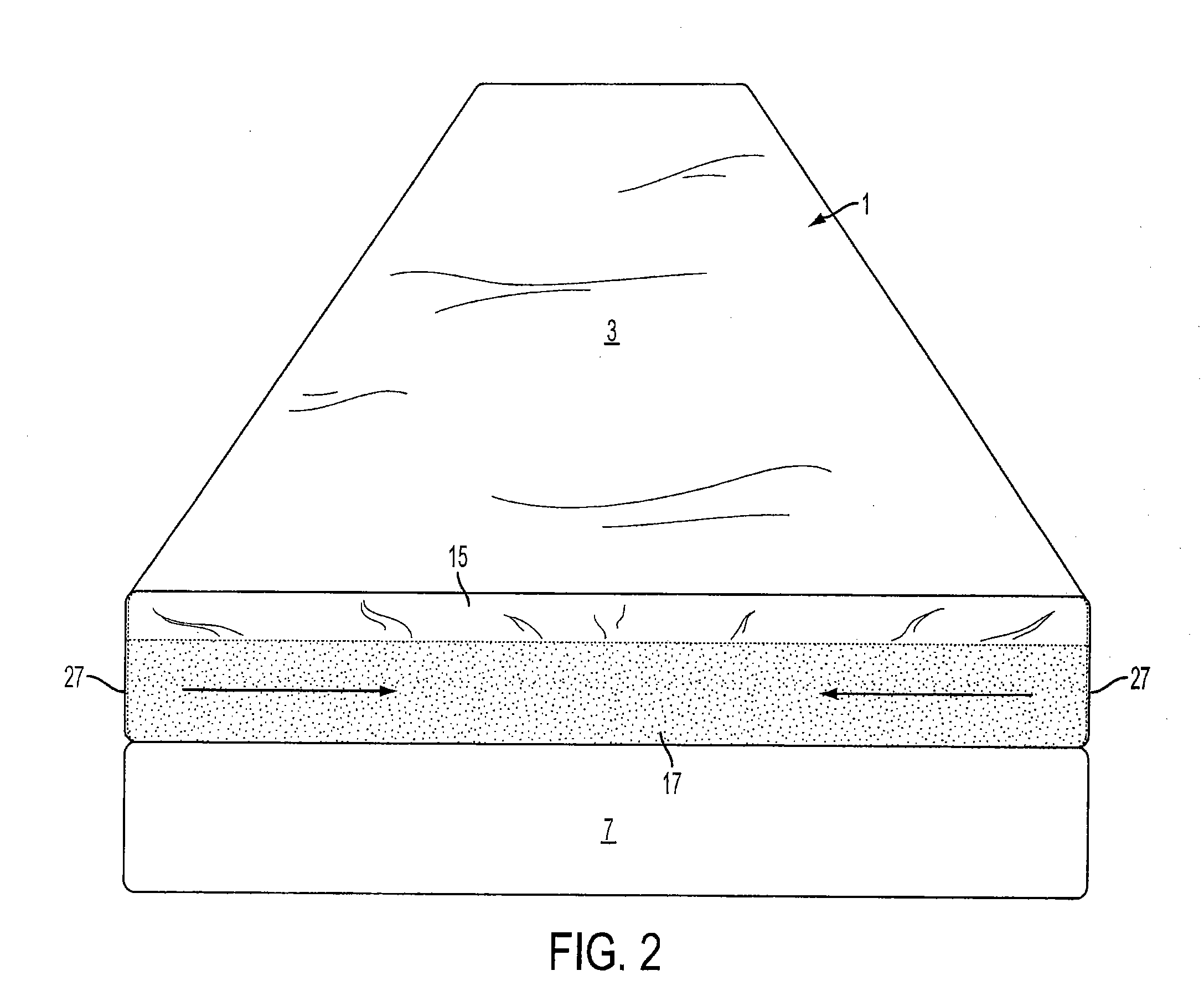

Mattress cover with fit enhancing composite end panels

A fitted mattress cover for enveloping the top, side and end surfaces of a mattress is constructed to accommodate a range of mattress peripheral sizes and thicknesses. The construction utilizes composite end panels which include stretch end panels covering lower partial portions of the mattress end surfaces and which impart recovery forces to effectively grip the mattress and thereby minimize the shifting of the cover relative to the mattress. At the same time, the look and feel of the mattress covering, which may be of importance especially in the case of a fitted sheet, is improved, by virtue of the fact that the side panels can be formed as uninterrupted unitary extensions of the material forming the top side panel, or other material based upon aesthetic considerations, as can upper partial portions (extension end panels) of the composite end panels. In a related aspect, stretchability of the mattress cover skirt may be imparted in a post-manufacture heat treatment finishing step, which may included a laundry wash and dry cycle.

Owner:LOUISVILLE BEDDING CO INC

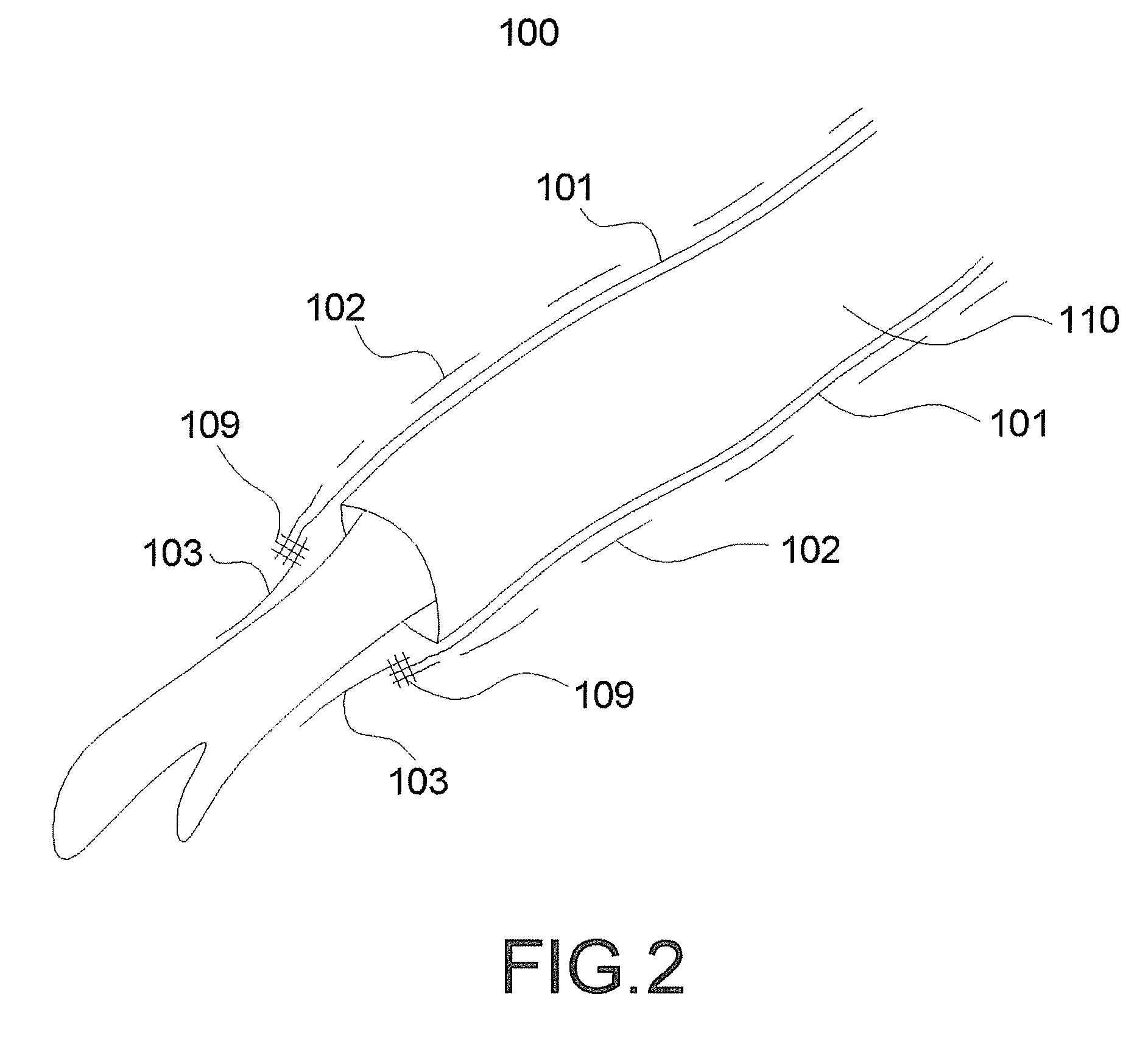

Packages for medical devices and methods therefor

ActiveUS20120061262A1Minimizes shiftingShorter pouch lengthSuture equipmentsSurgical furnitureMedical deviceBiomedical engineering

A package for a medical device having a handle and an elongated shaft. The package includes a holster for holding the medical device, the holster having a tubular member for receiving the elongated shaft and a handle cover located at a proximal end thereof. The handle cover has a holster opening for accessing the handle to draw the medical device from the holster. The package includes a pouch having a sealed area bounded by a top sealed edge, a bottom sealed edge, a pair of side sealed edges extending between the top and bottom sealed edges, and at least one opening tab spaced from the bottom sealed edge. The medical device and the holster are disposed within the sealed area of the pouch with the elongated shaft of the medical device extending along the bottom sealed edge and the holster opening being located adjacent the at least one opening tab.

Owner:ETHICON INC

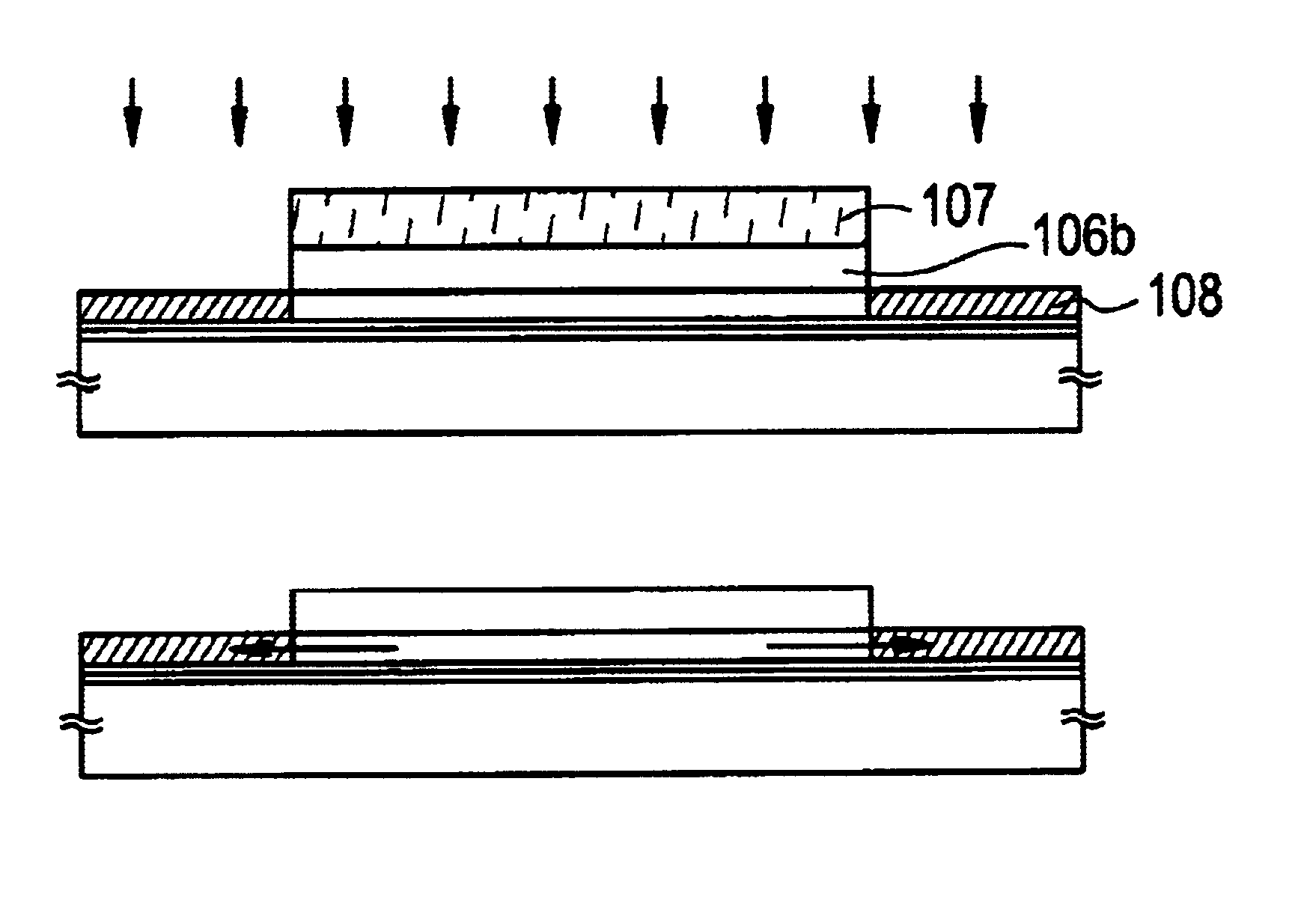

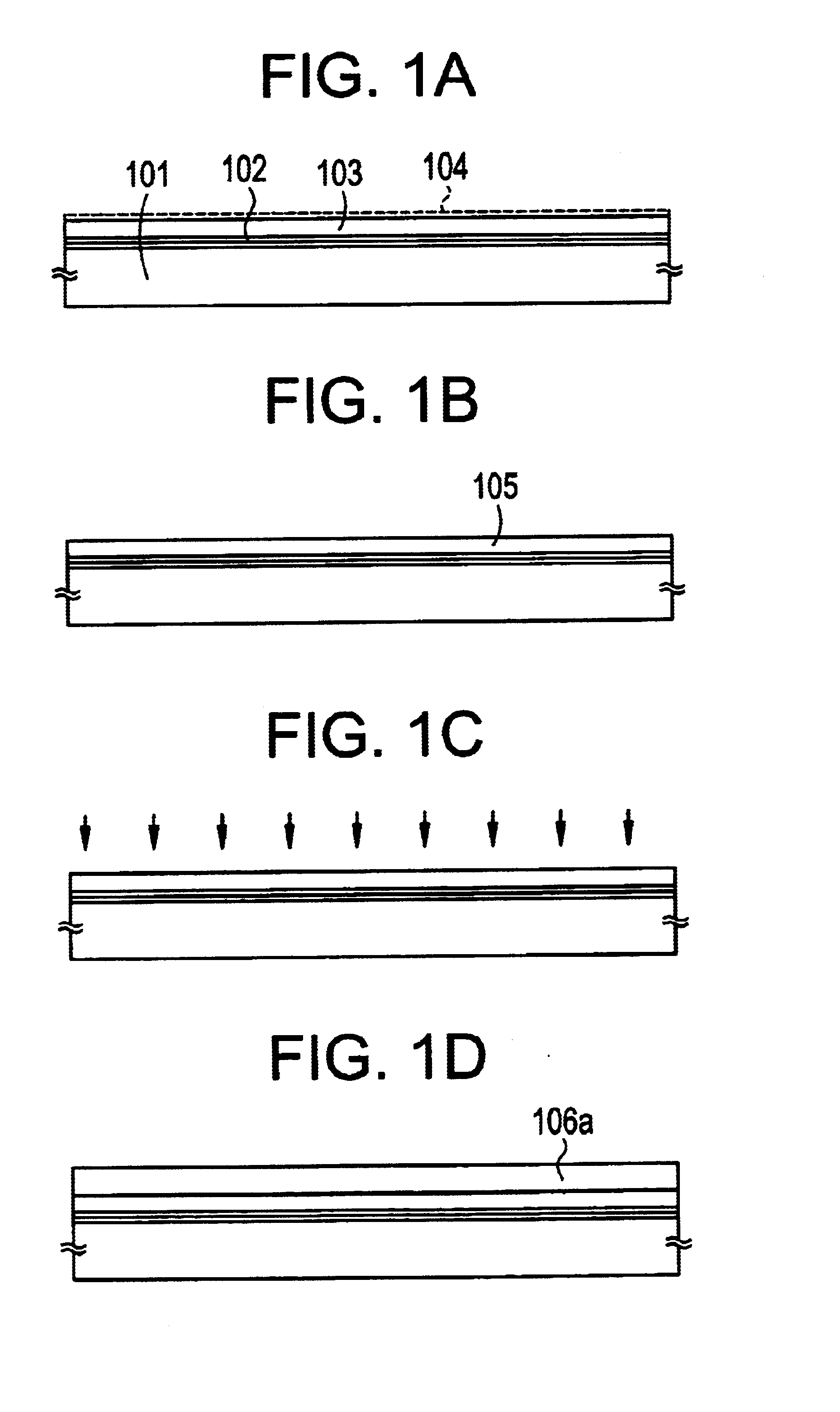

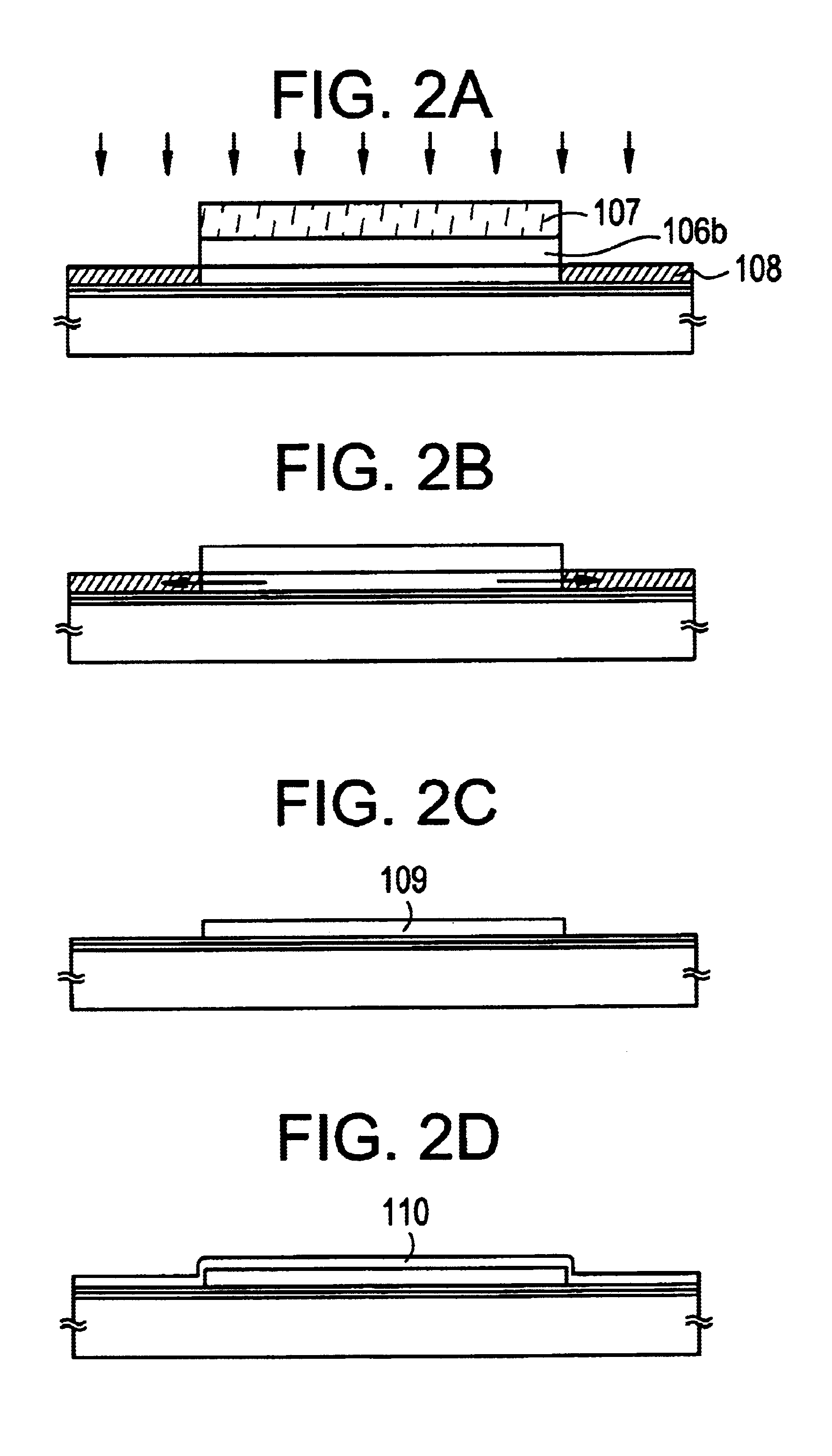

Method of manufacturing semiconductor device

InactiveUS6858480B2Simple processImprove throughputTransistorSolid-state devicesNoble gasCrystal structure

According to the present invention, an impurity region, to which a rare gas element (also called a rare gas) and one kind or a plurality of kinds of elements selected from the group consisting of H, H2, O, O2, and P are added, are formed in a semiconductor film having a crystalline structure, using a mask, and gettering for segregating a metal element contained in the semiconductor film to the impurity region by heat treatment. Thereafter, pattering is conducted using the mask, whereby a semiconductor layer made of the semiconductor film having a crystalline structure is formed.

Owner:SEMICON ENERGY LAB CO LTD

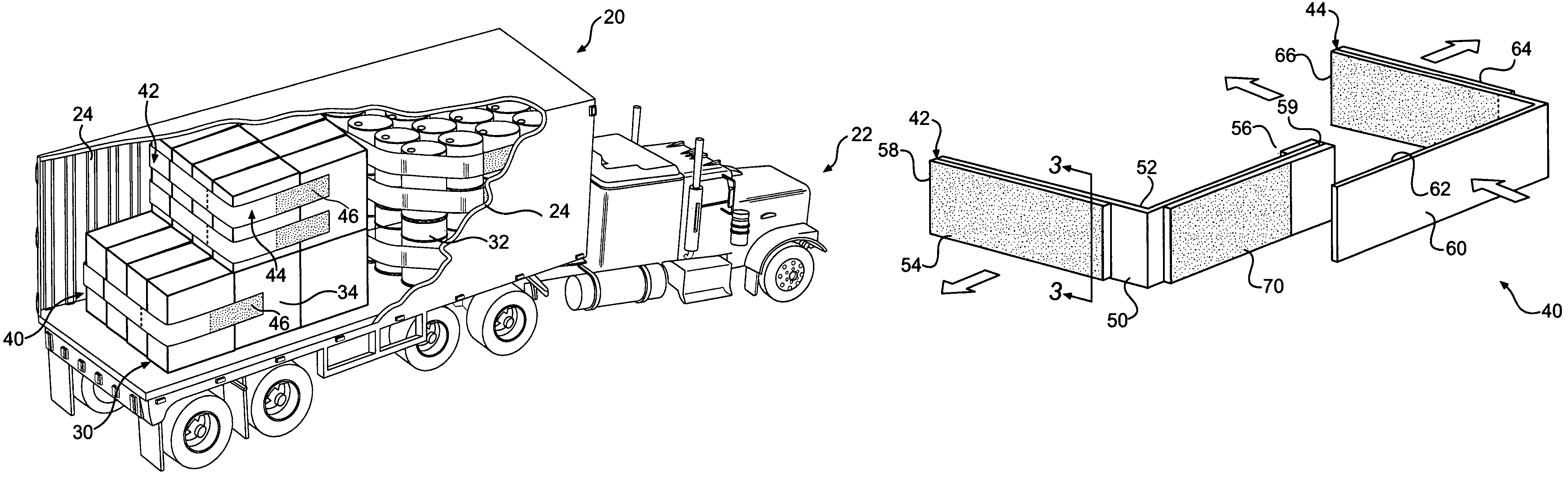

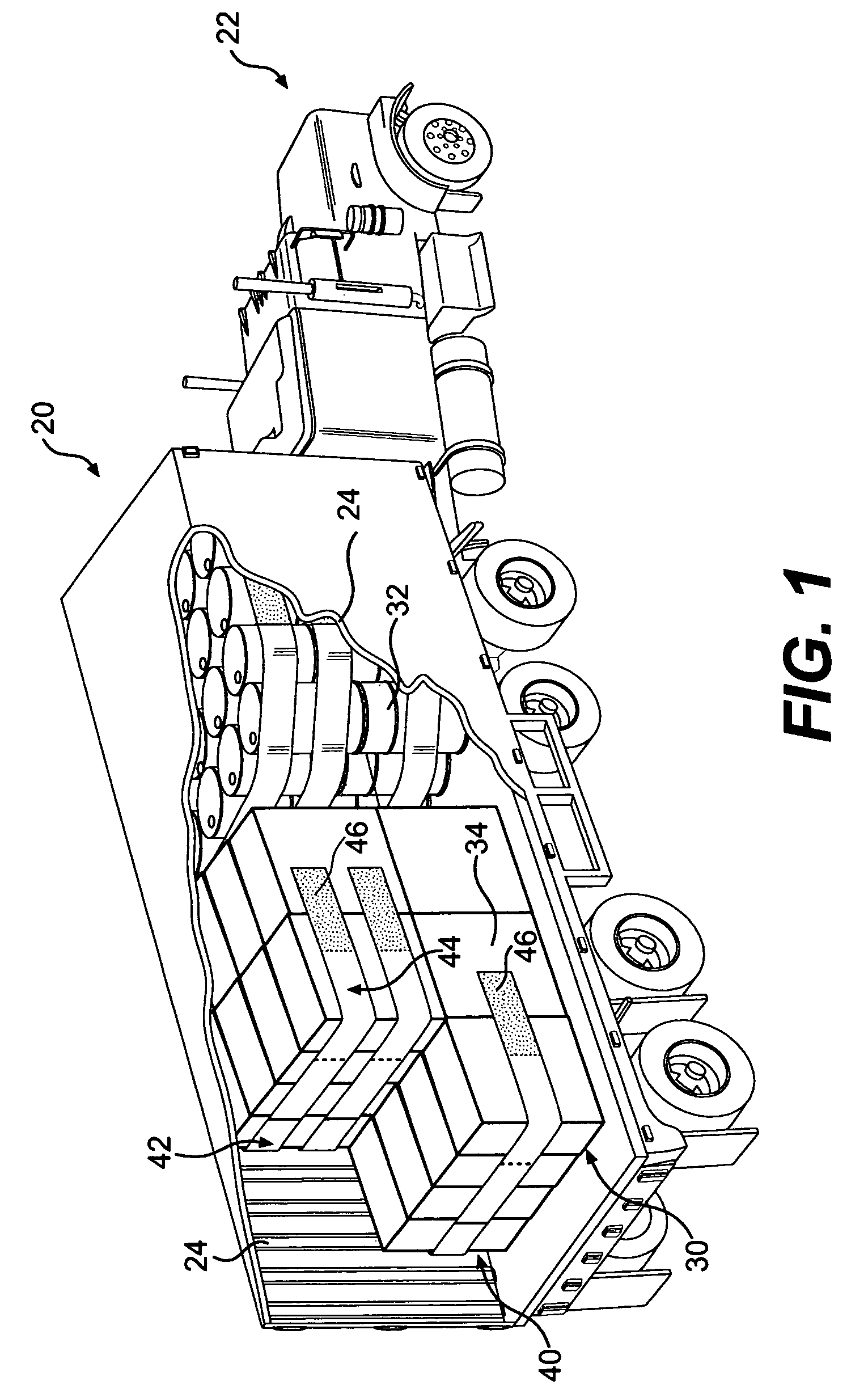

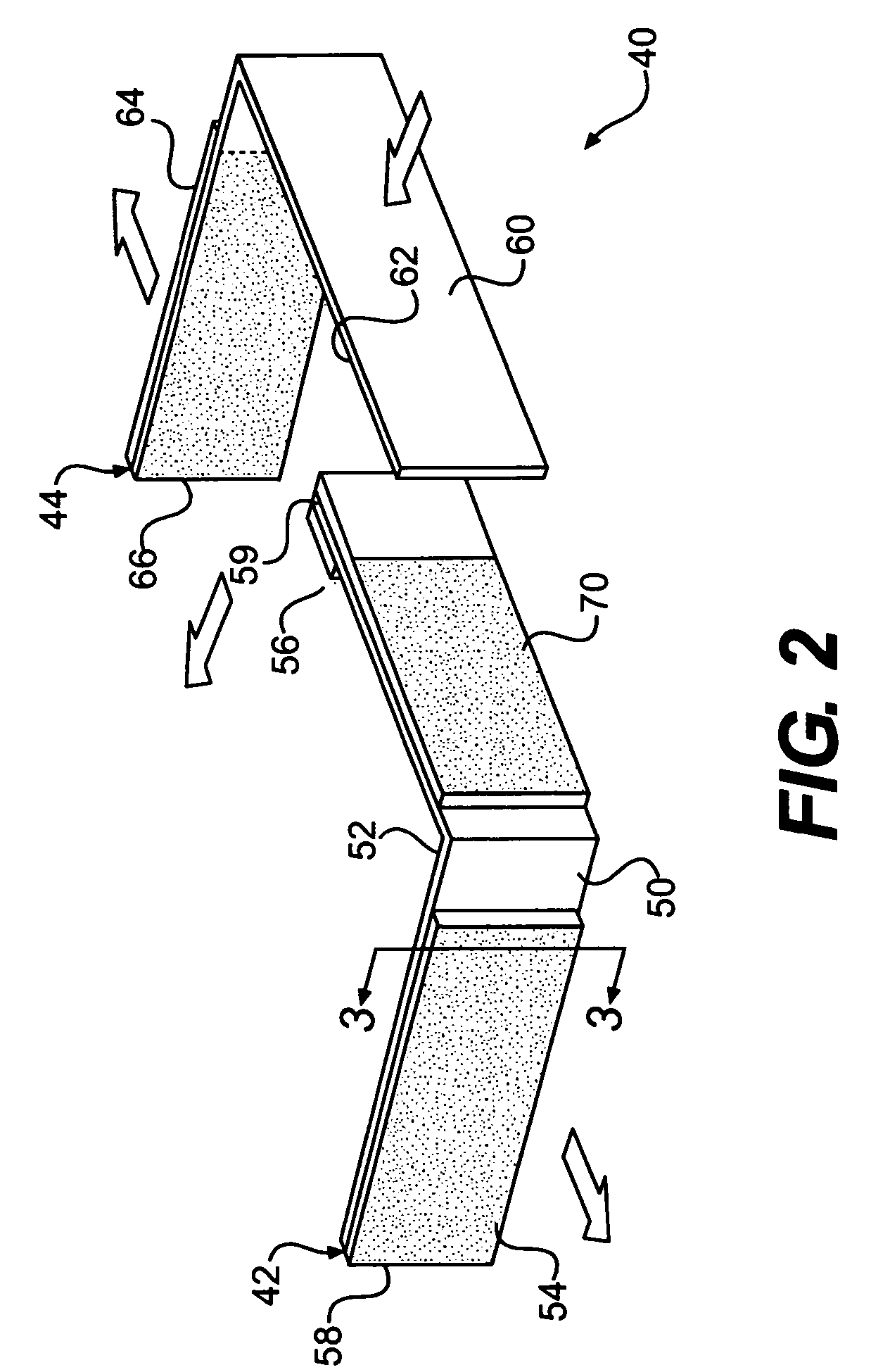

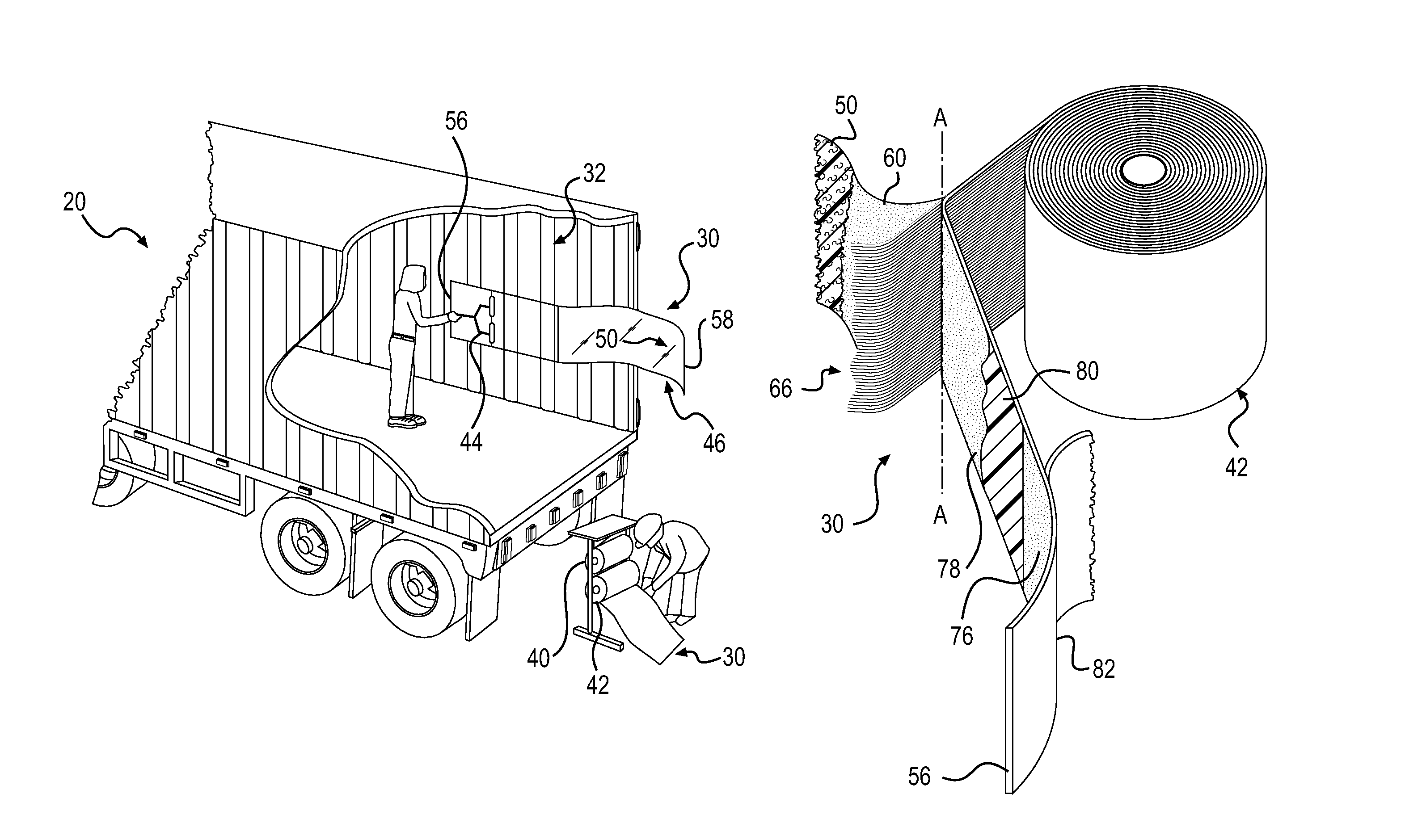

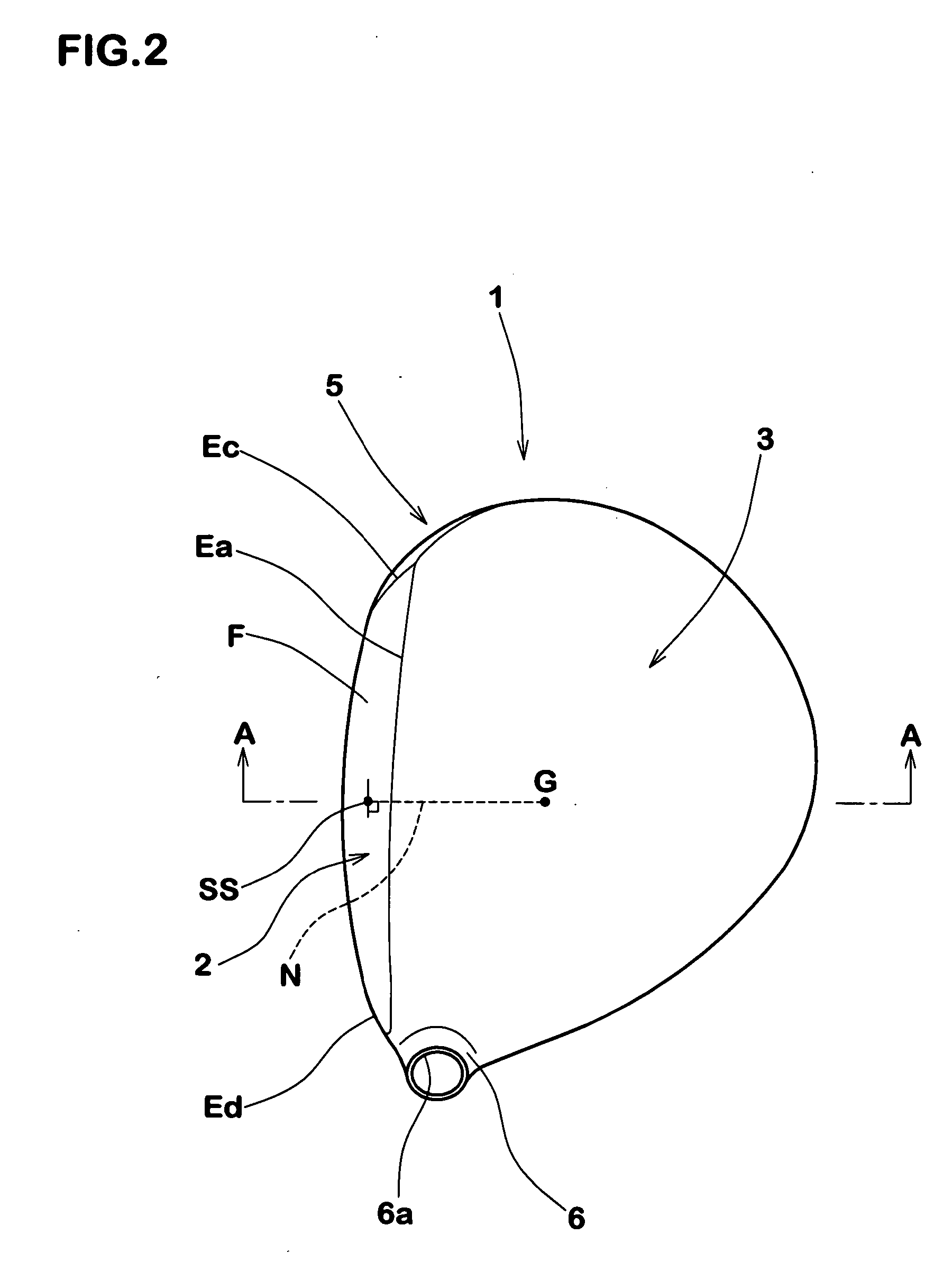

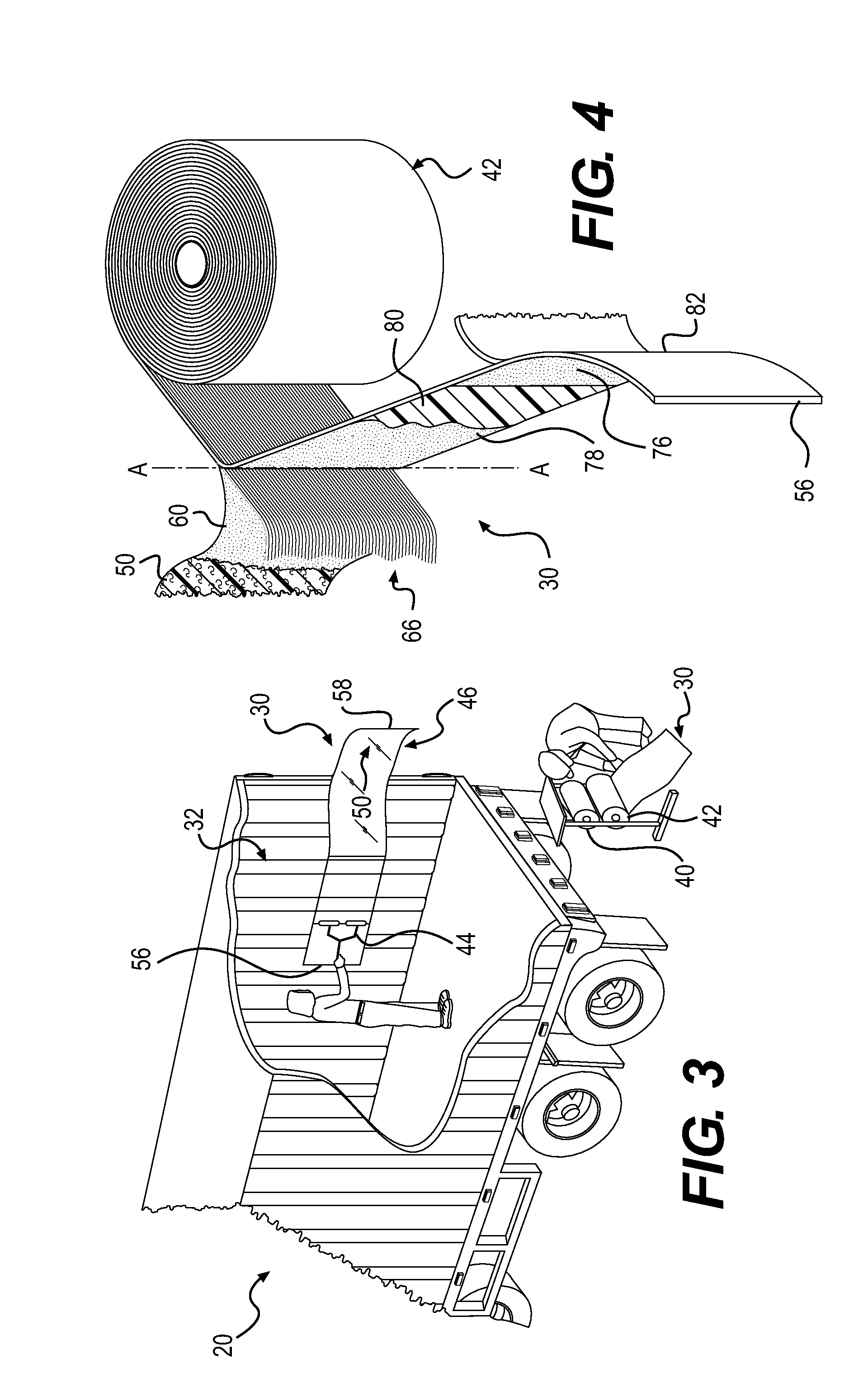

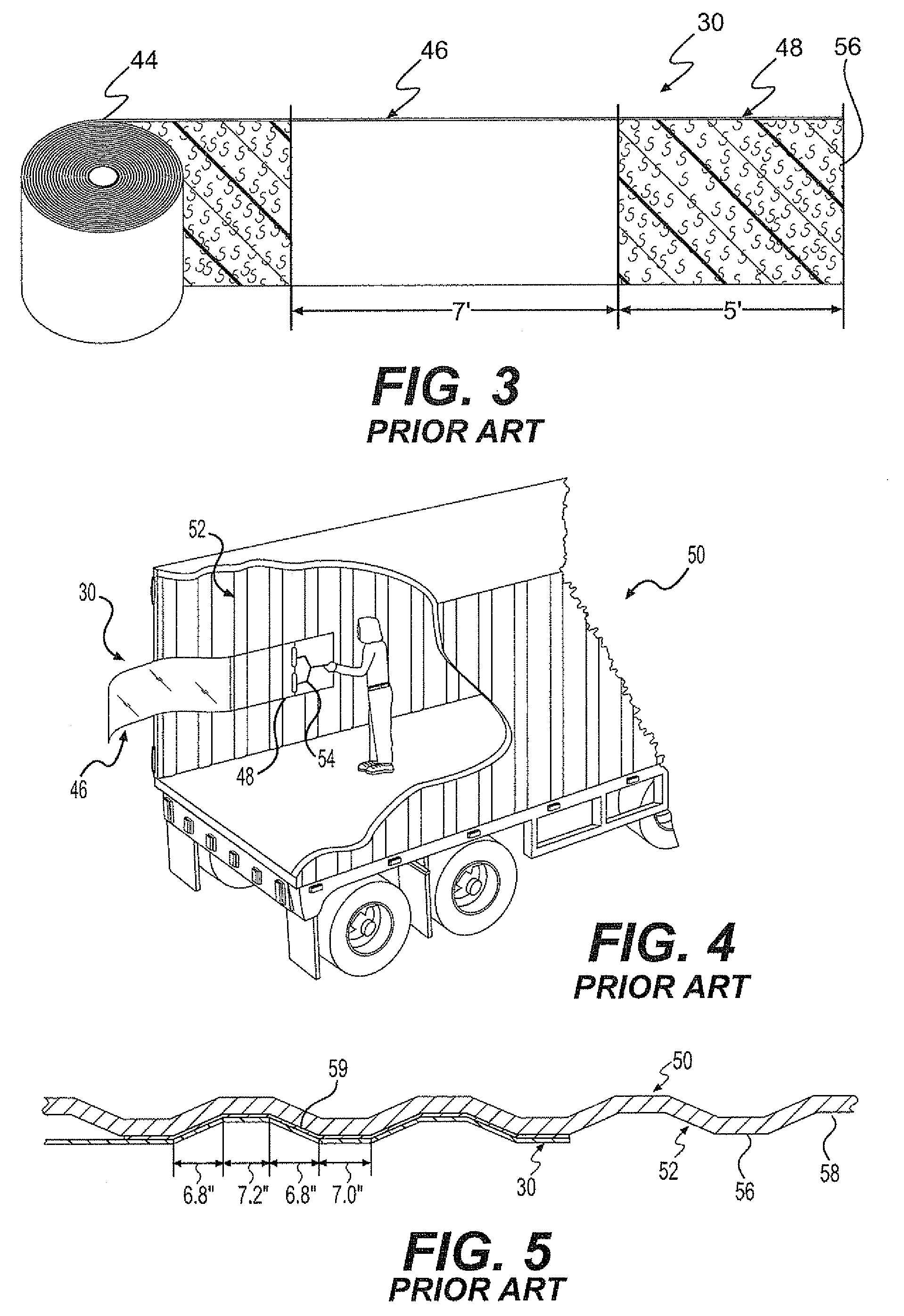

Overland cargo restraint system and method

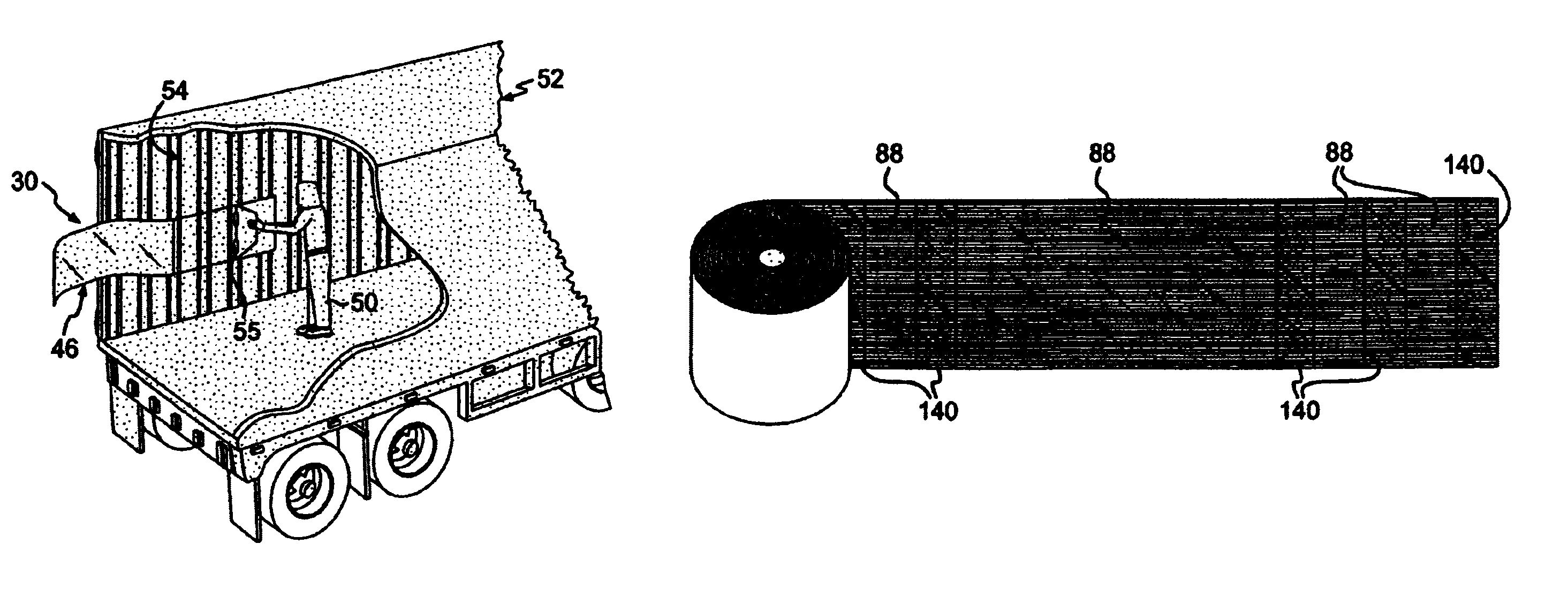

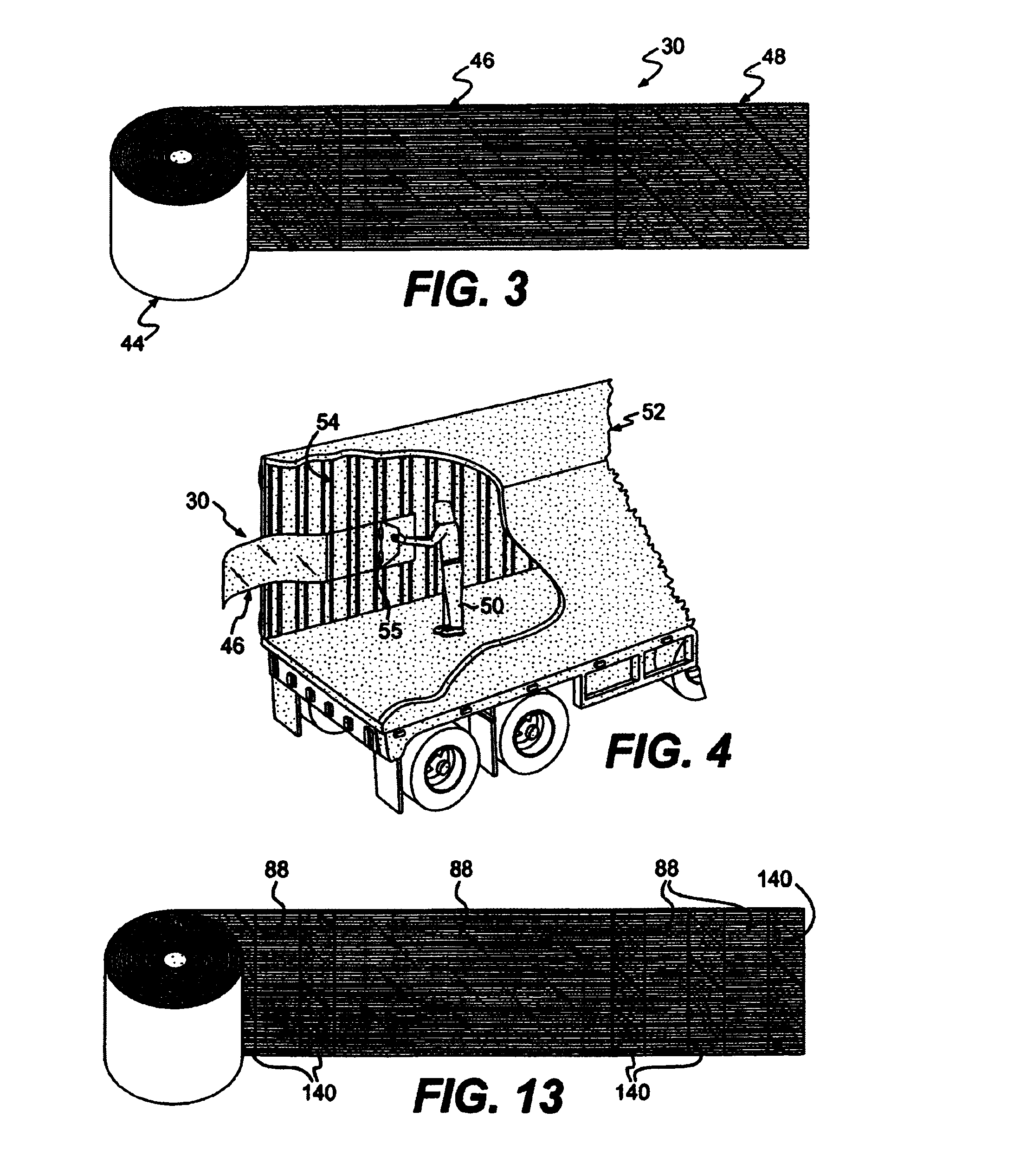

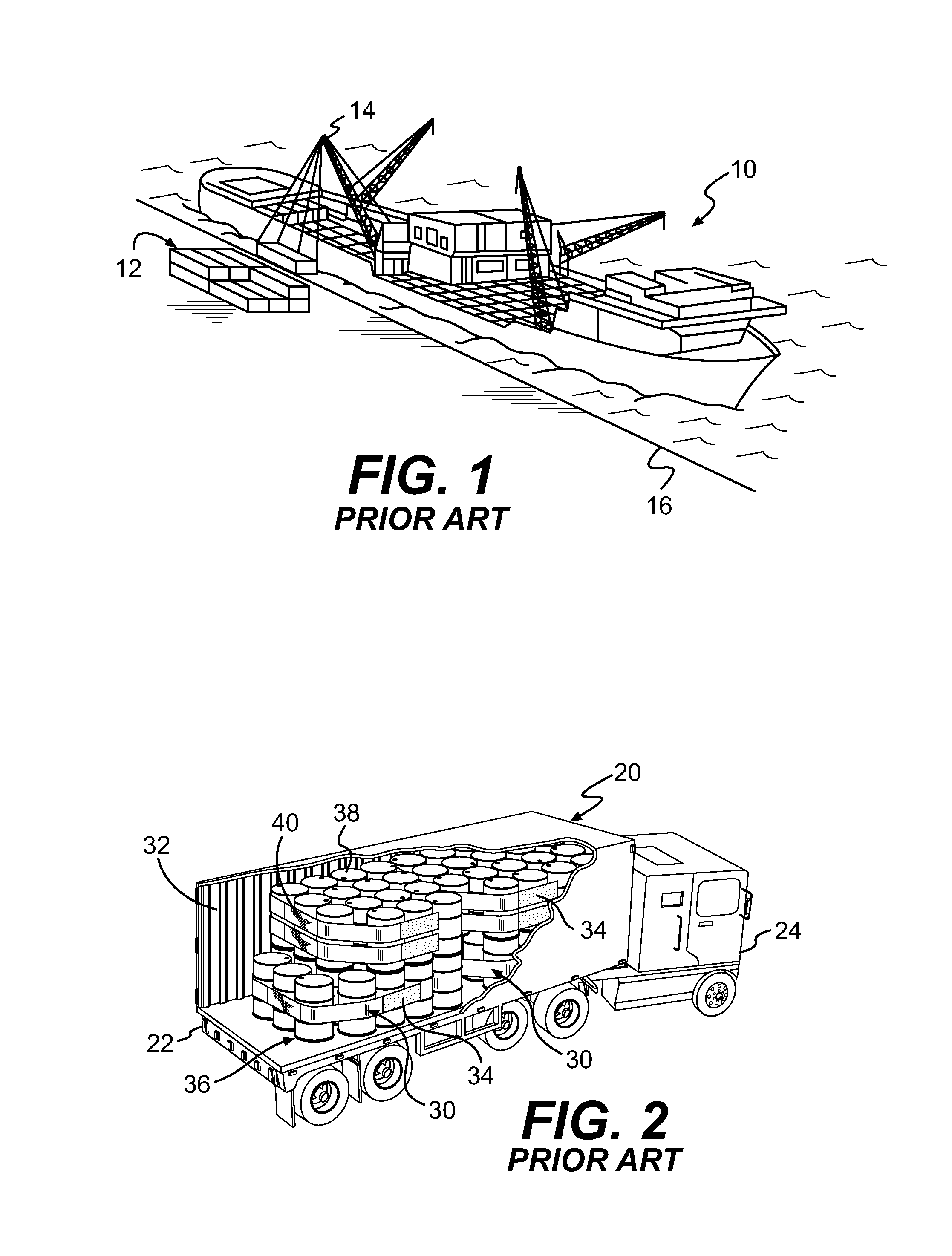

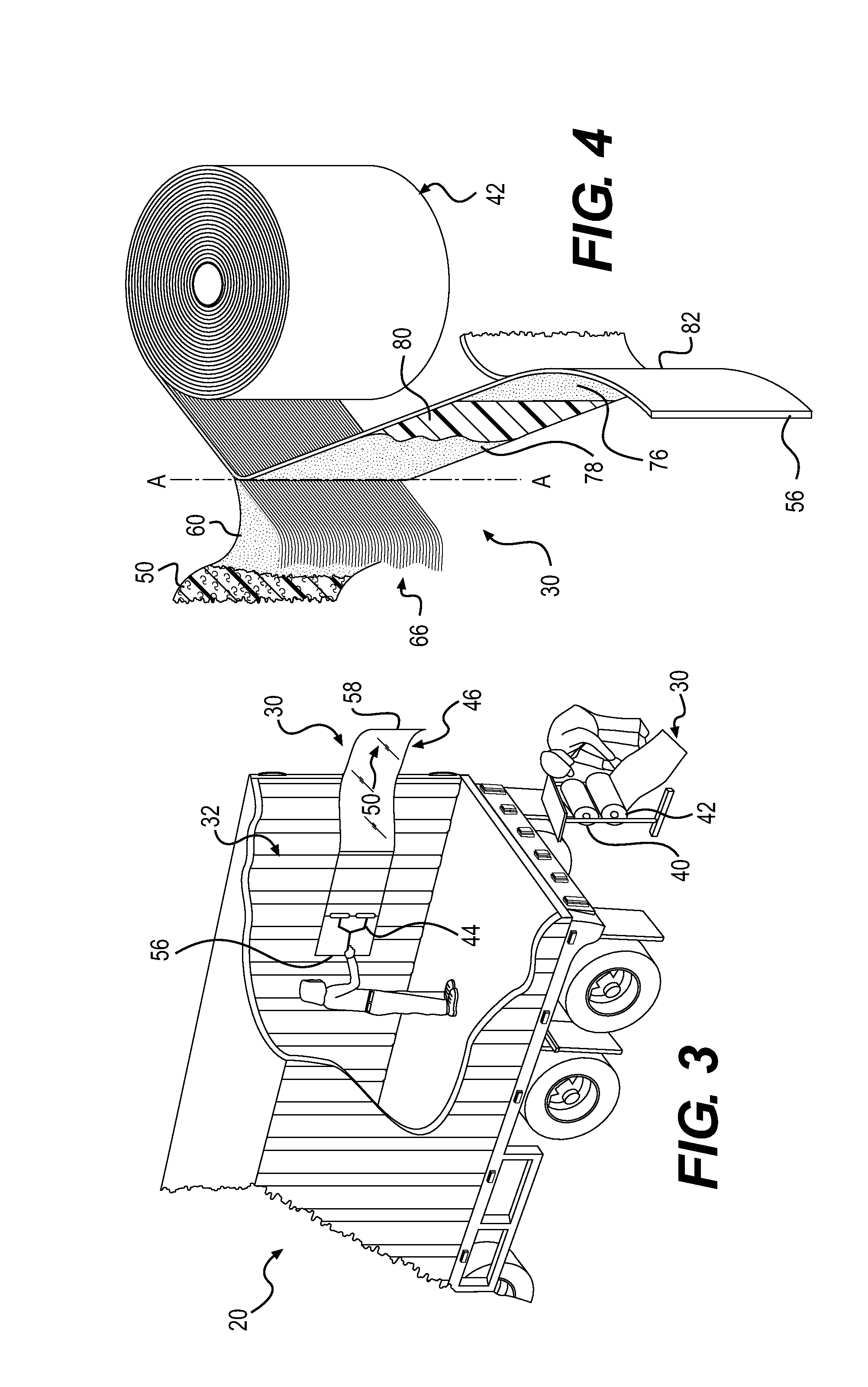

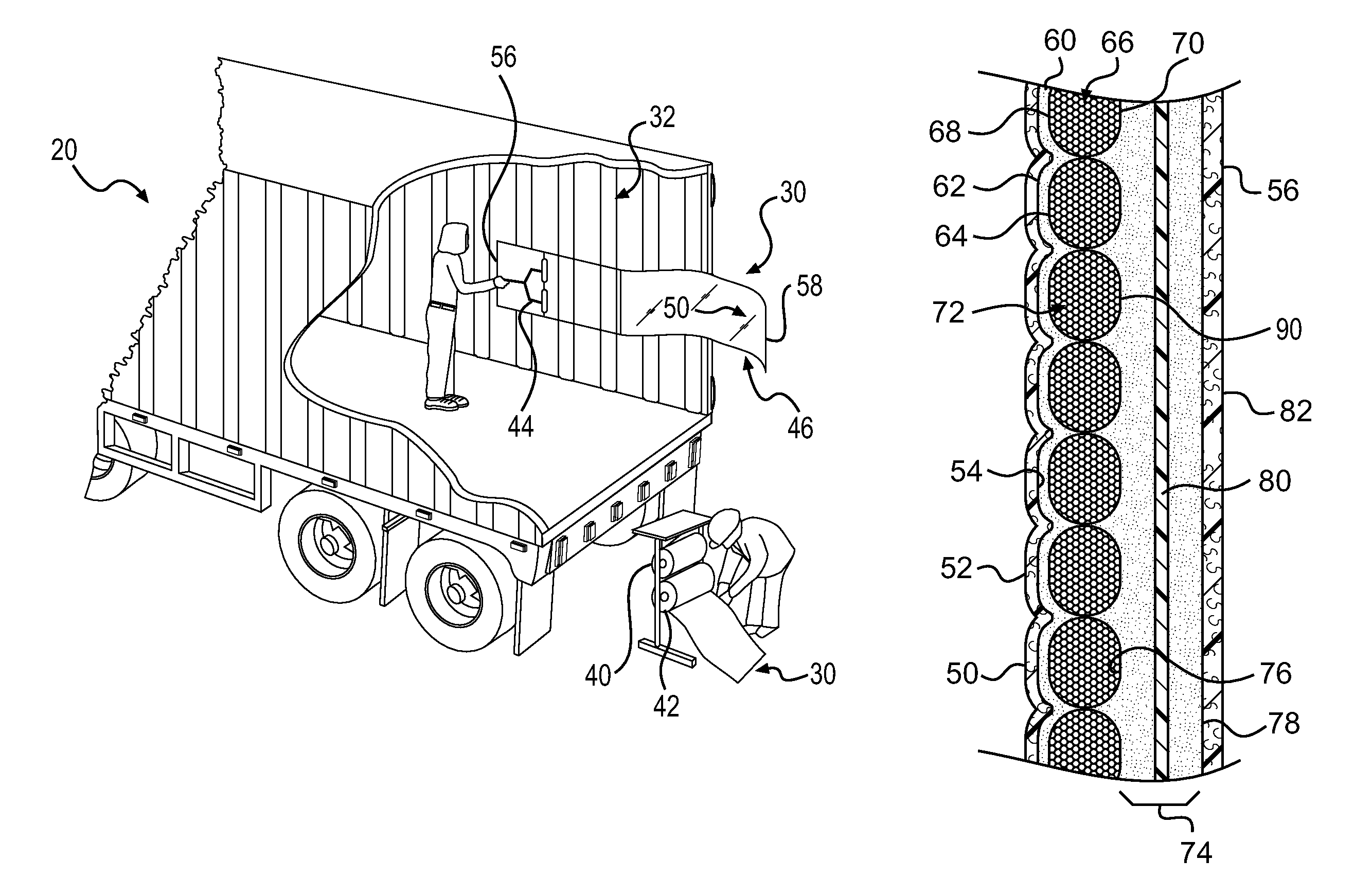

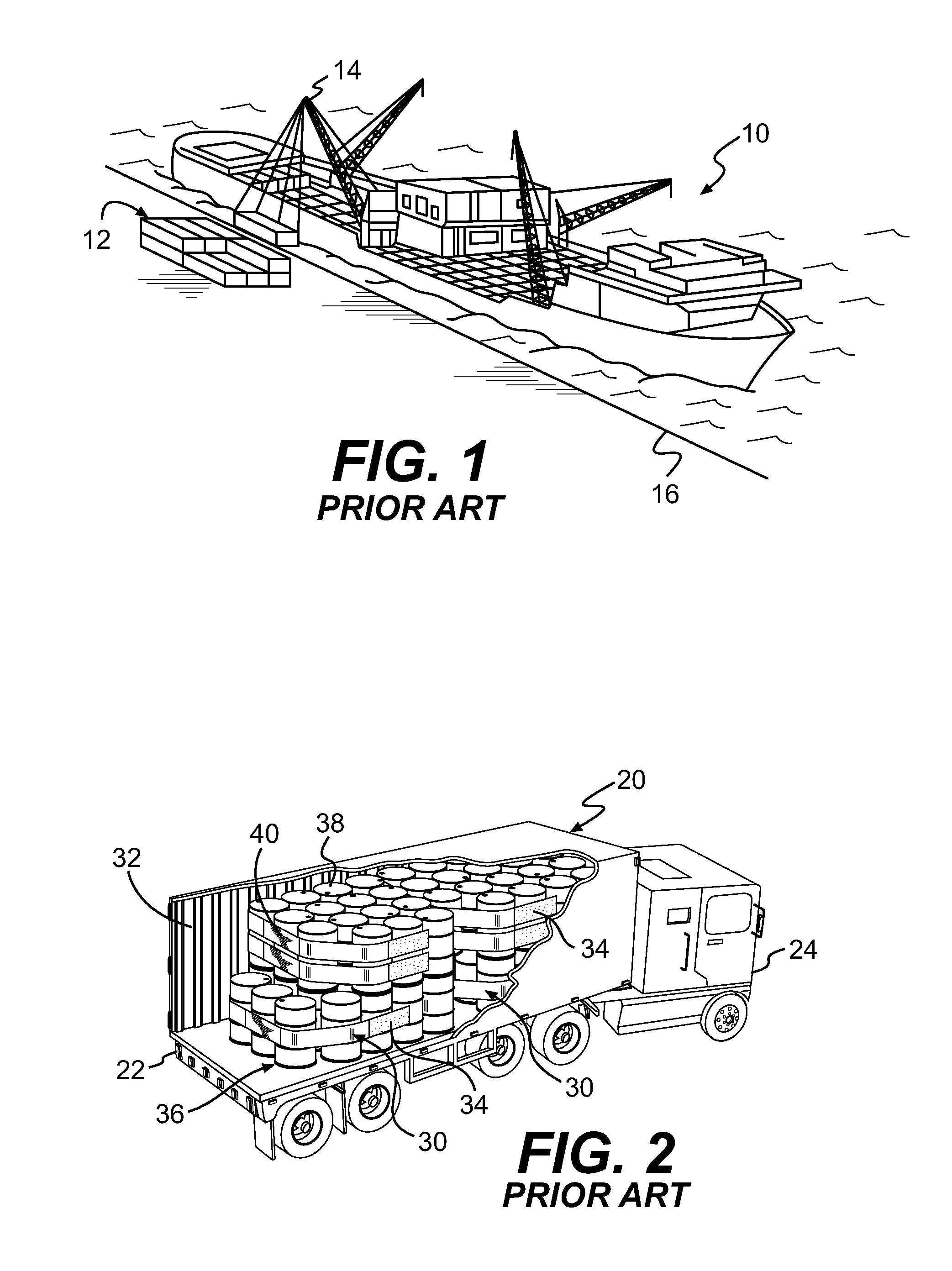

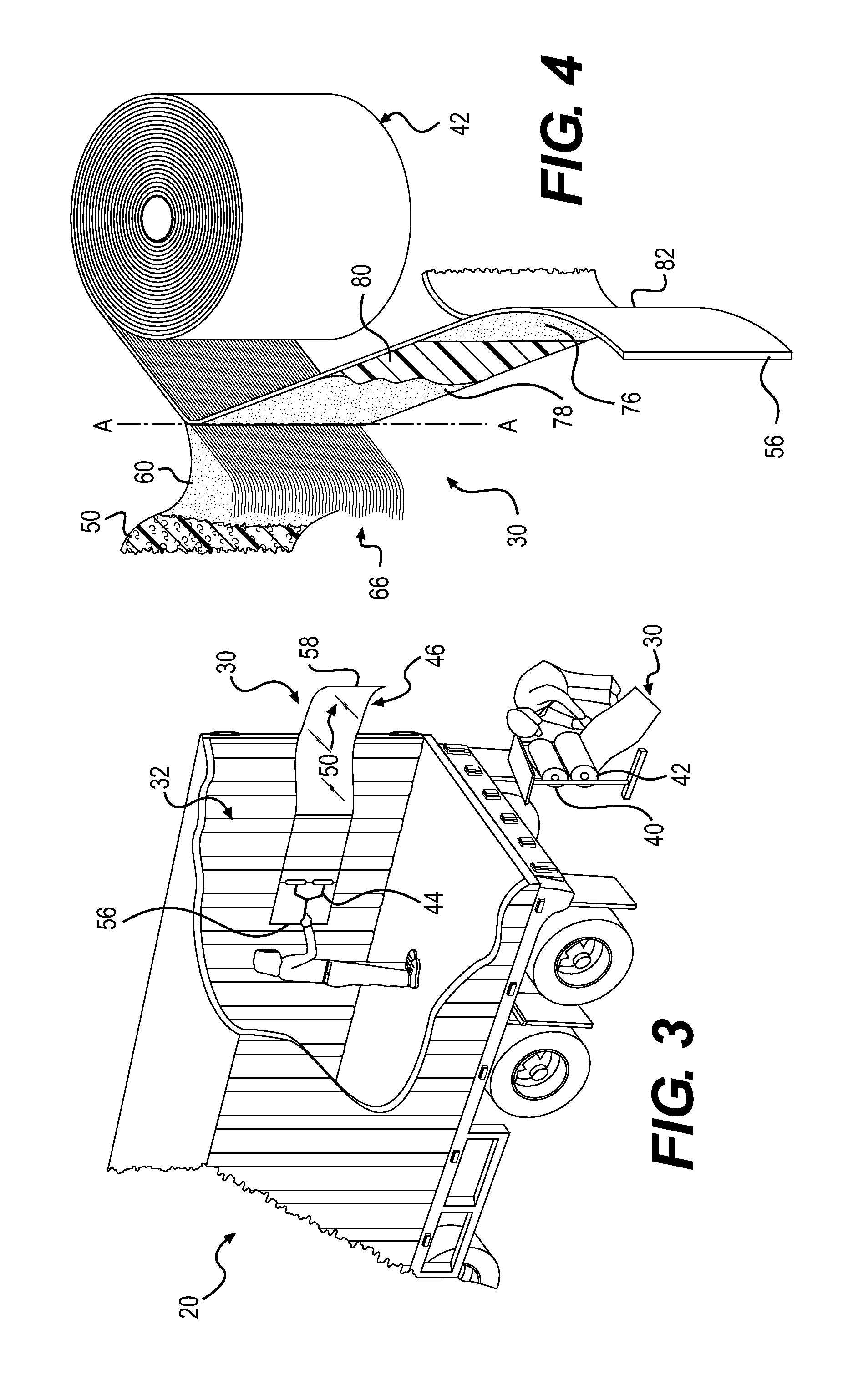

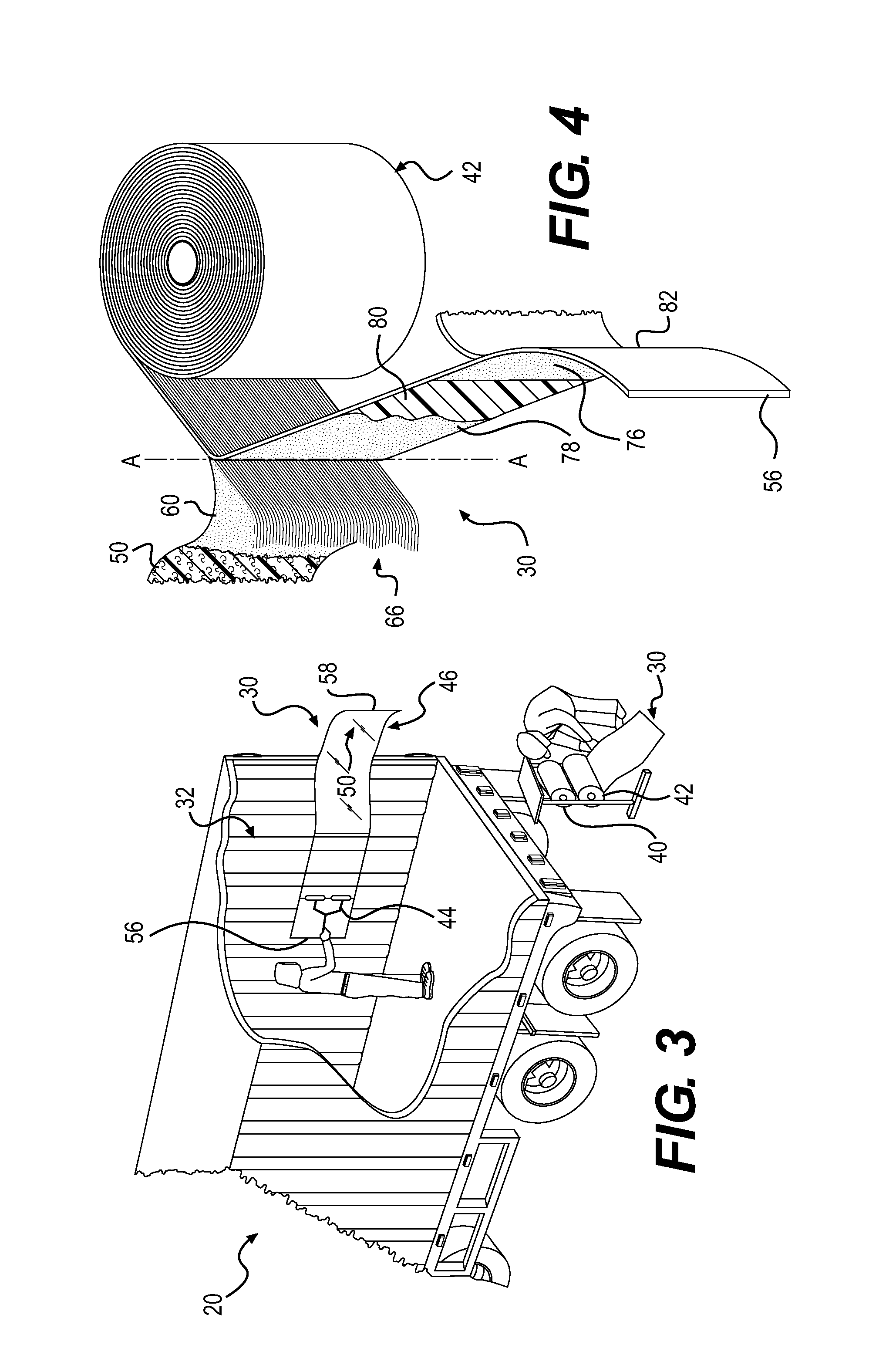

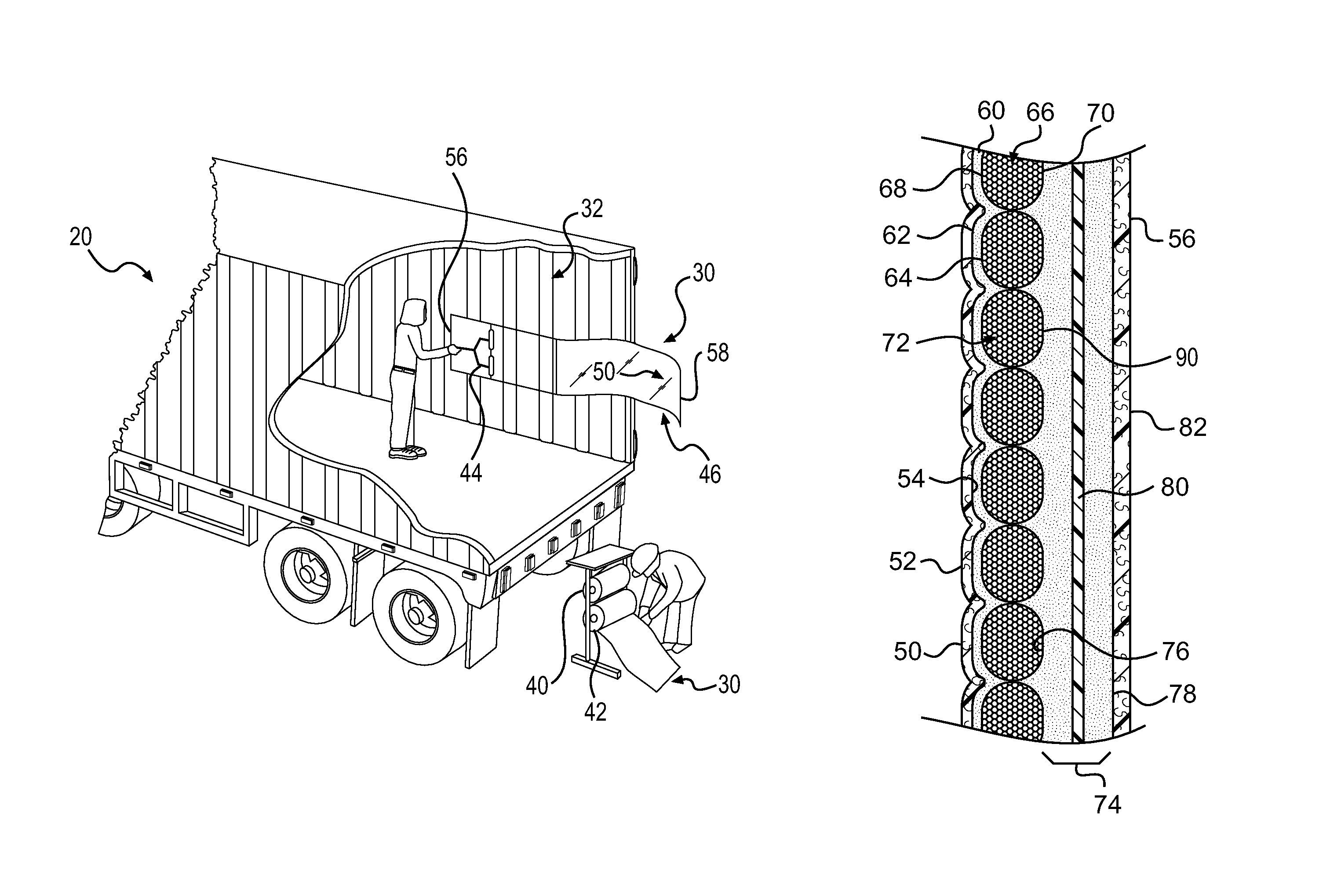

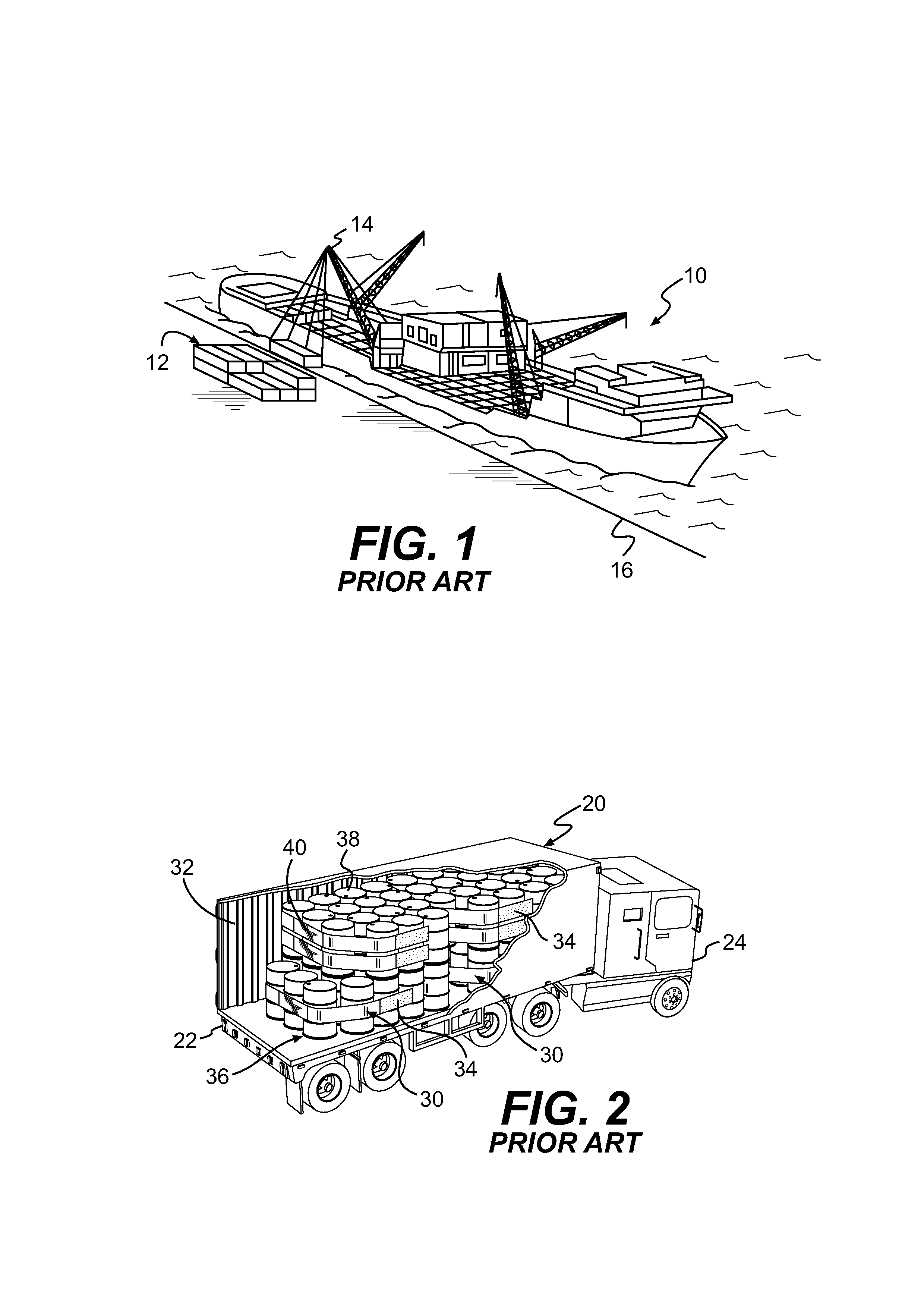

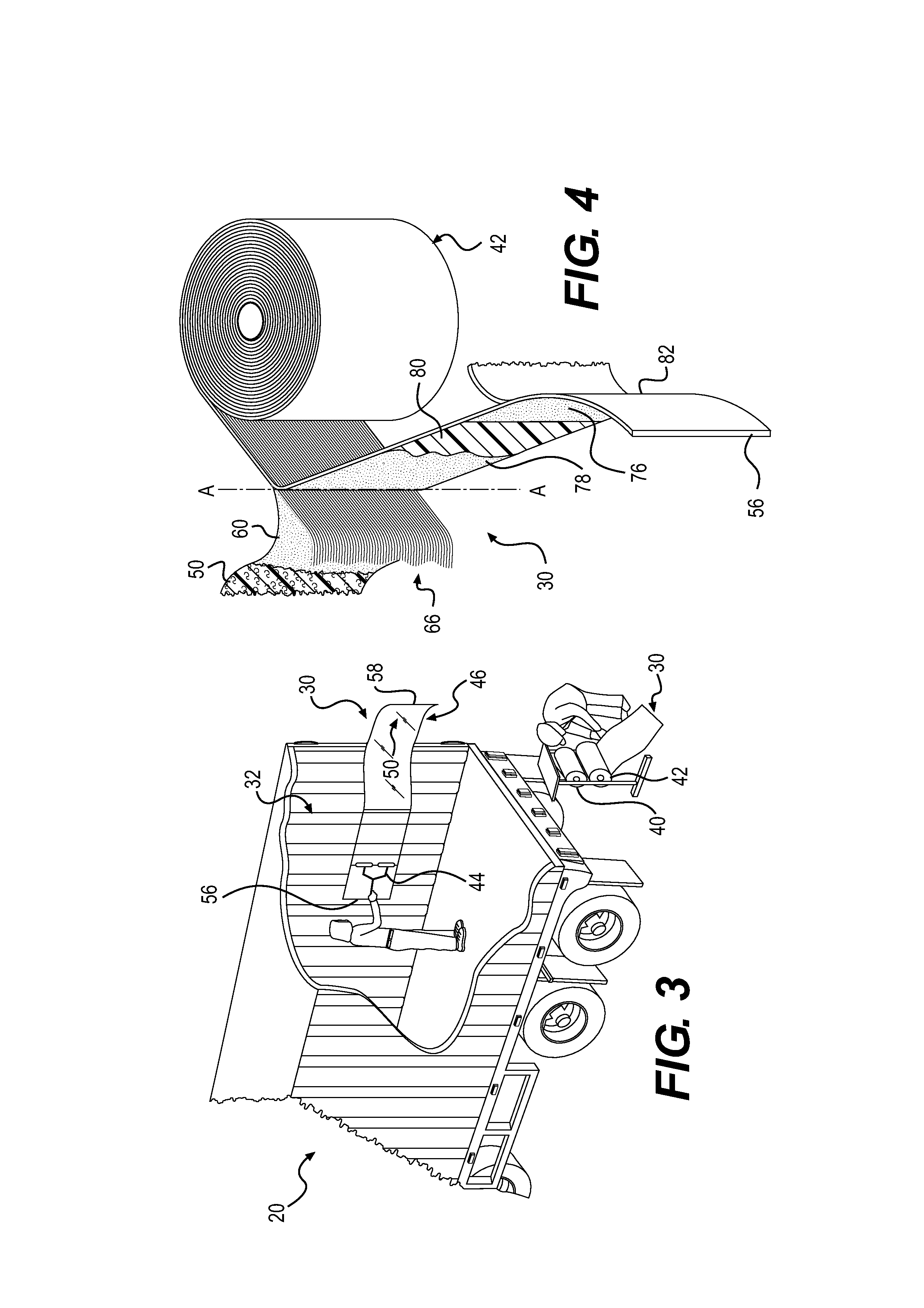

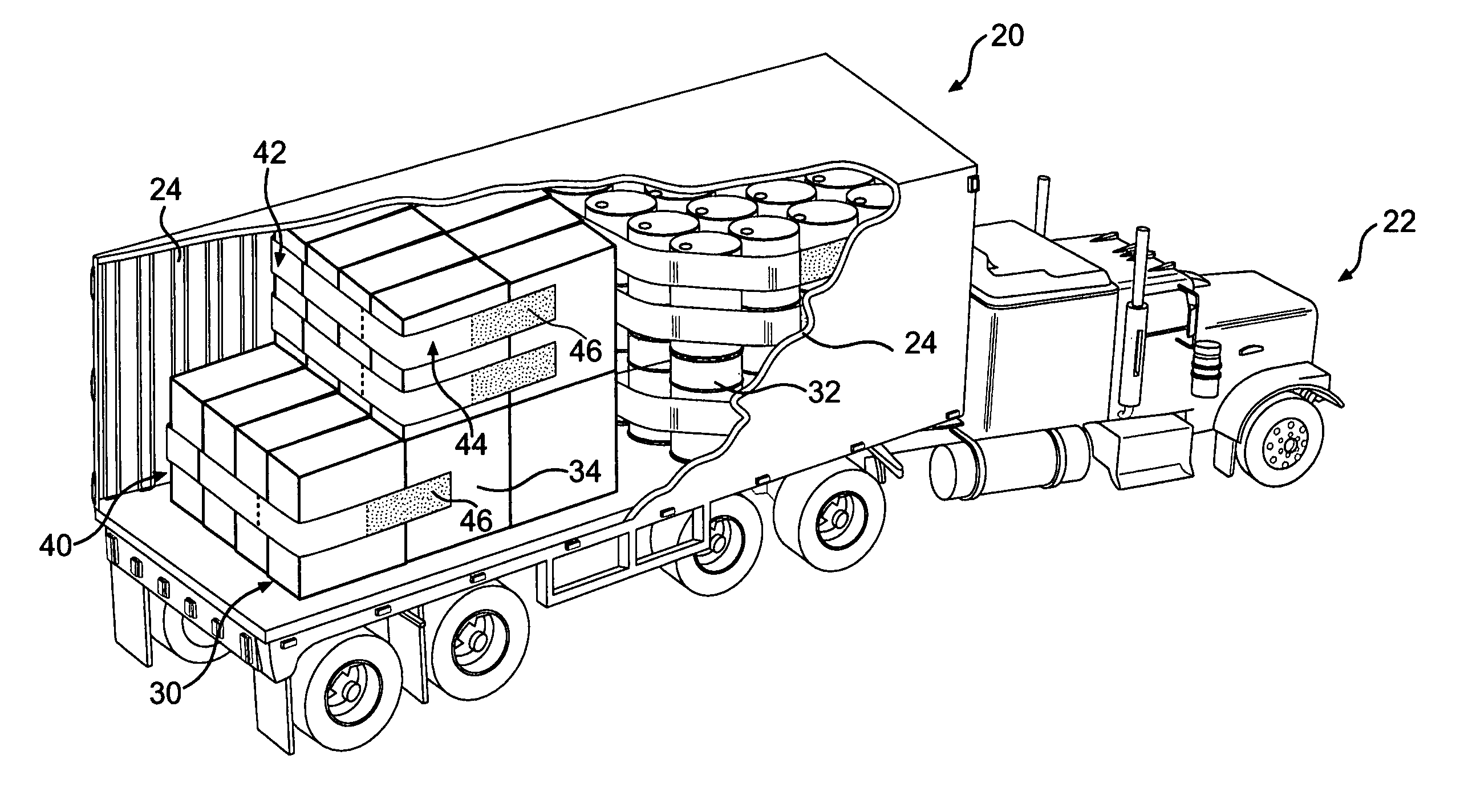

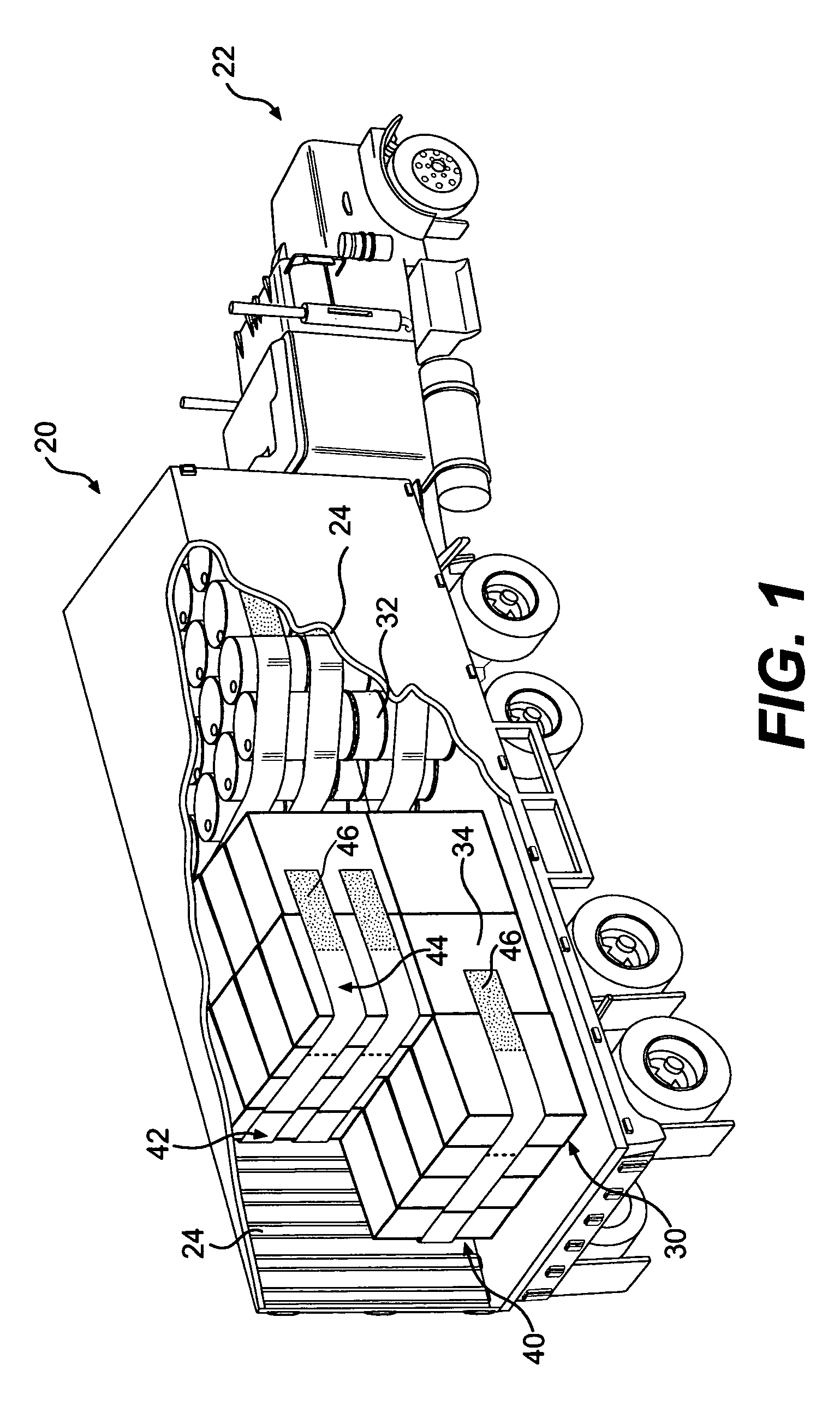

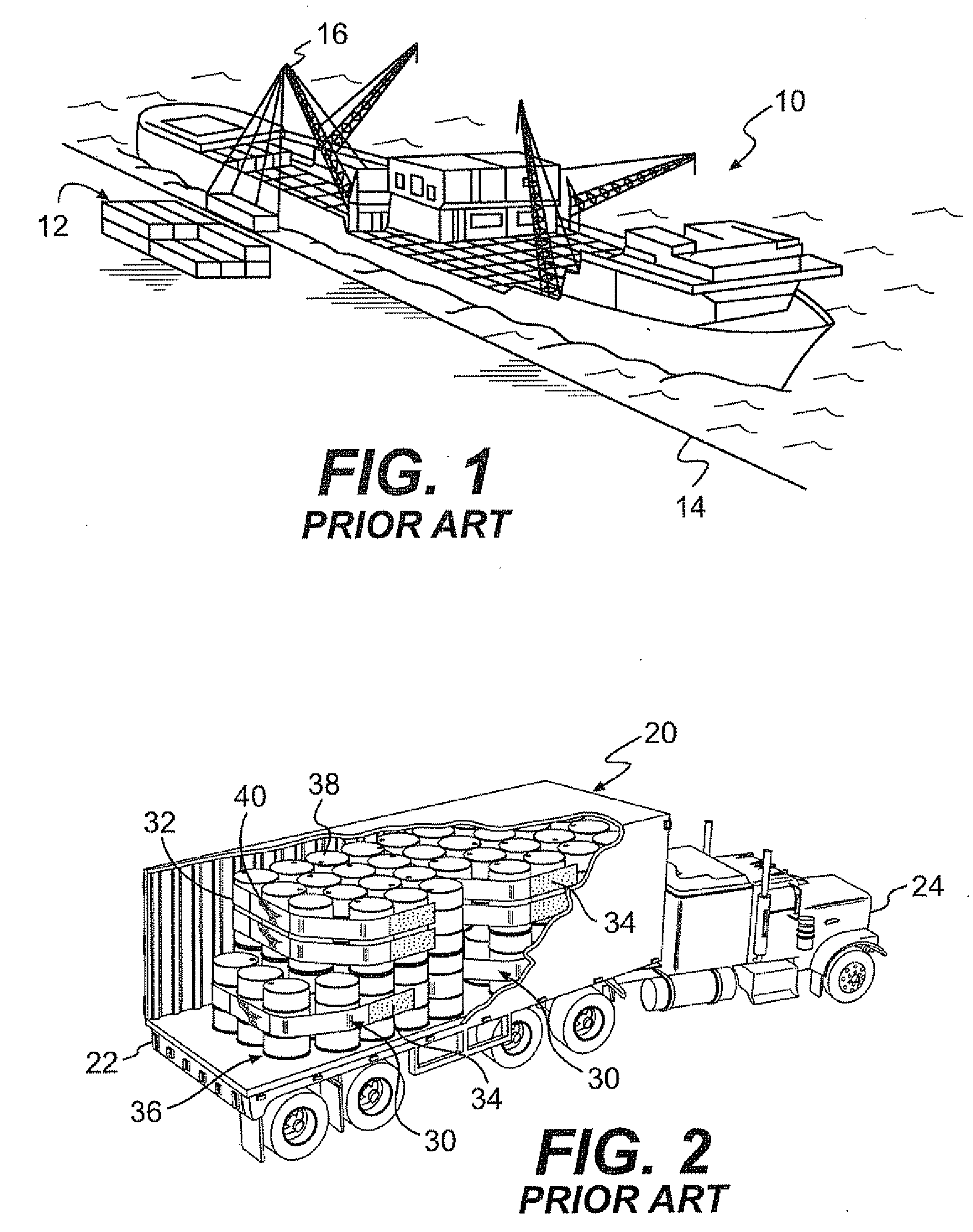

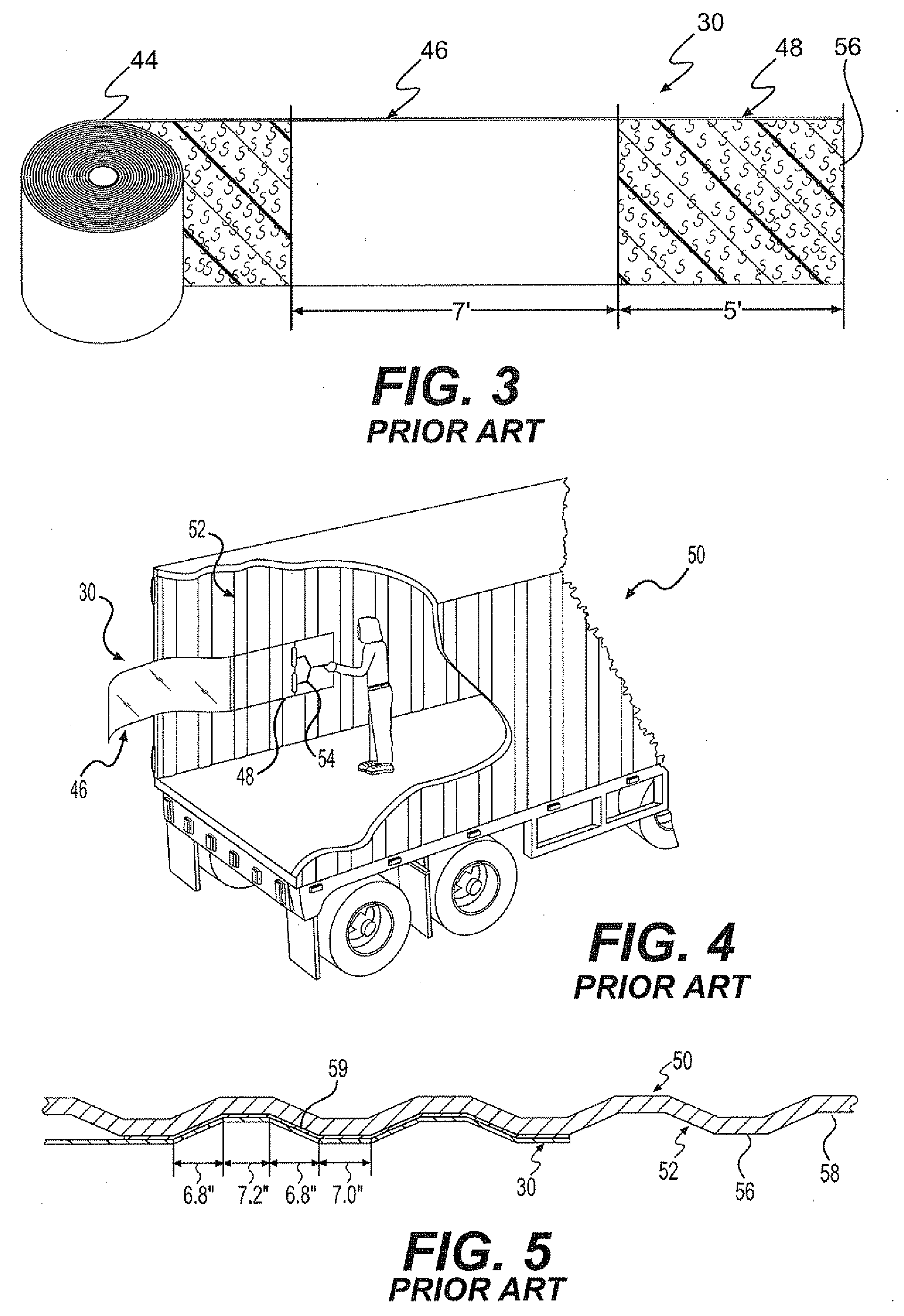

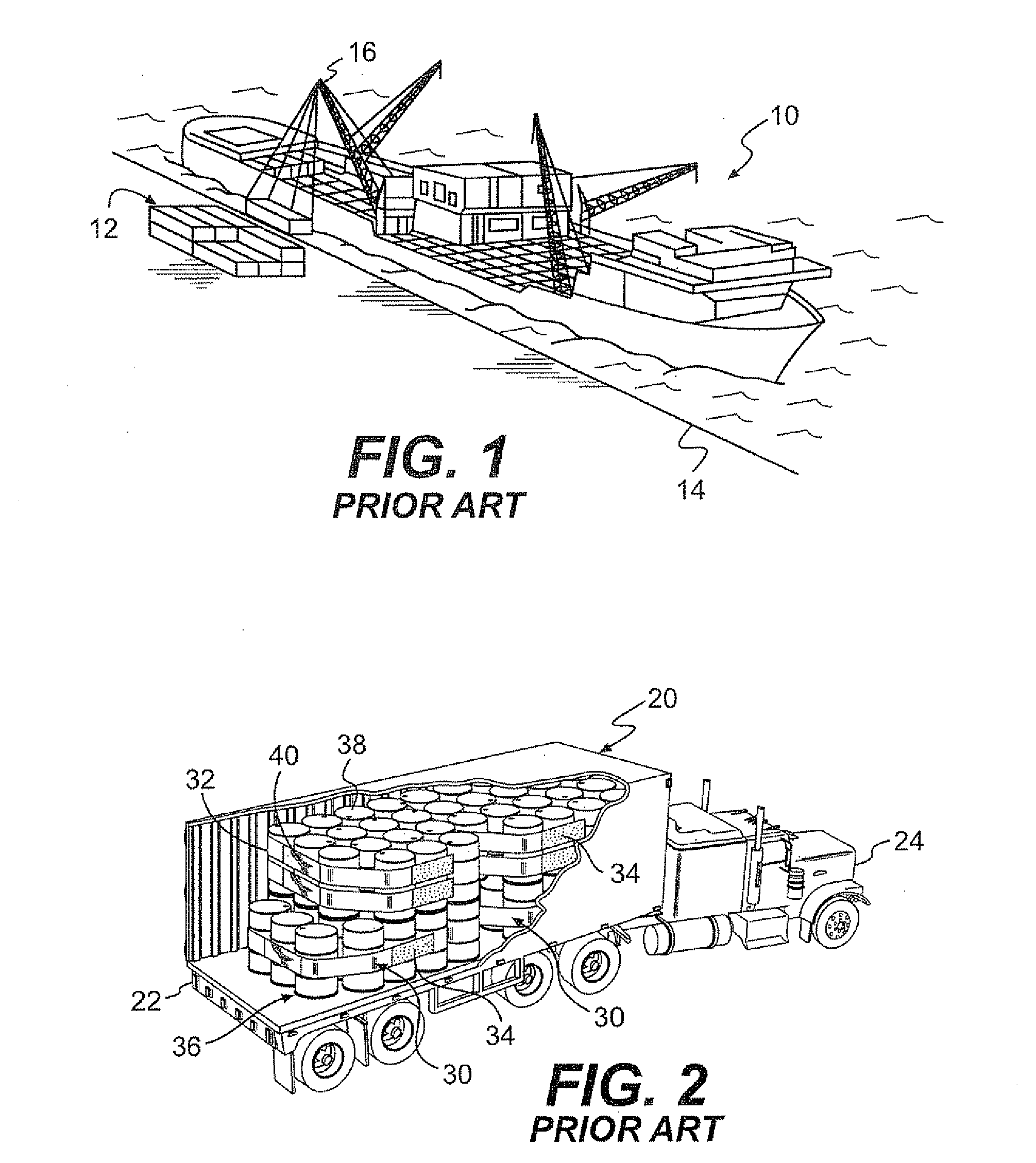

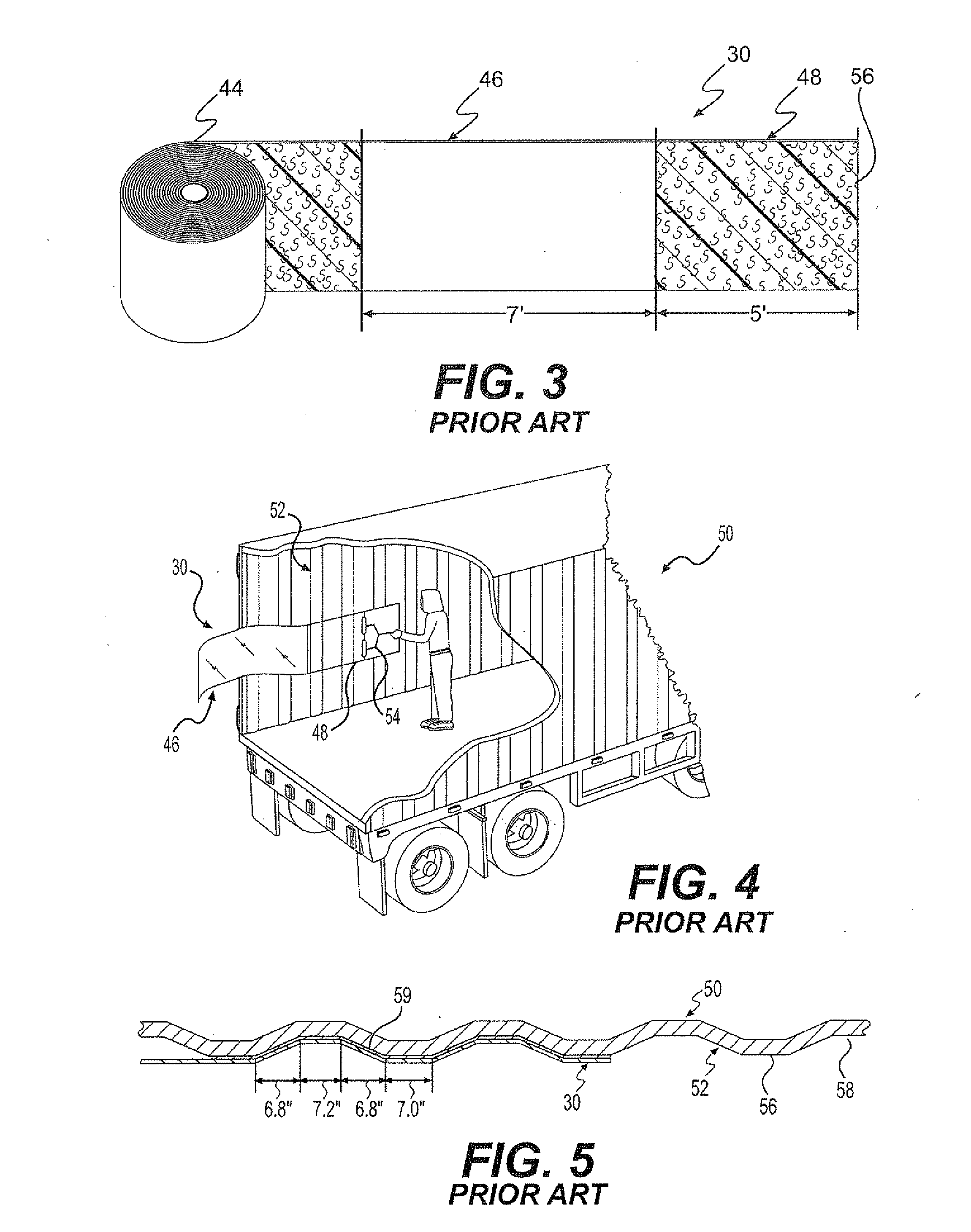

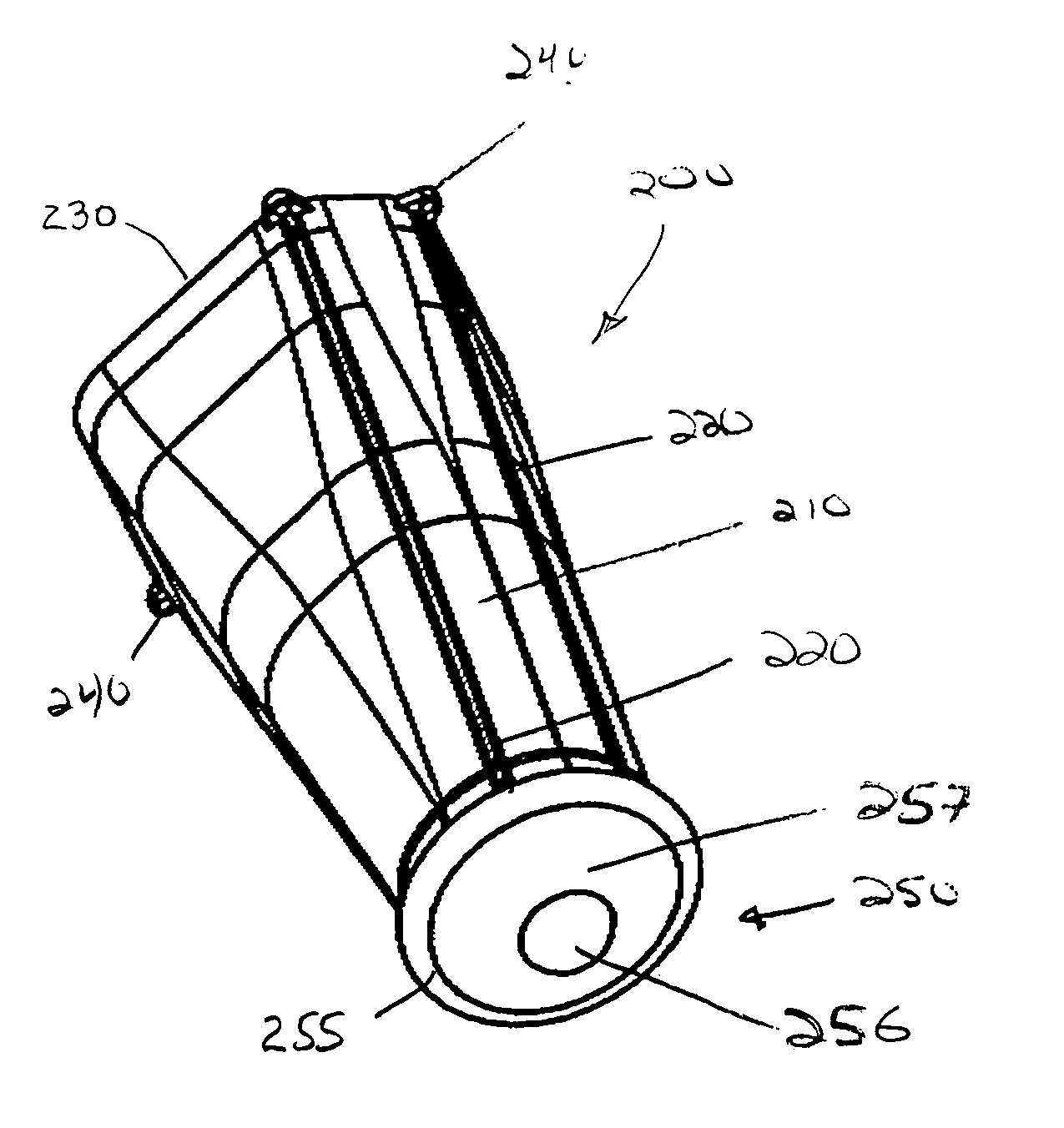

ActiveUS7290969B2Improve securityMinimizes shiftingFlexible elementsLoad securingEngineeringShipping container

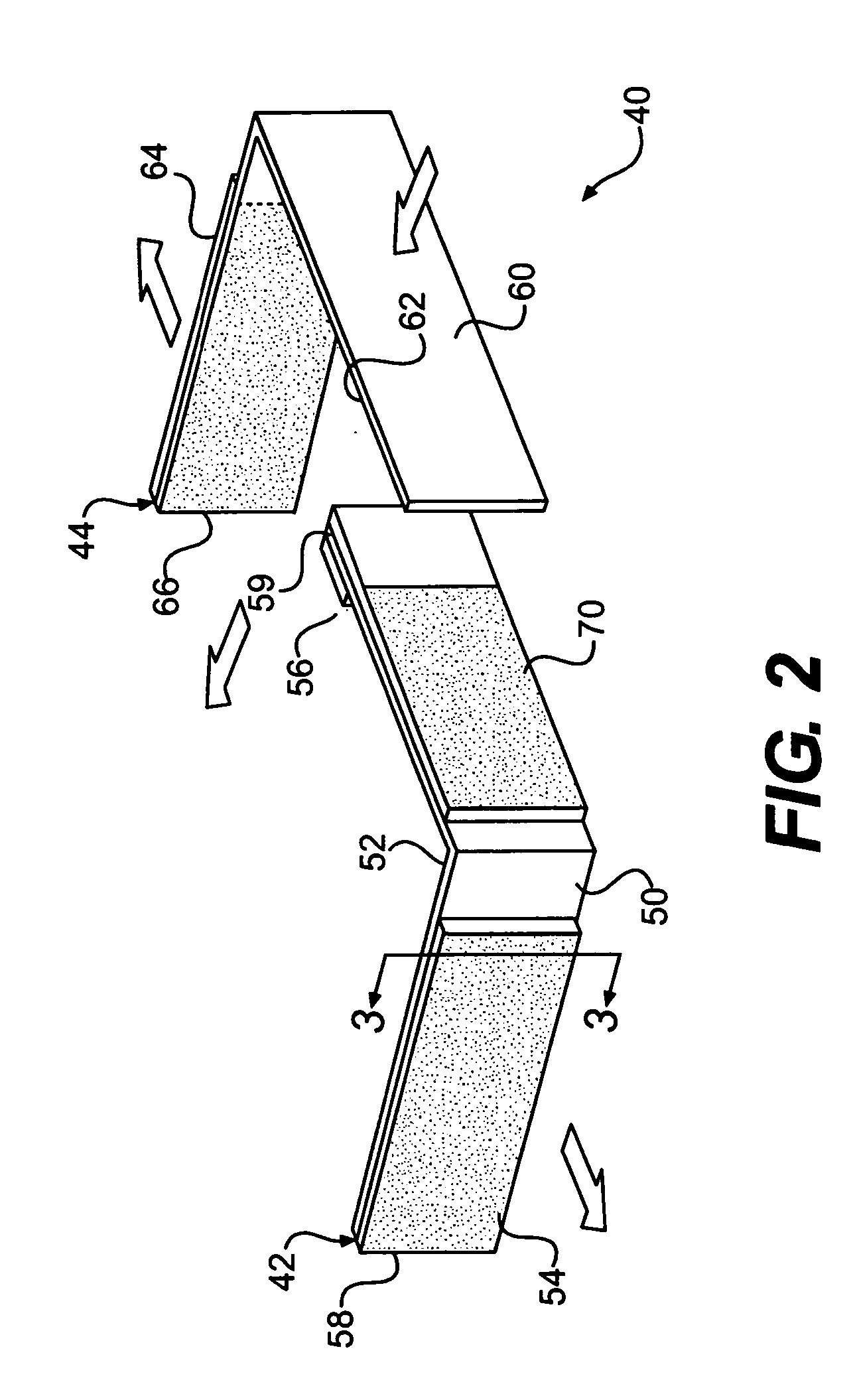

The present invention is directed to a load restraining system and method for securing cargo within a transport container, which is subject to shifting forces. A system includes first and second load restraining strips that cab be self-adhered onto interior wall surfaces of a transport container and extend across cargo within the container. The first load restraining strip has a first adhesive element, which can engage an interior wall surface, and a second adhesive element on a second side, which can engage a surface of cargo to be restrained. A second load restraining strip has a third adhesive element on a first side, which engage an interior wall surface of the container. A fourth adhesive element connected to one of the load restraining strips is operable to secure the two load restraining strips together. A method for securing cargo within a transport container includes providing first and second load restraining strips having adhesive elements, attaching each load restraining strip to internal wall surfaces of a transport container, wrapping the free ends of the load restraining strips around cargo to be restrained, and mutually securing the load restraining strips across cargo.

Owner:MBULL HLDG LLC

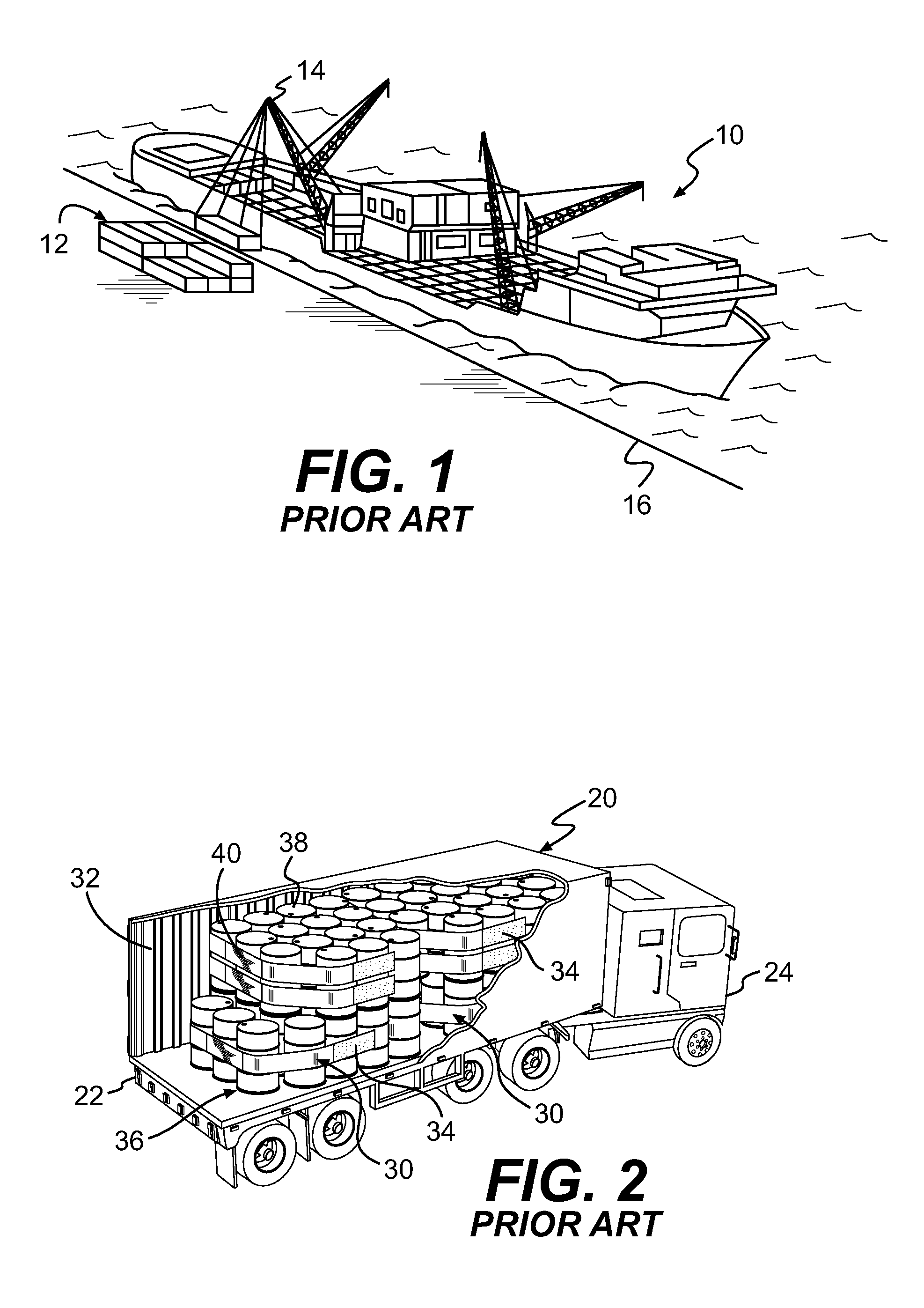

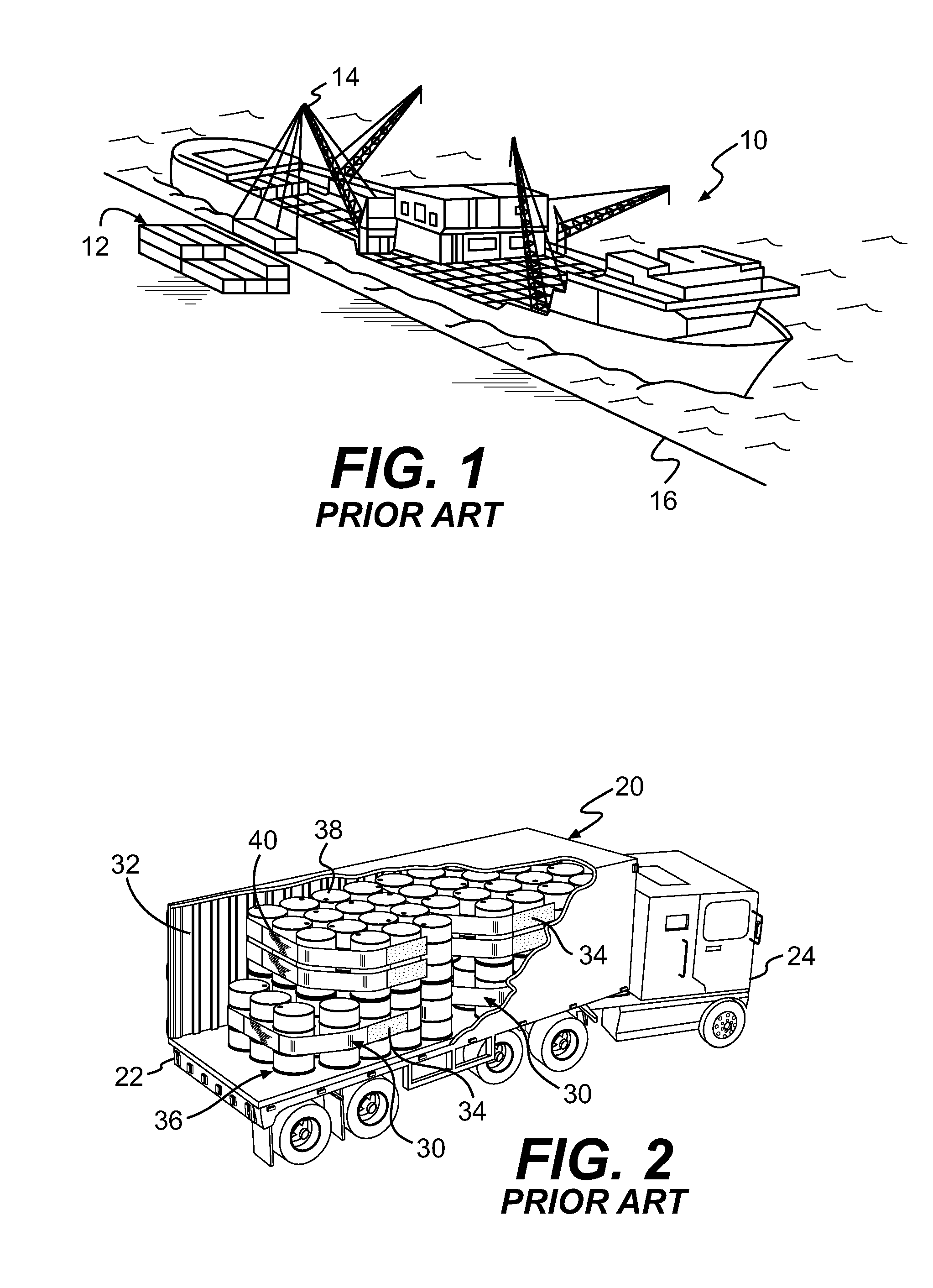

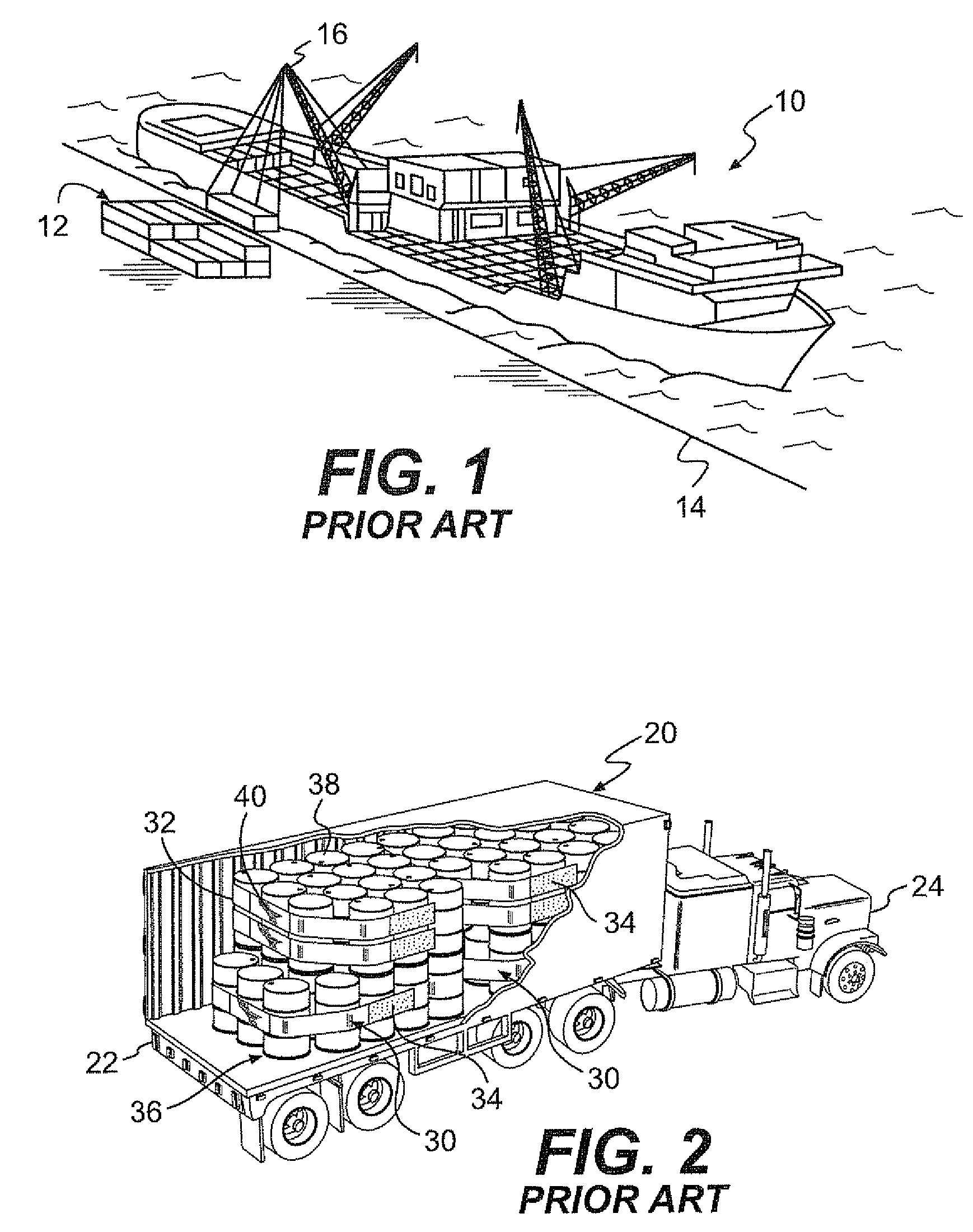

Cargo restraint system and method

InactiveUS7018151B2Improve securityMinimizes shiftingLayered productsFlexible elementsStructural engineeringShipping container

A load restraint system and method for securing cargo within transport containers having corrugated side wall surfaces with lands and alternative valleys said load restraining strips are attached to the side wall surfaces only on the land surfaces of the transport container.

Owner:MBULL HLDG LLC

Mattress cover with fit enhancing composite end panels

ActiveUS20080078029A1Effective gripMinimizes shiftingBlanketBed linenEngineeringMechanical engineering

A fitted mattress cover for enveloping the top, side and end surfaces of a mattress is constructed to accommodate a range of mattress peripheral sizes and thicknesses. The construction utilizes composite end panels which include stretch end panels covering lower partial portions of the mattress end surfaces and which impart recovery forces to effectively grip the mattress and thereby minimize the shifting of the cover relative to the mattress. At the same time, the look and feel of the mattress covering, which may be of importance especially in the case of a fitted sheet, is improved, by virtue of the fact that the side panels can be formed as uninterrupted unitary extensions of the material forming the top side panel, or other material based upon aesthetic considerations, as can upper partial portions (extension end panels) of the composite end panels. In a related aspect, stretchability of the mattress cover skirt may be imparted in a post-manufacture heat treatment finishing step, which may included a laundry wash and dry cycle.

Owner:LOUISVILLE BEDDING CO INC

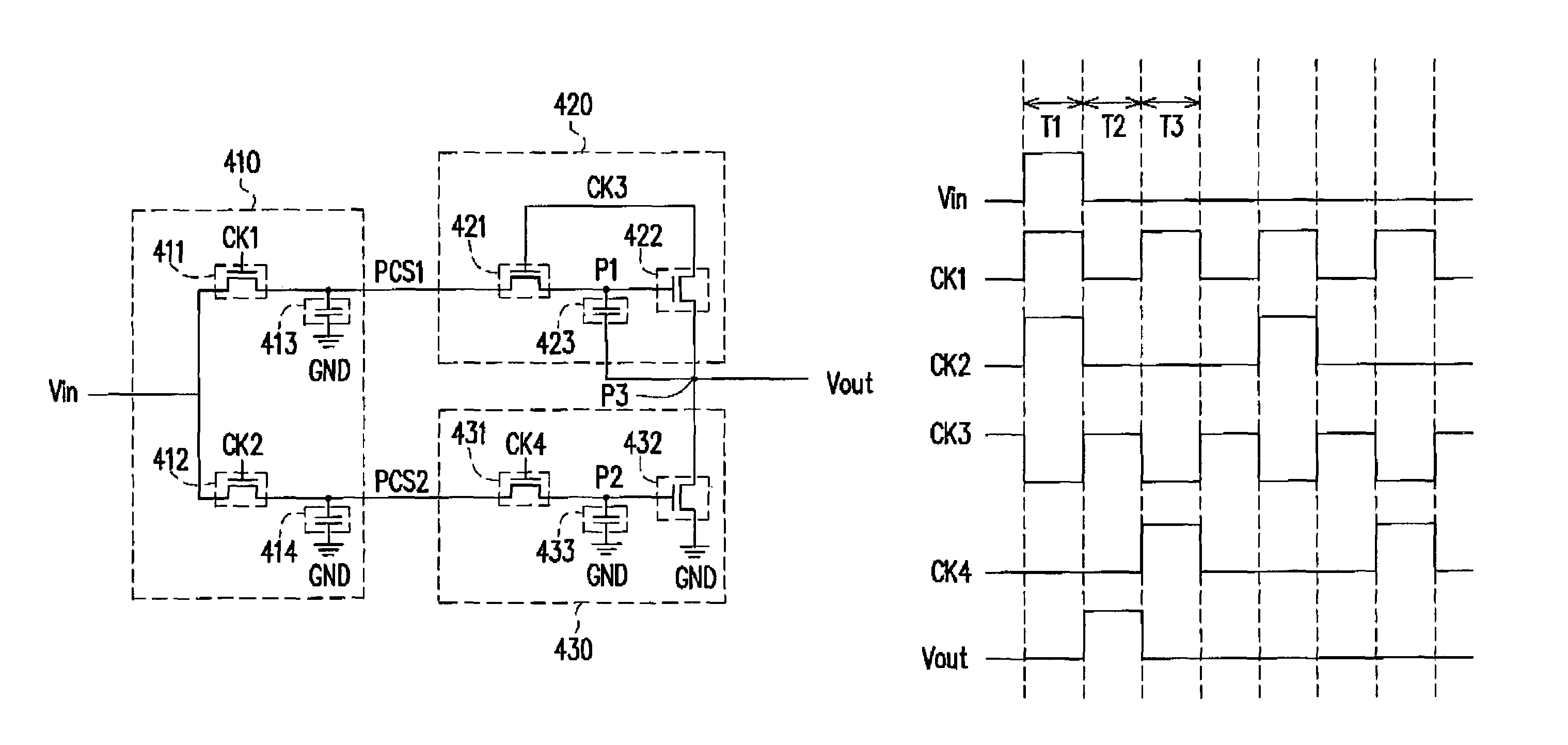

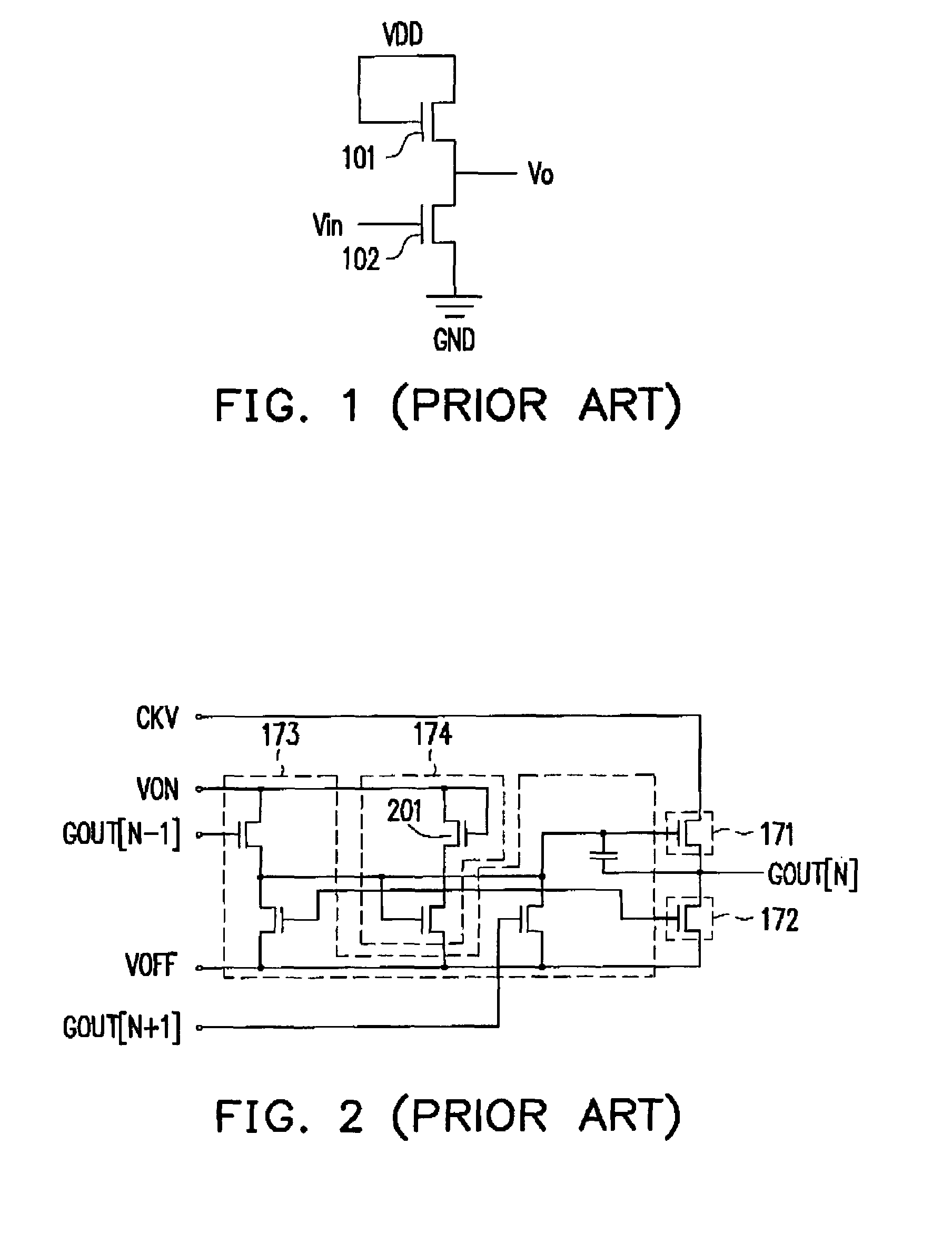

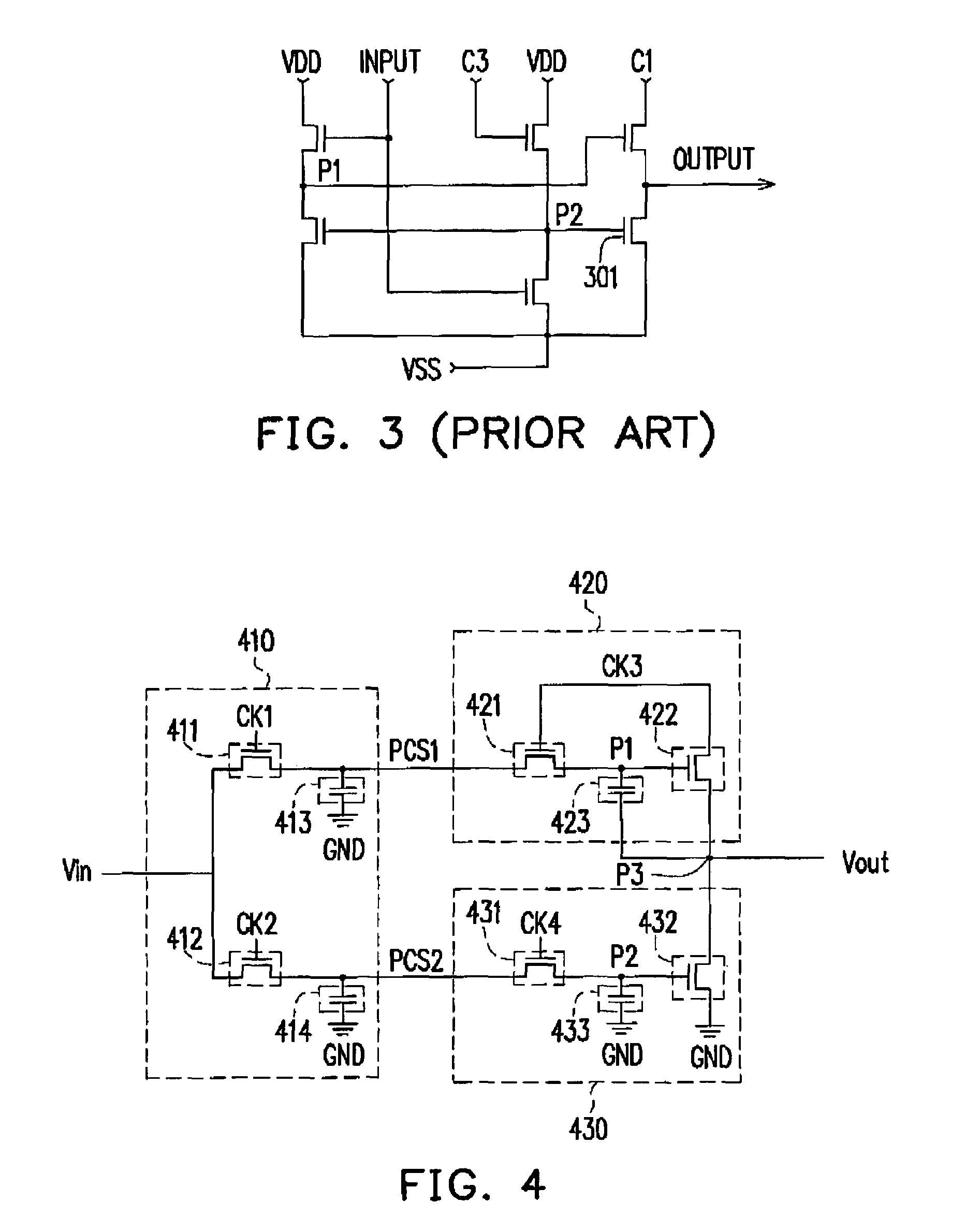

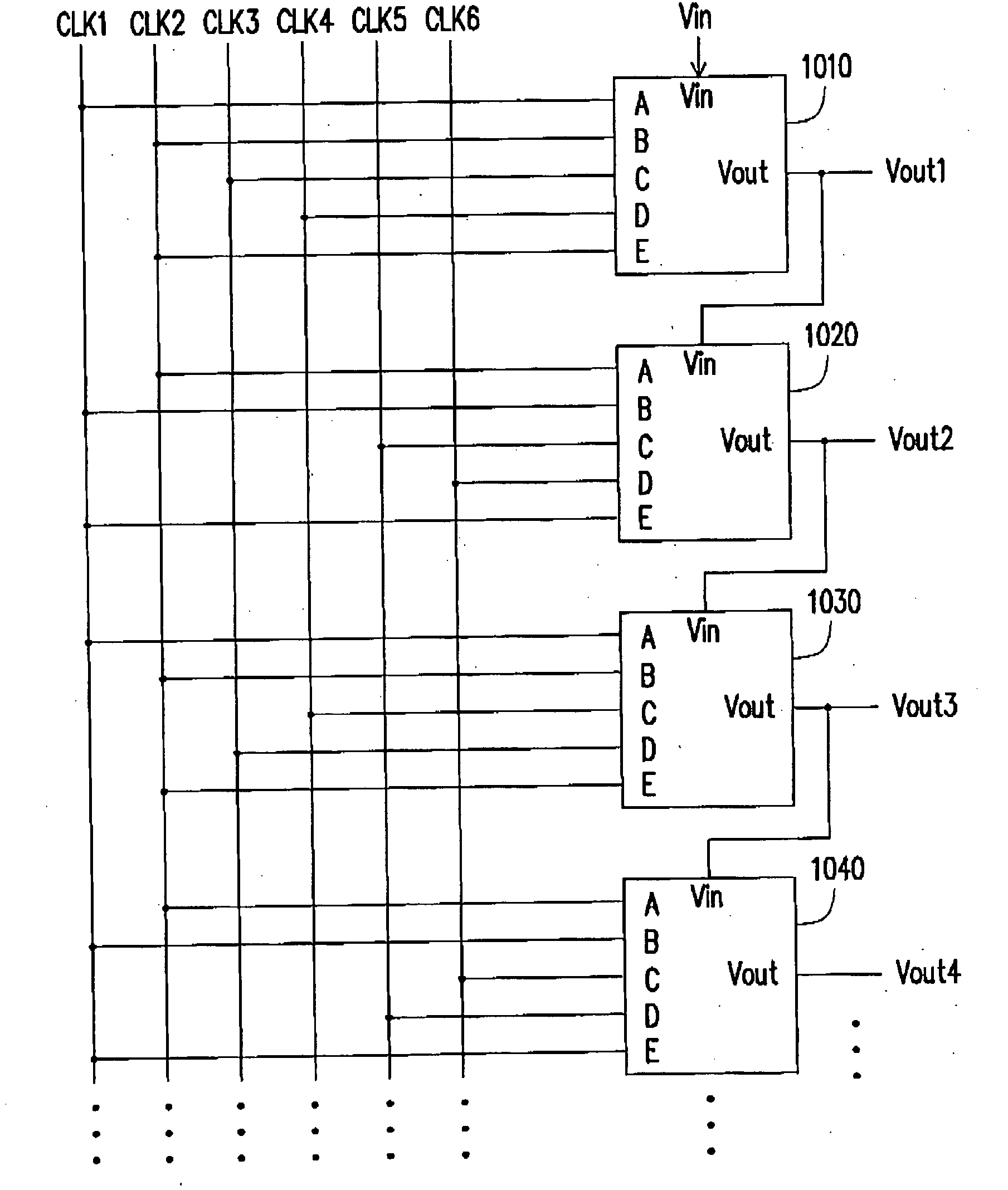

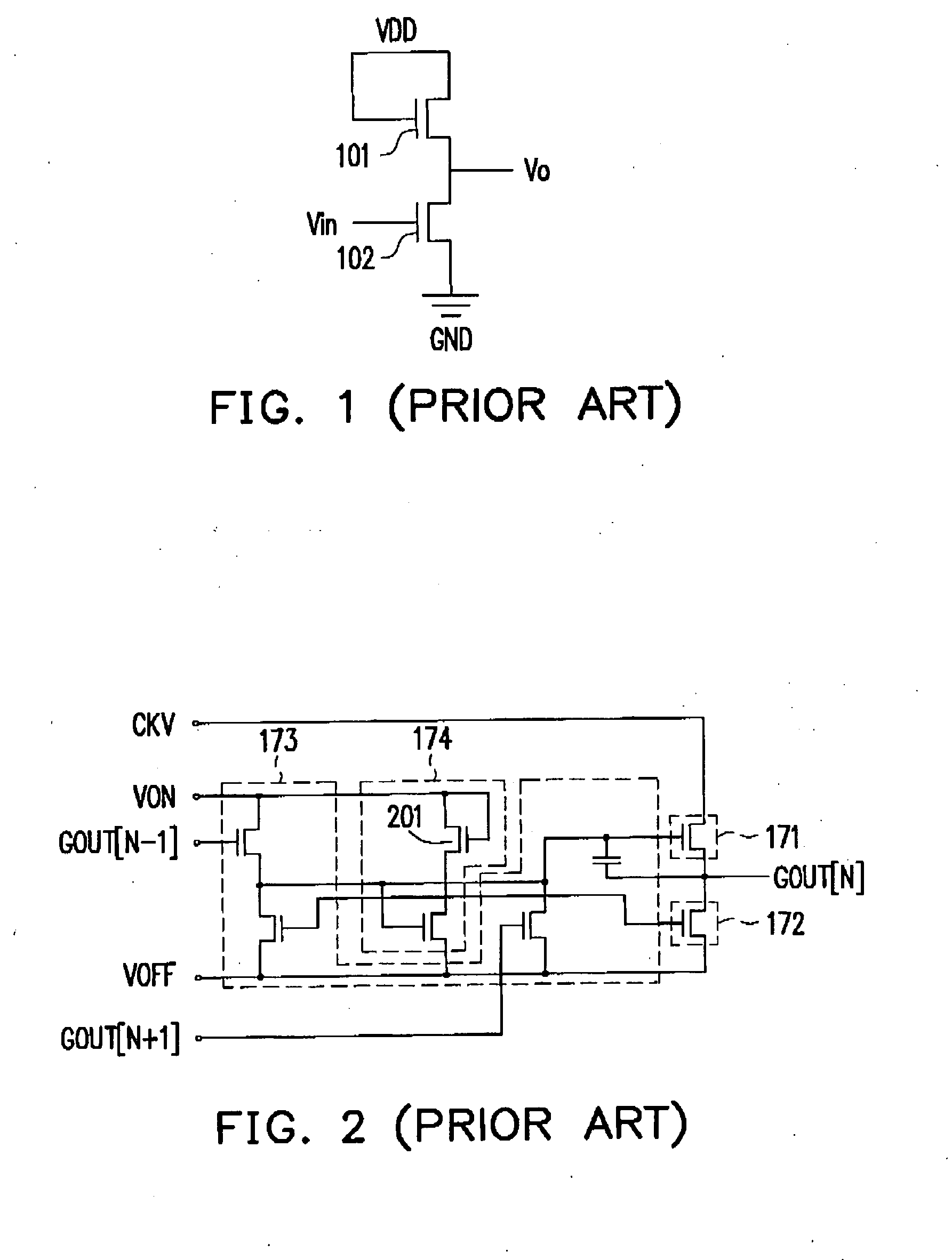

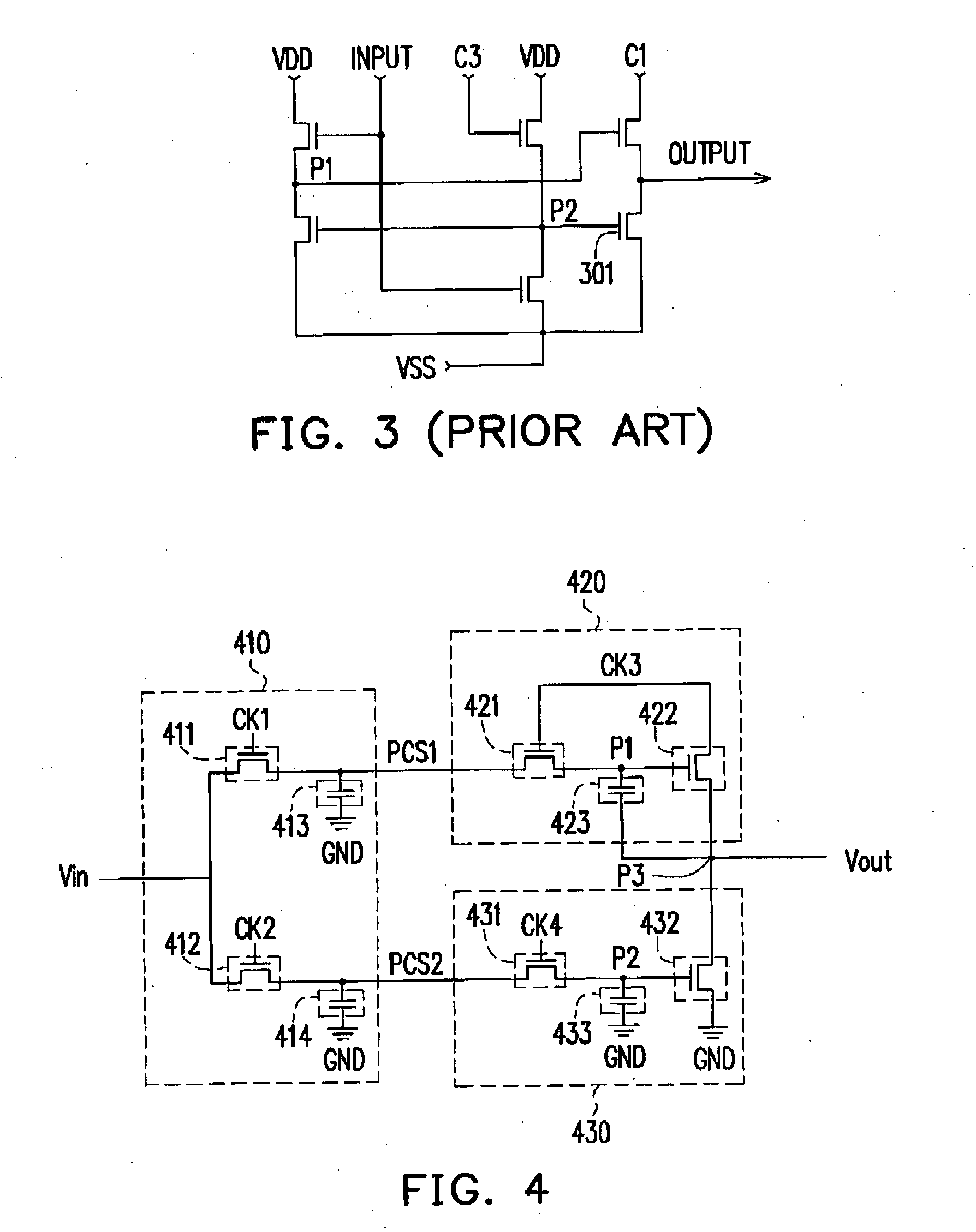

Shift register and shift register apparatus thereof

InactiveUS7590214B2Improve reliabilityImprove stabilityElectric analogue storesDigital storageShift registerPre-charge

A shift register and a shift register apparatus are provided. The shift register includes a plurality of shift register apparatus, and each shift register apparatus comprises a pre-charge circuit, a pull-up circuit and a pull-down circuit. The pre-charge circuit is used for sampling an input signal according to a first clock signal and a second clock signal respectively and generate a first charging signal and a second charging signal respectively. The pull-up circuit is coupled to the pre-charge circuit. The pull-up circuit receives the third clock signal and the first charging signal to output an output signal accordingly. The pull-down circuit is coupled to the pre-charge circuit and the pull-up circuit. The pull-down circuit receives the fourth clock signal and the second charging signal to decide whether to couple the output signal to a common potential.

Owner:CHUNGHWA PICTURE TUBES LTD

Shift register and shift register apparatus thereof

InactiveUS20080279327A1Improve reliabilityImprove stabilityElectric analogue storesDigital storageShift registerPre-charge

A shift register and a shift register apparatus are provided. The shift register includes a plurality of shift register apparatus, and each shift register apparatus comprises a pre-charge circuit, a pull-up circuit and a pull-down circuit. The pre-charge circuit is used for sampling an input signal according to a first clock signal and a second clock signal respectively and generate a first charging signal and a second charging signal respectively. The pull-up circuit is coupled to the pre-charge circuit. The pull-up circuit receives the third clock signal and the first charging signal to output an output signal accordingly. The pull-down circuit is coupled to the pre-charge circuit and the pull-up circuit. The pull-down circuit receives the fourth clock signal and the second charging signal to decide whether to couple the output signal to a common potential.

Owner:CHUNGHWA PICTURE TUBES LTD

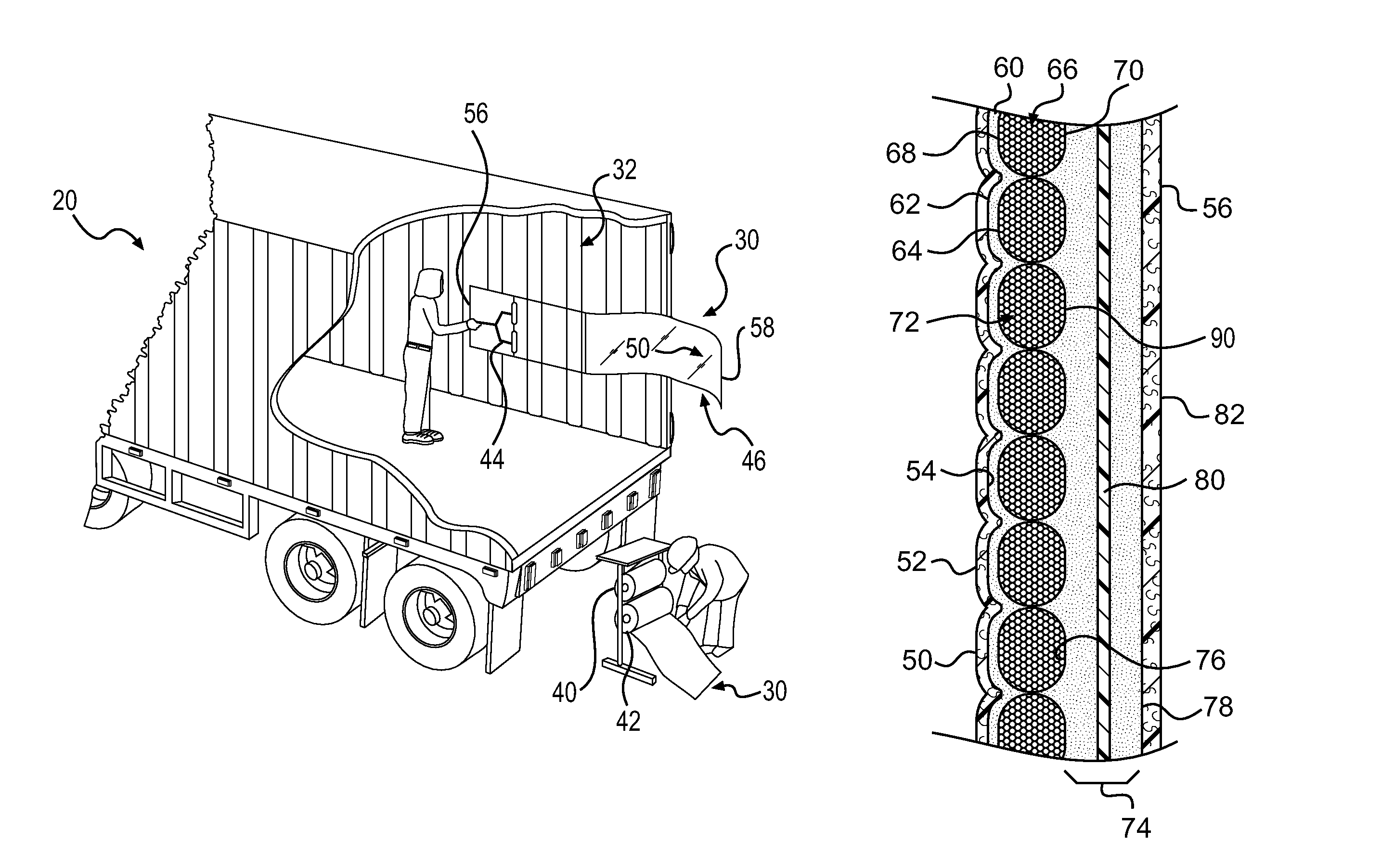

Cargo restraint system with enhanced polyester reinforcement filament strand denier content

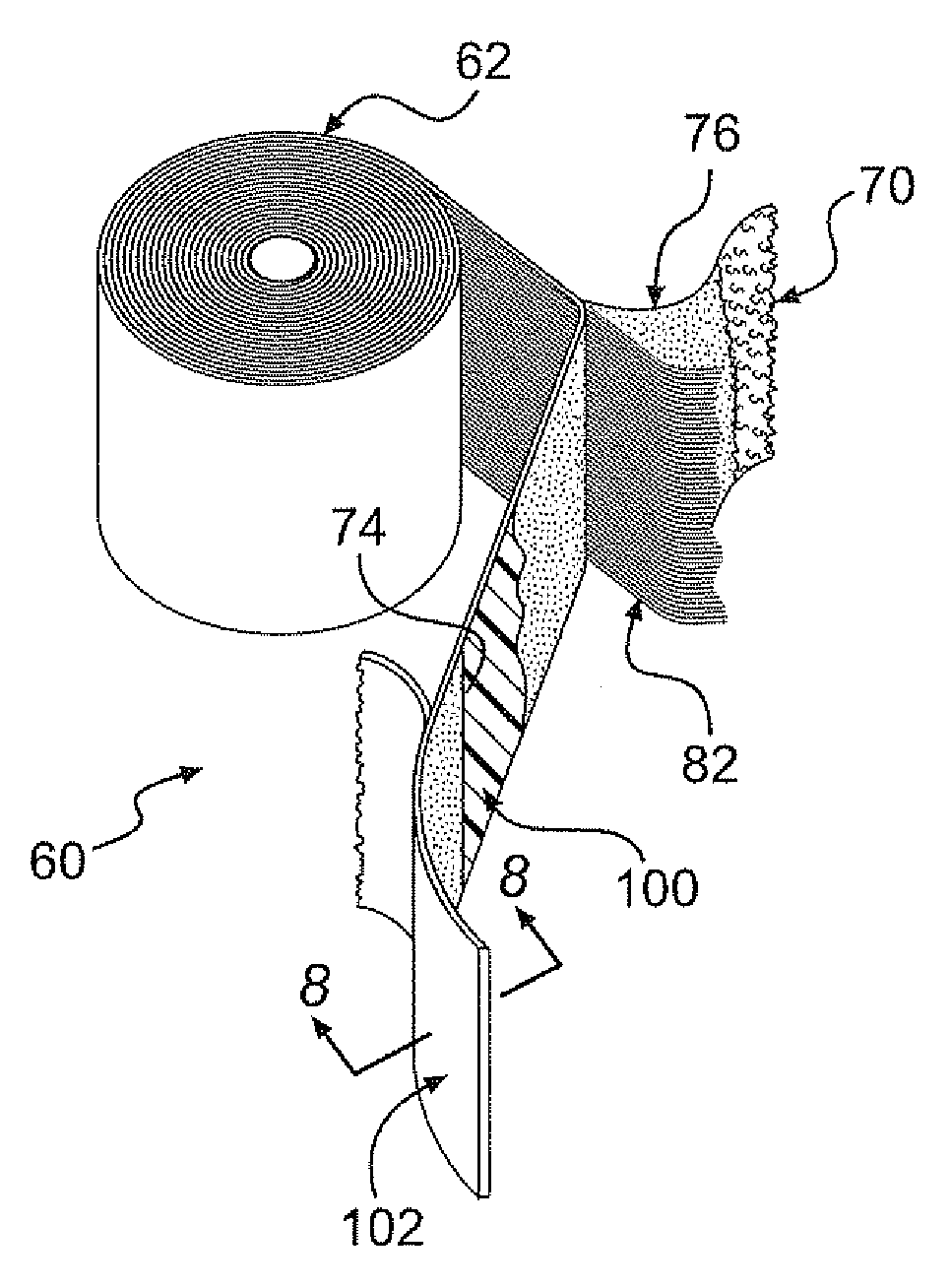

A cargo restraint system with enhanced filament characteristics wherein the restraint system includes laminated load restraining strips with a layer of reinforcement material comprising a plurality of substantially parallel bundles of filaments and wherein the layer of reinforcement contains approximately three hundred and twenty four ends an approximately four hundred and eighty four filaments and each filament comprises one or more polyester monofilament strands having a total break strength of approximately between fifteen point nine and twenty point seven grams.

Owner:MBULL HLDG LLC

Cargo restraint system with enhanced reinforcement content

ActiveUS8408852B1Improve efficiencyMinimizes shiftingFlexible elementsLoad securingBreaking strengthGram

A cargo restraint system with enhanced filament characteristics wherein the restraint system includes load restraining strips with a layer of reinforcement material comprising a plurality of substantially parallel bundles of ends of filaments each filament comprises a plurality of one or more monofilament strands wherein the layer of reinforcement material has a break strength of between approximately three million two hundred forty three thousand one hundred and sixty nine grams and two million four hundred ninety four thousand seven hundred forty five grams.

Owner:MBULL HLDG LLC

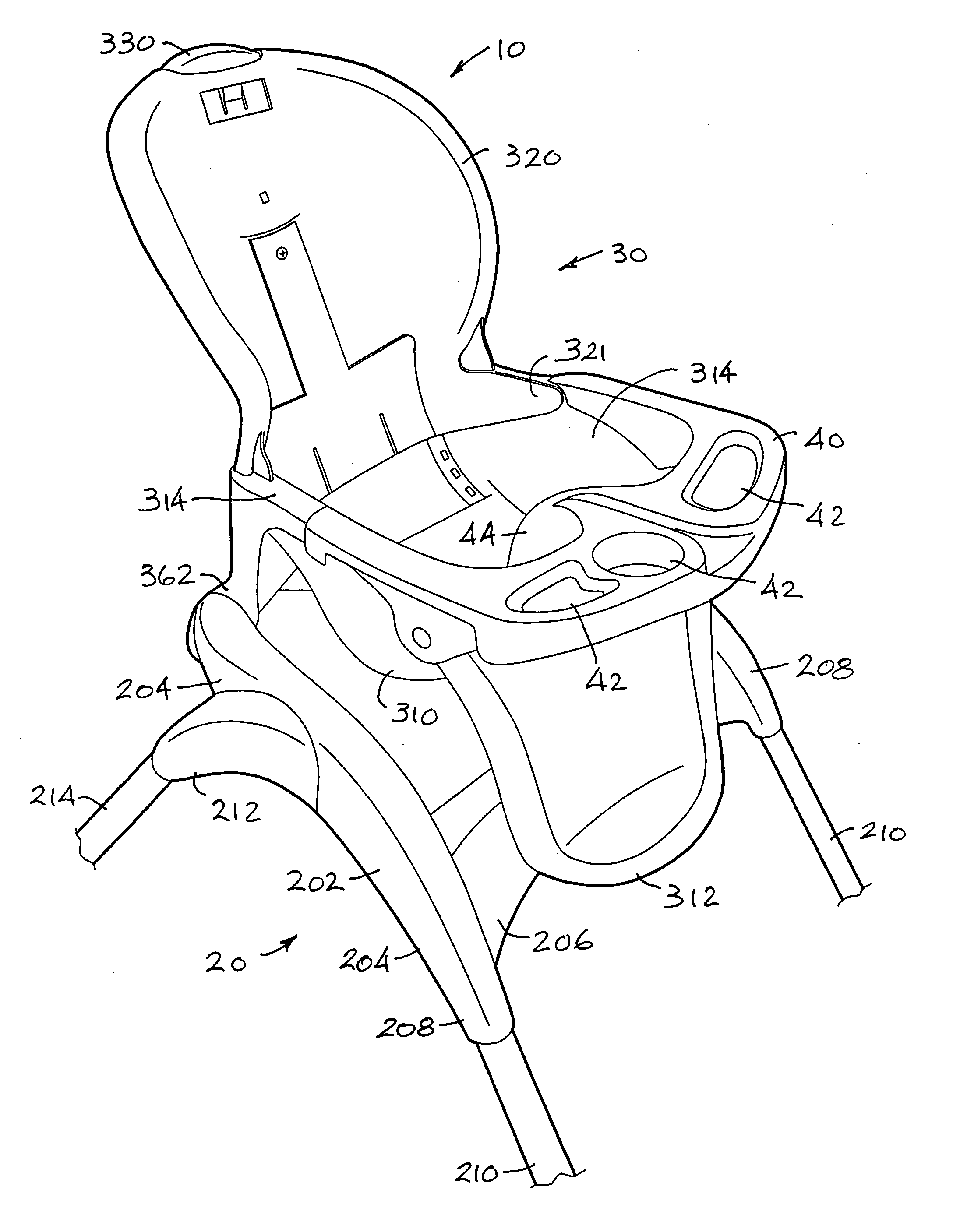

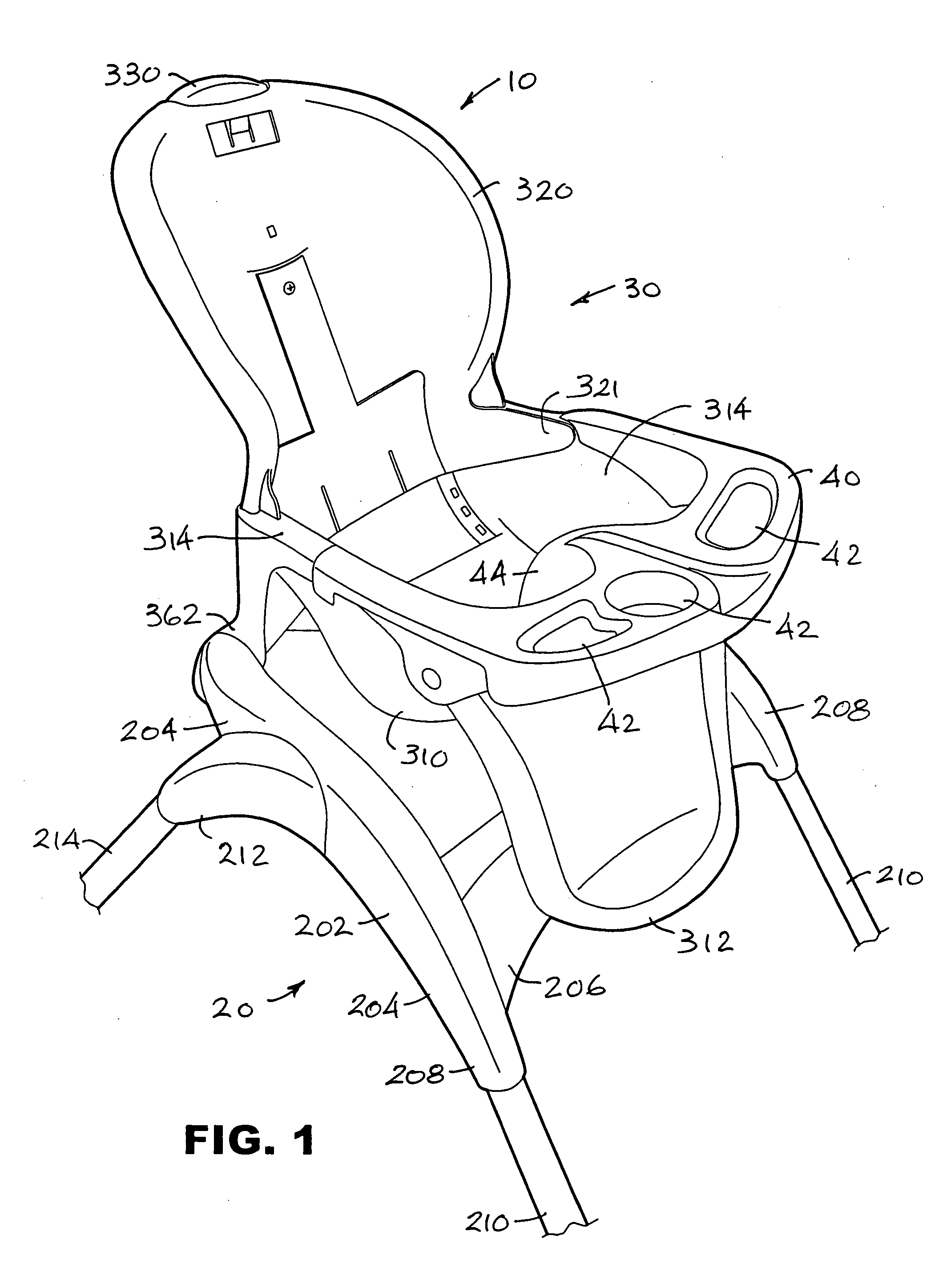

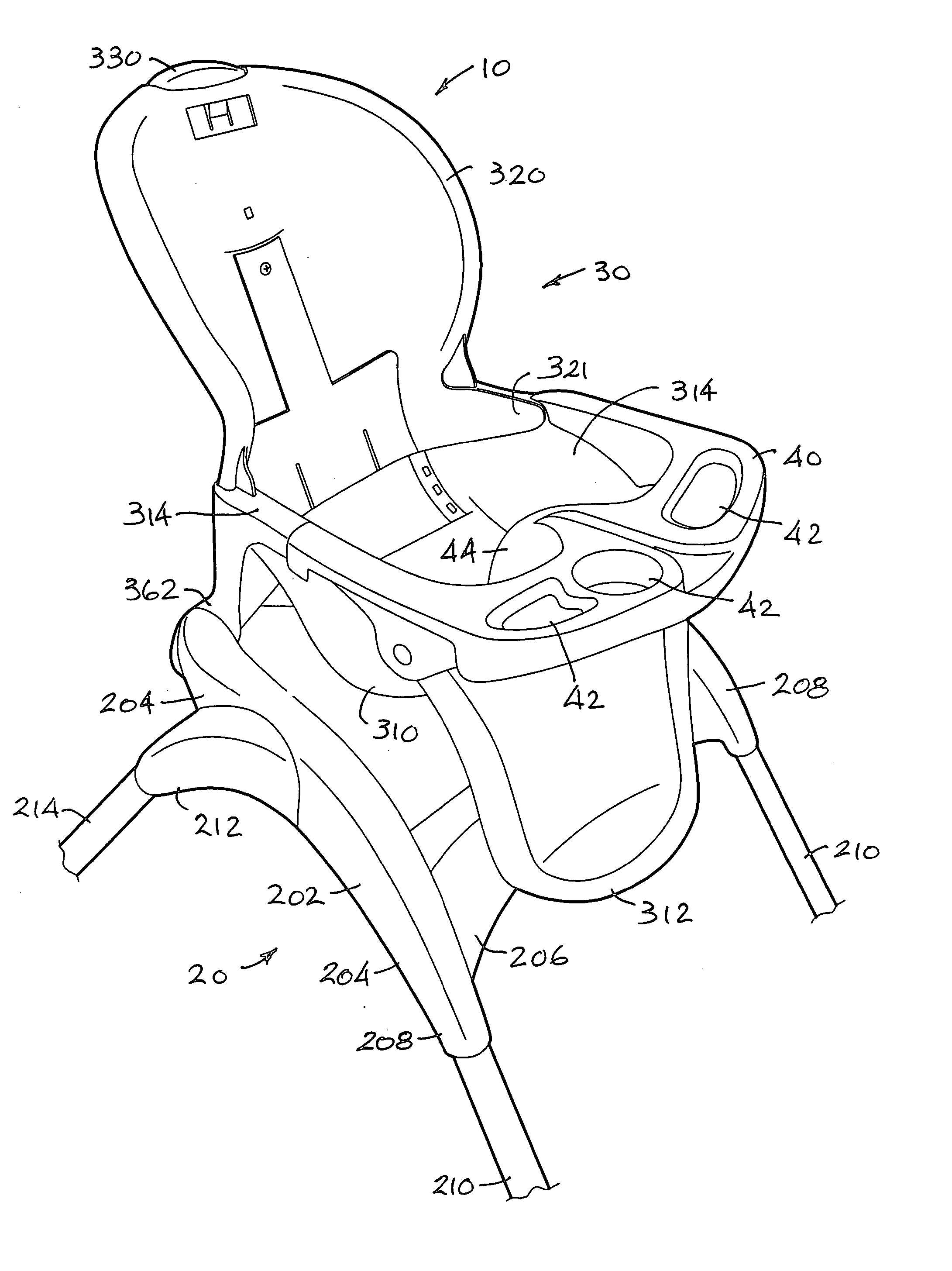

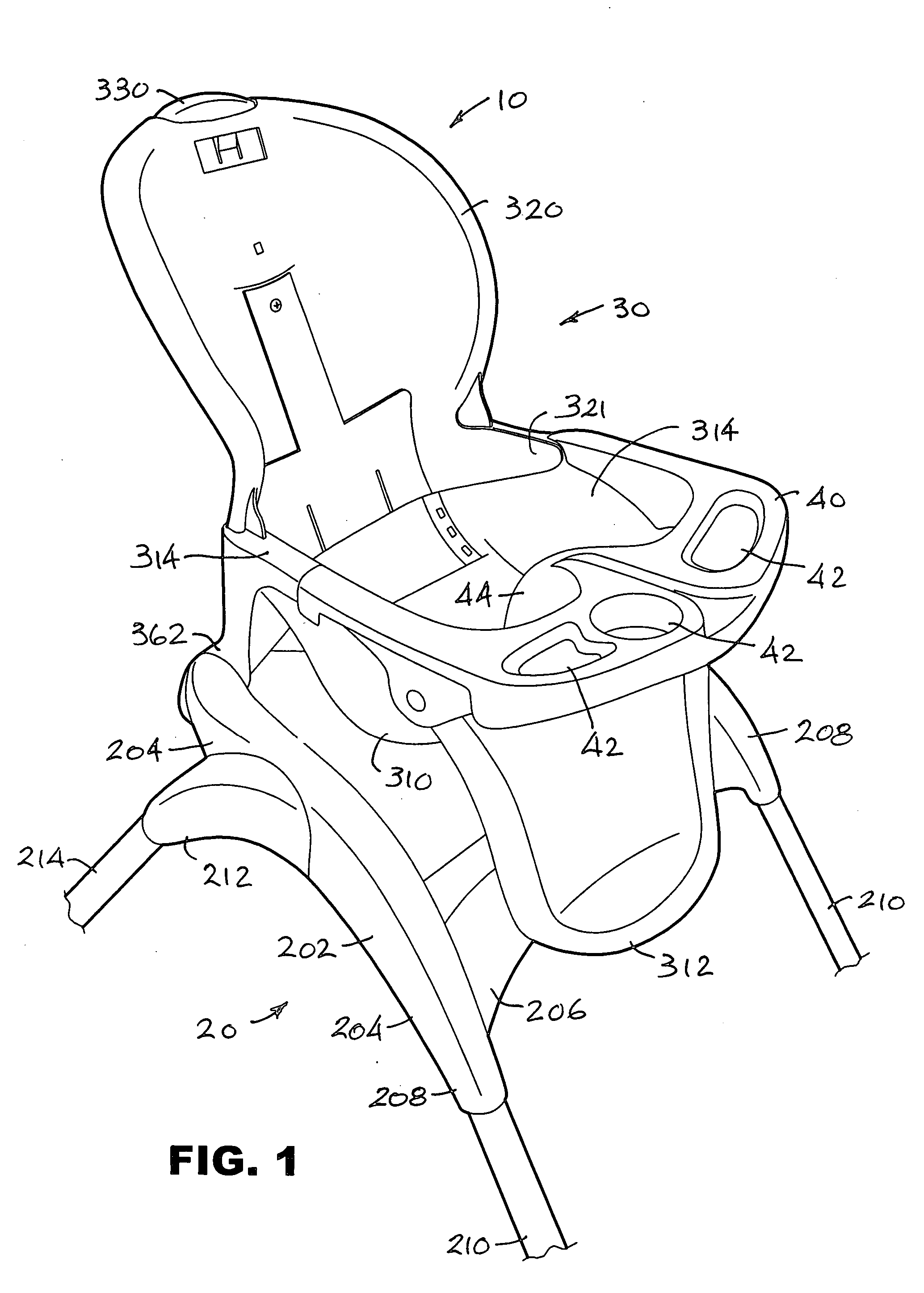

High chair

InactiveUS20050127722A1Easy to cleanFirm supportSchool benchesKids chairsCaregiver personEngineering

A high chair features various modes of adjustability and enhanced utility. The height of the chair can be adjusted using a single hand that engages a rear handle. The height of a seat platform of the chair can be adjusted separately relative to the tray. The tray itself is ergonomically designed for the benefit of the caregiver. A removable tray liner facilitates after-meal clean-up. Wheels on the underside of the tray ease fore / aft adjustment. A pivoting back rest of the chair minimizes rearward shift of the center of gravity of the occupied chair, thus requiring a smaller chair footprint. Further, an accessory bar pivoted to a seat back portion of the chair provides readily accessible entertainment.

Owner:GRACO CHILDRENS PROD INC

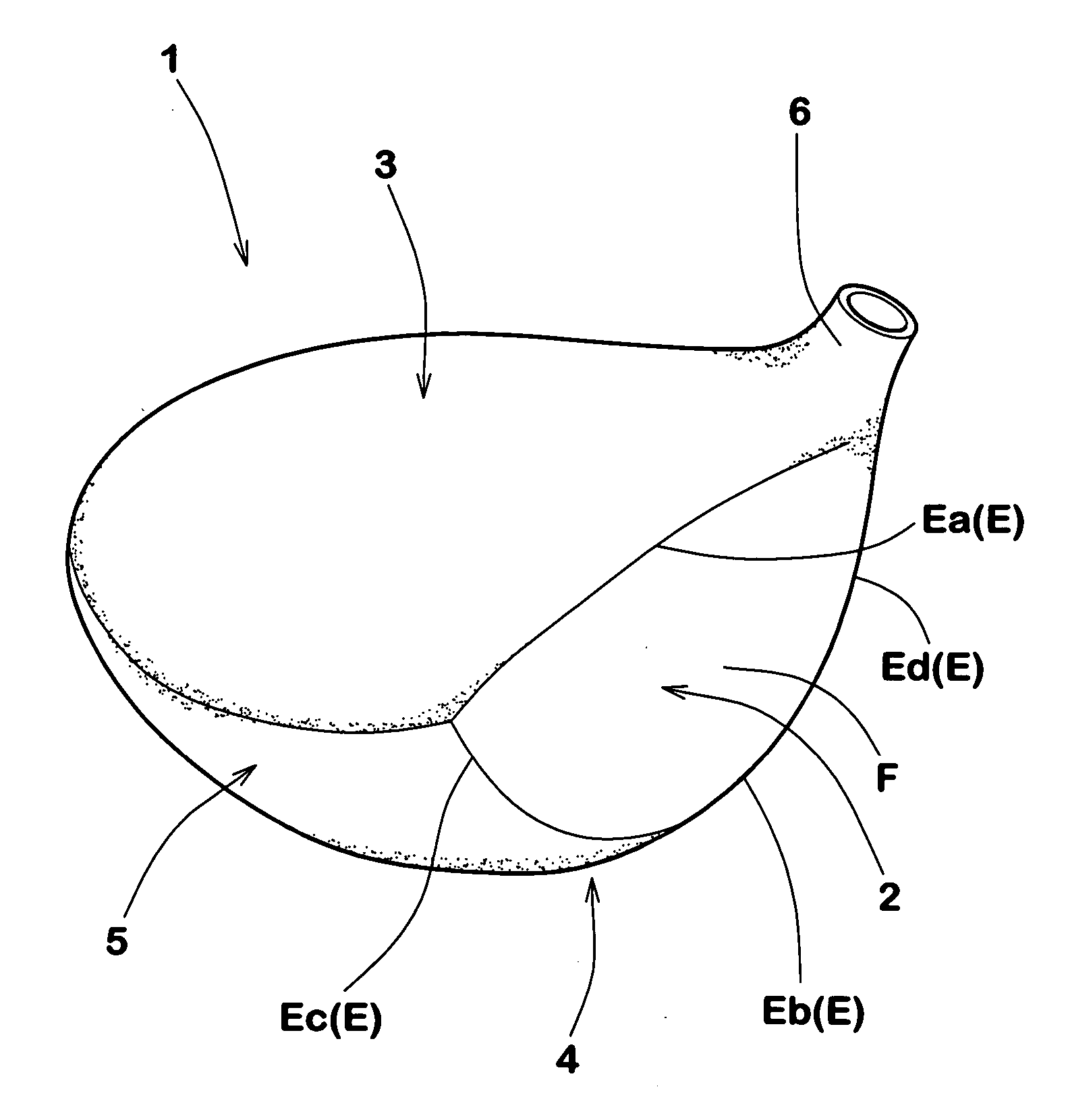

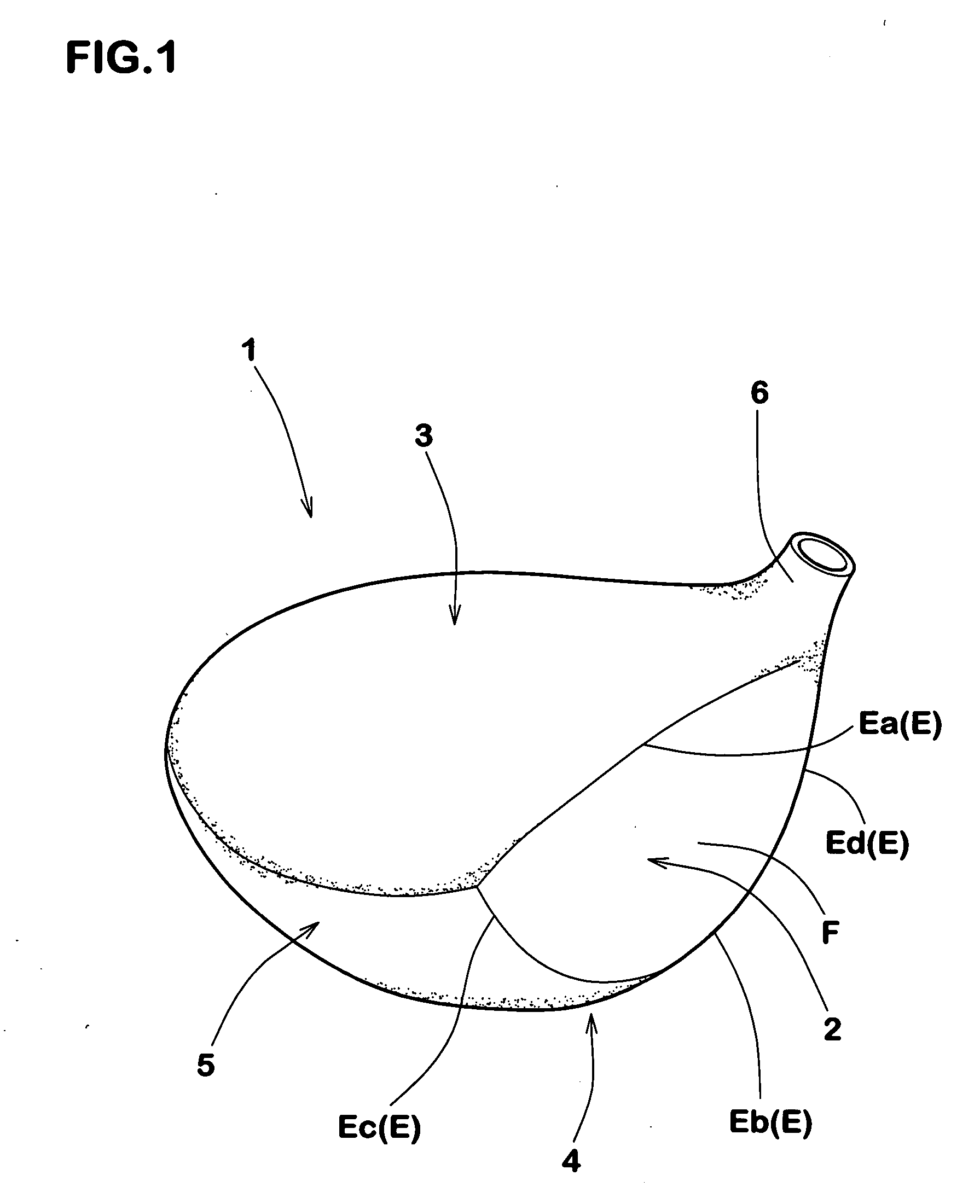

Golf club head and method for manufacturing the same

InactiveUS20060287131A1Easy to adjustPrevent movementGolf clubsRacket sportsCoefficient of restitutionEngineering

Owner:DUNLOP SPORTS CO LTD

Cargo restraint system with enhanced reinforcement end filament content

ActiveUS8403607B1Improve efficiencyMinimizes shiftingFlexible elementsLoad securingBreaking strengthGram

A cargo restraint system with enhanced filament characteristics wherein the restraint system includes laminated load restraining strips with a layer of reinforcement material comprising a plurality of substantially parallel bundles of filaments and wherein the layer of reinforcement contains approximately two hundred and fifteen to two hundred and seventy nine ends of reinforcing material and each end of reinforcement material comprises approximately four hundred and eighty four filaments of reinforcement material and each filament comprises one or more monofilament strands having a total break strength of approximately twenty four grams.

Owner:MBULL HLDG LLC

Cargo restraint system with enhanced reinforcement filament break strength content

ActiveUS8403609B1Improve efficiencyMinimizes shiftingFlexible elementsLoad securingBreaking strengthGram

A cargo restraint system with enhanced filament characteristics wherein the restraint system includes laminated load restraining strips with a layer of reinforcement material comprising a plurality of substantially parallel bundles of filaments and wherein the layer of reinforcement filaments each have a break strength of approximately fifteen point nine (15.9 grams to approximately twenty point seven (20.7) grams.

Owner:MBULL HLDG LLC

Cargo restraint system with enhanced reinforcement filament content

ActiveUS8403608B1Improve efficiencyMinimizes shiftingFlexible elementsLoad securingBreaking strengthGram

A cargo restraint system with enhanced filament characteristics wherein the restraint system includes laminated load restraining strips with a layer of reinforcement material comprising a plurality of substantially parallel bundles of filaments and wherein the layer of reinforcement contains approximately three hundred twenty four ends of reinforcing material and each end of reinforcement material comprises approximately three hundred and twenty one to four hundred and seventeen filaments of reinforcement material and each filament comprises one or more monofilament strands having a total break strength of approximately twenty four grams.

Owner:MBULL HLDG LLC

Overland cargo restraint system and method

ActiveUS20060257224A1Improve efficiencyImprove securityFlexible elementsLoad securingEngineeringMechanical engineering

The present invention is directed to a load restraining system and method for securing cargo within a transport container, which is subject to shifting forces. A system includes first and second load restraining strips that cab be self-adhered onto interior wall surfaces of a transport container and extend across cargo within the container. The first load restraining strip has a first adhesive element, which can engage an interior wall surface, and a second adhesive element on a second side, which can engage a surface of cargo to be restrained. A second load restraining strip has a third adhesive element on a first side, which engage an interior wall surface of the container. A fourth adhesive element connected to one of the load restraining strips is operable to secure the two load restraining strips together. A method for securing cargo within a transport container includes providing first and second load restraining strips having adhesive elements, attaching each load restraining strip to internal wall surfaces of a transport container, wrapping the free ends of the load restraining strips around cargo to be restrained, and mutually securing the load restraining strips across cargo.

Owner:MBULL HLDG LLC

Cargo restraint system with enhanced peel strength

ActiveUS8113752B2Improve securityMinimizes shiftingFilm/foil adhesivesSynthetic resin layered productsAdhesiveFront edge

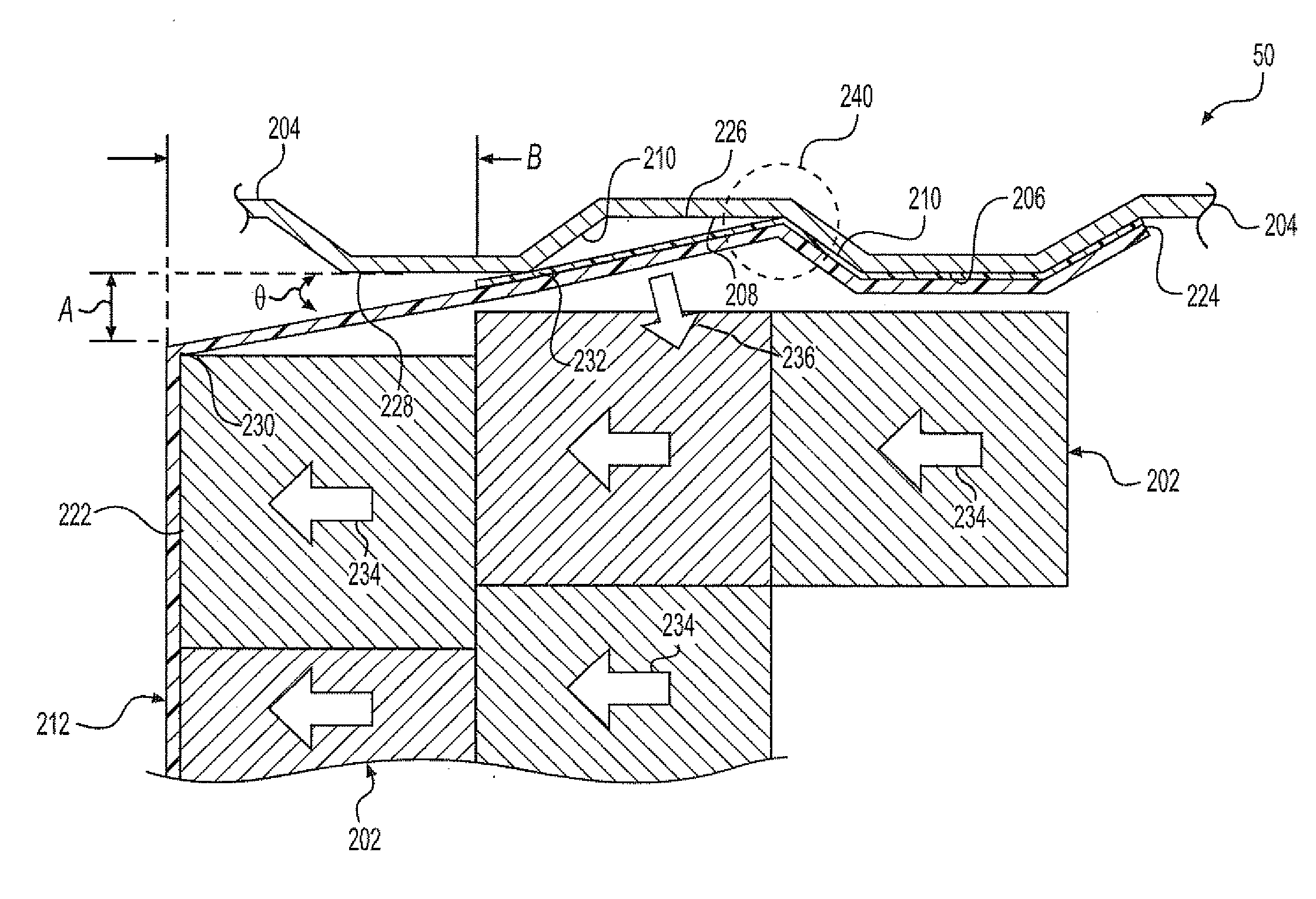

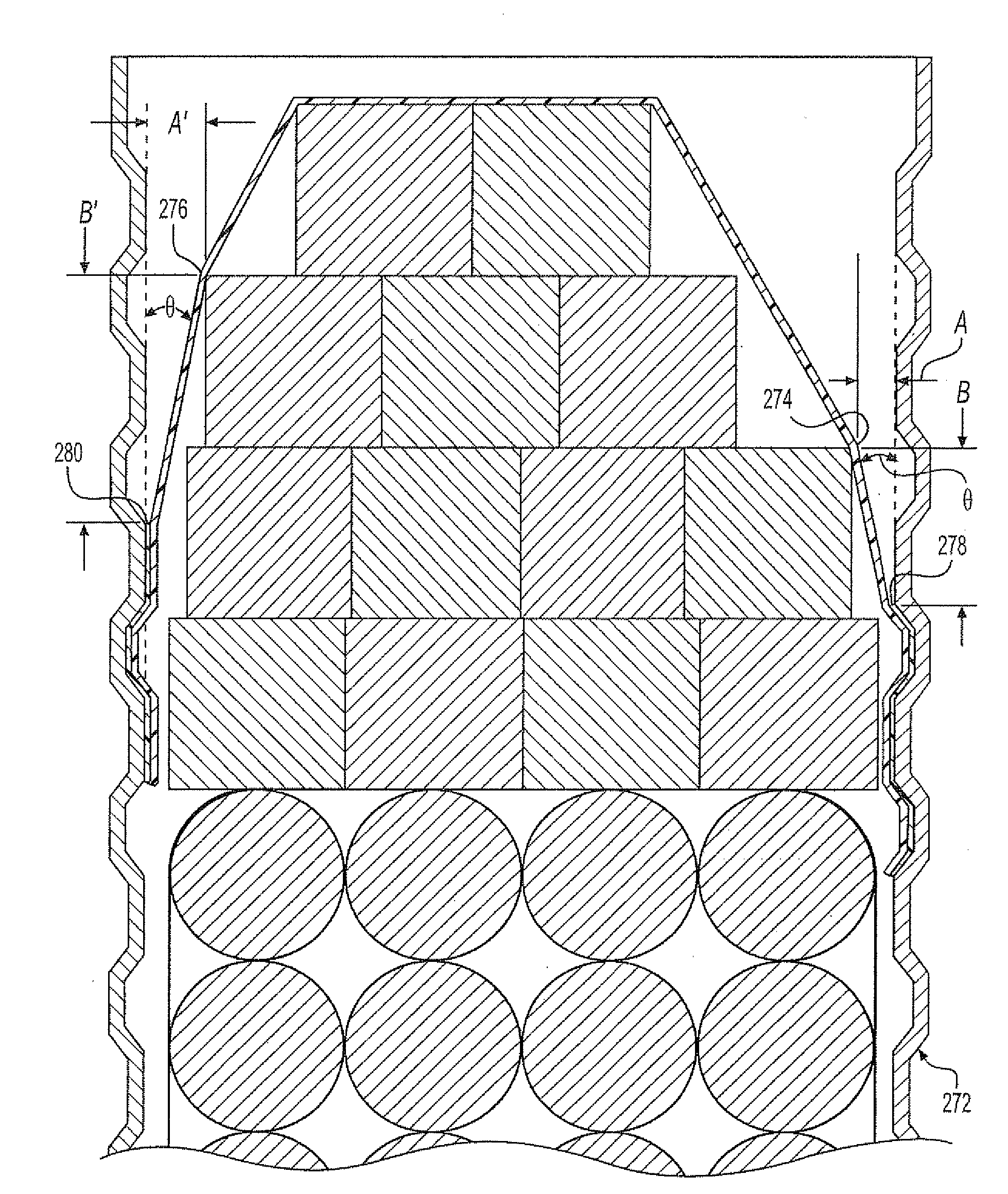

A cargo restraint system and method with enhanced peel strength characteristics the restraint system including laminated load restraining strips with a layer of adhesive to adhere the restraining strip to a container wall surface having a thickness of approximately greater than 1.6 and less than 3.0 millimeters. The load restraint method for securing cargo within transport containers wherein an angle θ of attachment between a side wall of a container and a reinforcing strip of material attached to the side wall is maintained at approximately 15 degrees or less in accordance with the formula B≦cot θ•A, where θ is the angle formed between an exterior surface of said load restraining strip and an interior plane of the lateral wall surface of the transport container “A” is the distance from a front edge of a load to an adjacent side wall and “B” is the distance along the wall of the container behind the point of contact of the restraining strip with an edge of the load to be restrained.

Owner:MBULL HLDG LLC

High chair

InactiveUS20050006930A1Easy to cleanFirm supportSchool benchesKids chairsCaregiver personEngineering

A high chair features various modes of adjustability and enhanced utility. The height of the chair can be adjusted using a single hand that engages a rear handle. The height of a seat platform of the chair can be adjusted separately relative to the tray. The tray itself is ergonomically designed for the benefit of the caregiver. A removable tray liner facilitates after-meal clean-up. Wheels on the underside of the tray ease fore / aft adjustment. A pivoting back rest of the chair minimizes rearward shift of the center of gravity of the occupied chair, thus requiring a smaller chair footprint. Further, an accessory bar pivoted to a seat back portion of the chair provides readily accessible entertainment.

Owner:GRACO CHILDRENS PROD INC

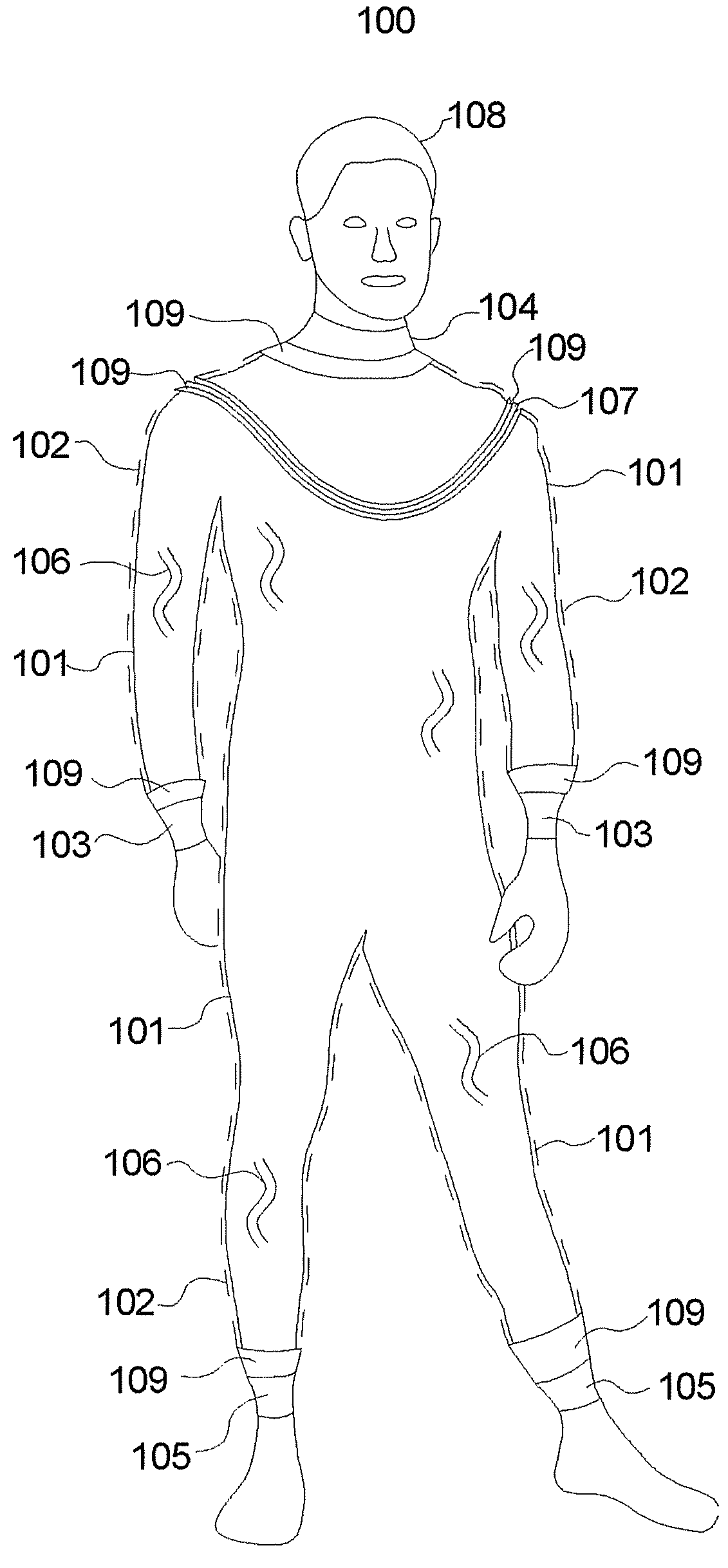

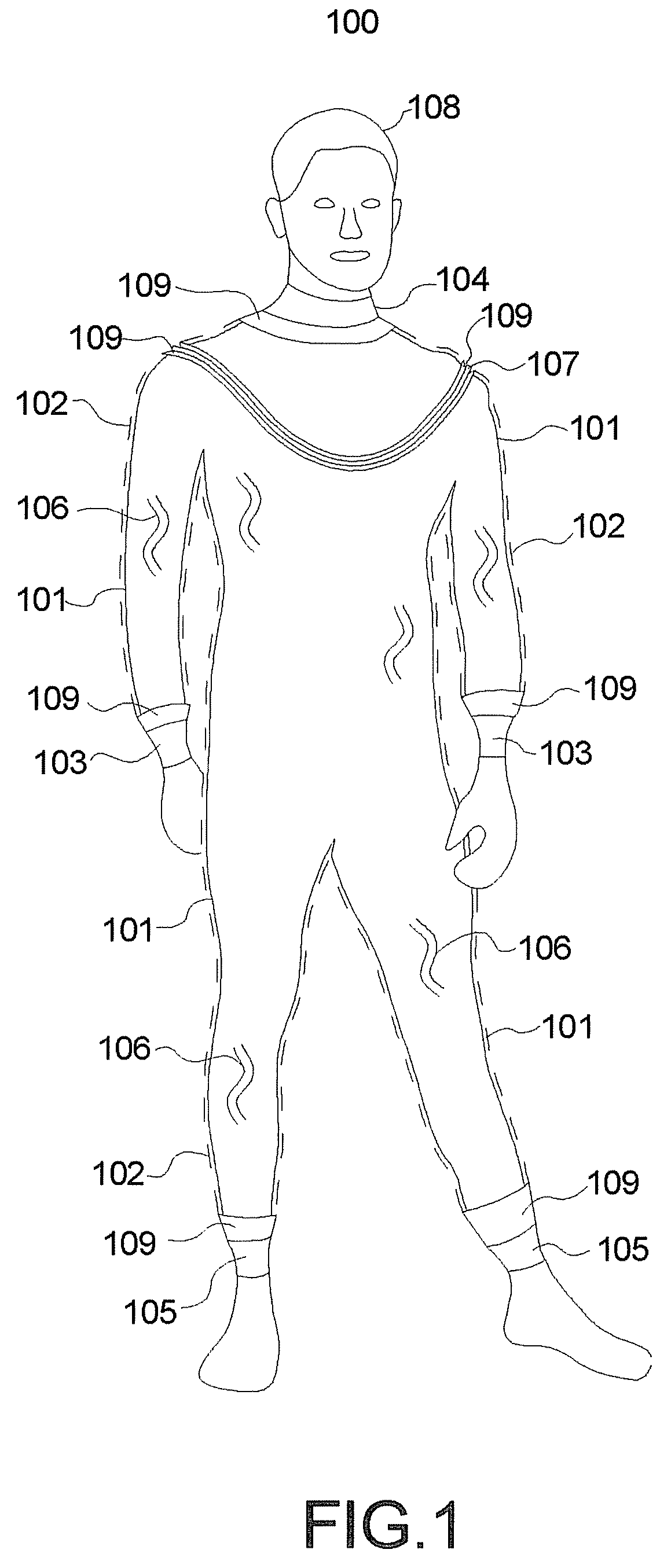

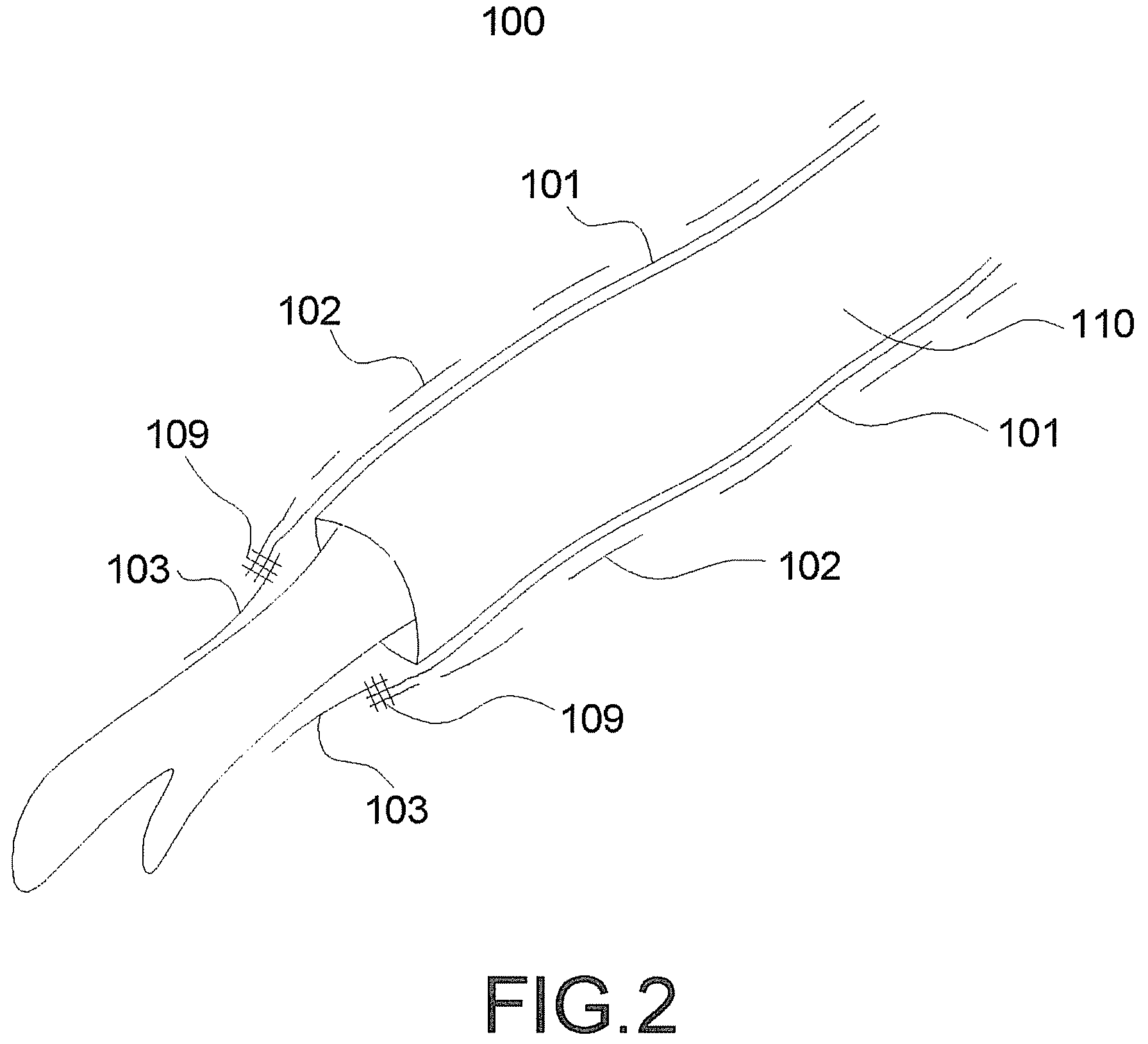

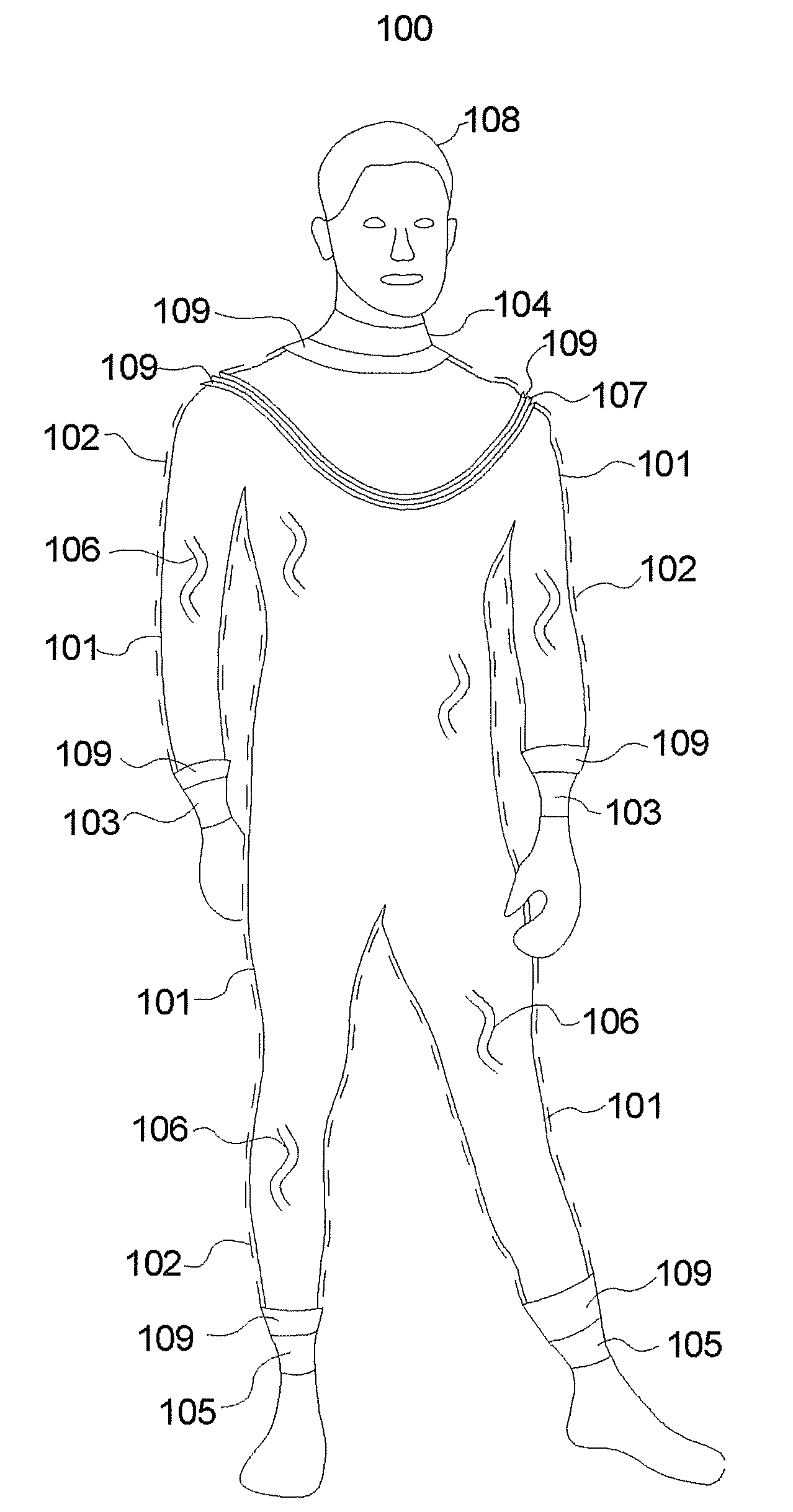

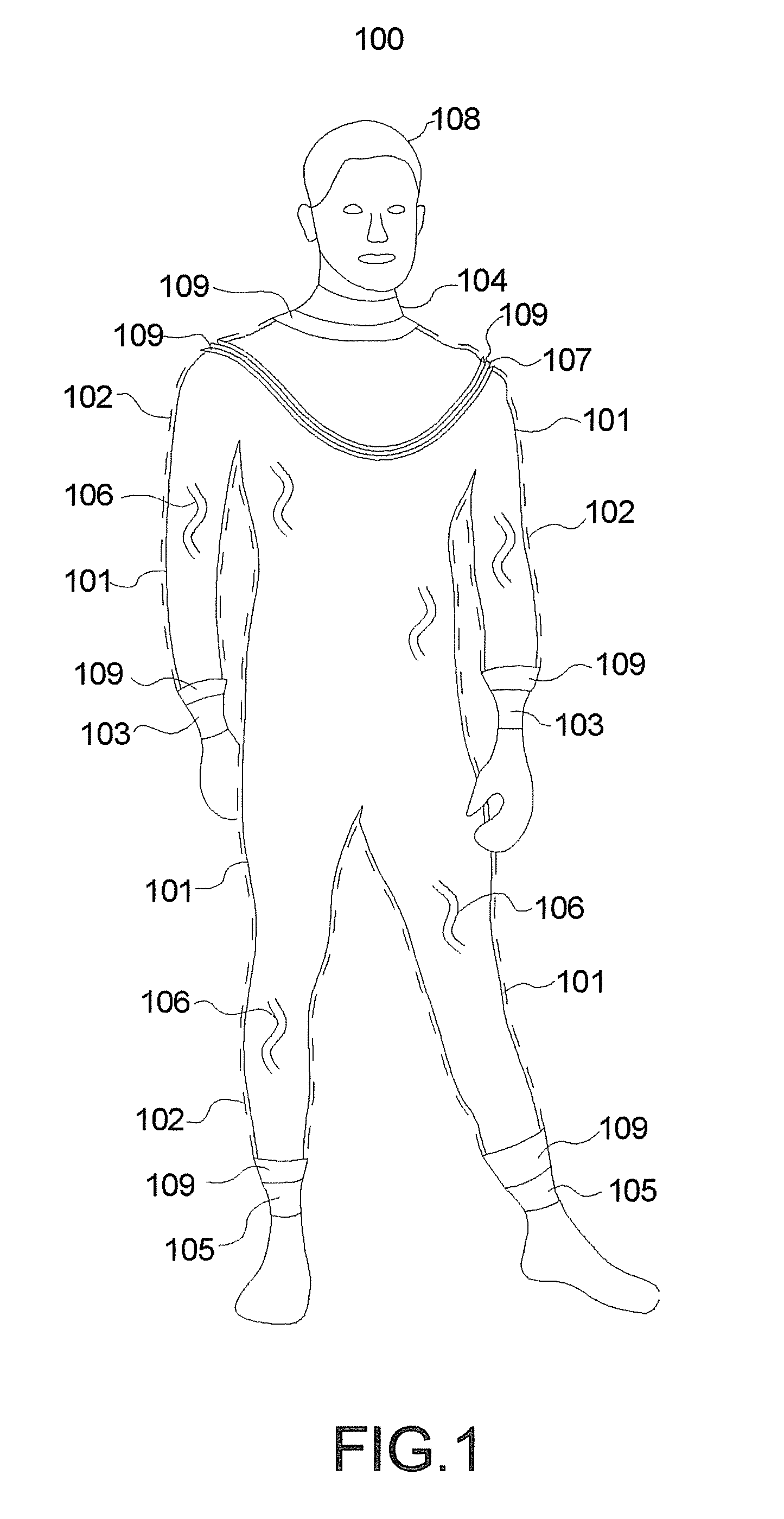

Split skin dry-suit

ActiveUS7631363B2Minimizes shiftingProtective garmentSpecial outerwear garmentsEngineeringBiomedical engineering

Owner:WHITES MFG

Cargo restraint system and method with enhanced peel strength

ActiveUS20100322736A1Enhanced peel strength characteristicImprove securityFilm/foil adhesivesSynthetic resin layered productsAdhesiveFront edge

A cargo restraint system and method with enhanced peel strength characteristics the restraint system including laminated load restraining strips with a layer of adhesive to adhere the restraining strip to a container wall surface having a thickness of approximately greater than 1.6 and less than 3.0 millimeters. The load restraint method for securing cargo within transport containers wherein an angle θ of attachment between a side wall of a container and a reinforcing strip of material attached to the side wall is maintained at approximately 15 degrees or less in accordance with the formula B≦cot θ•A, where θ is the angle formed between an exterior surface of said load restraining strip and an interior plane of the lateral wall surface of the transport container “A” is the distance from a front edge of a load to an adjacent side wall and “B” is the distance along the wall of the container behind the point of contact of the restraining strip with an edge of the load to be restrained.

Owner:MBULL HLDG LLC

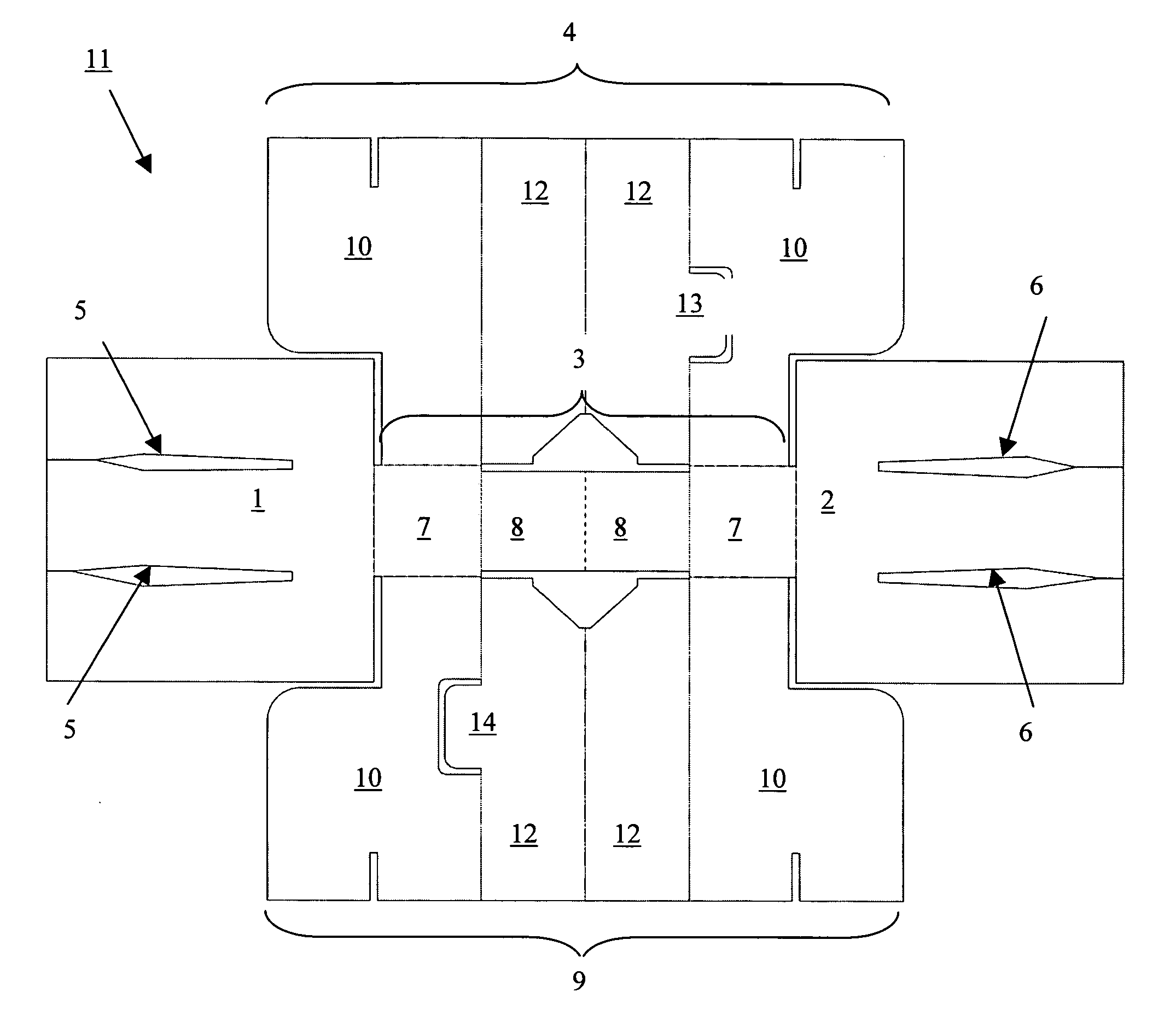

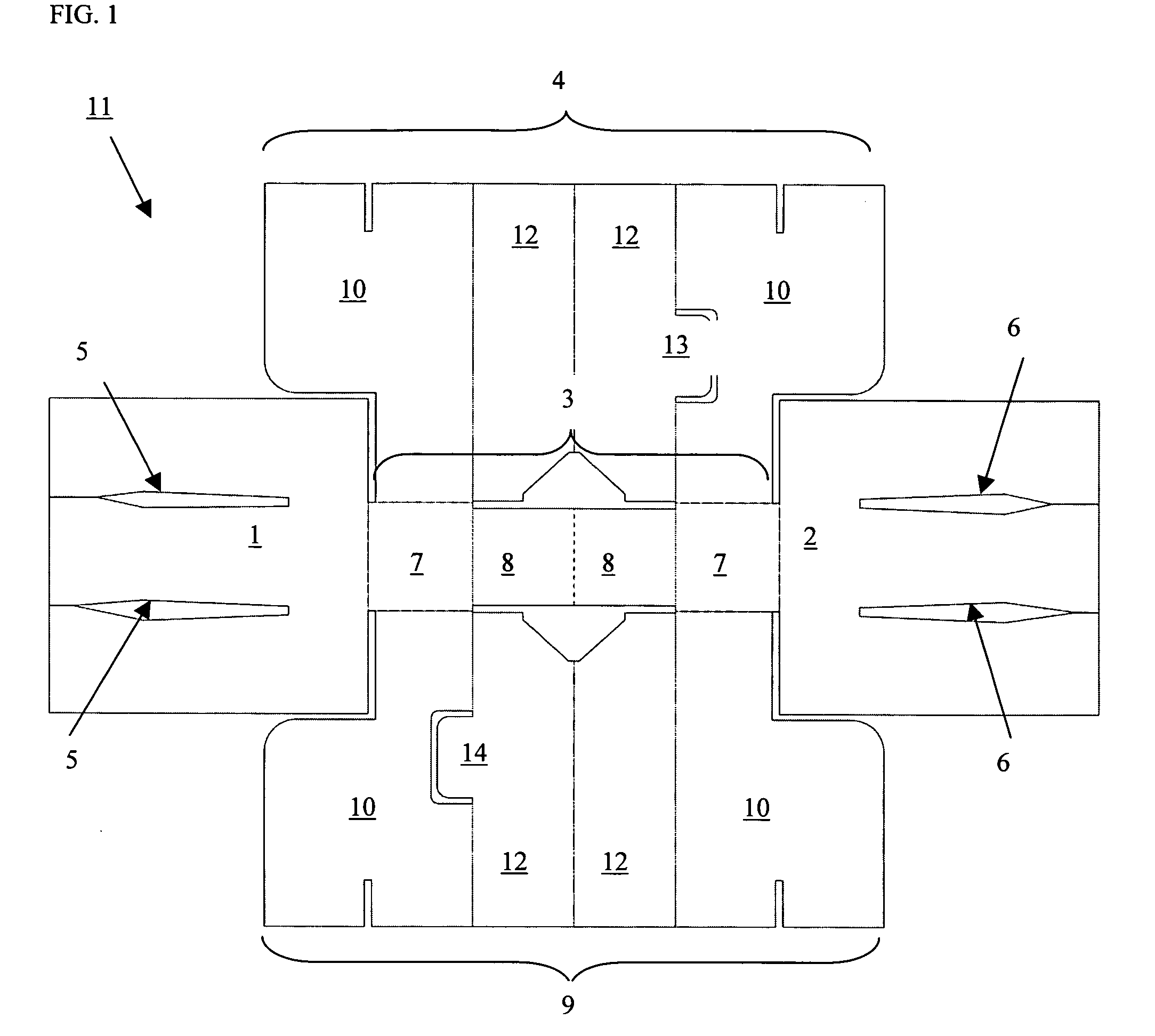

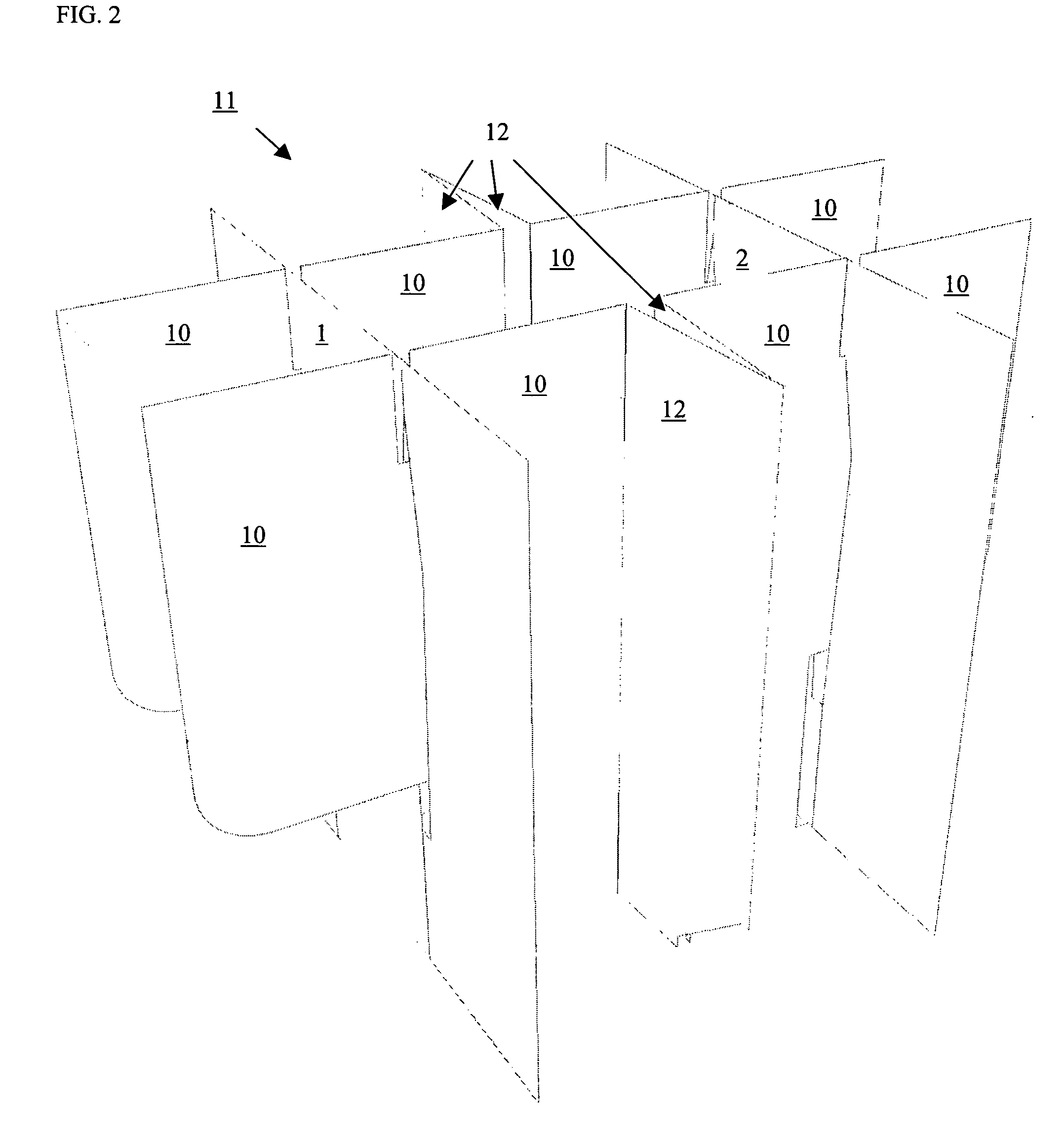

Box partition

InactiveUS20050230463A1Minimizes shiftMinimizes shiftingRigid containersInternal fittingsEqual sizeEngineering

A partition structure formed from a unitary sheet of paperboard to provide a plurality of cells for use within a package or container. The structure can be folded in such a way as to provide 12 or more cells of equal size or 6 cells of one size and 3 cells of a larger size.

Owner:CAIN SELWYN

Split skin dry-suit

ActiveUS20070186326A1Minimizes shiftingProtective garmentSpecial outerwear garmentsBiomedical engineeringCosmetic appearance

Owner:WHITES MFG

Method of imparting mattress gripping stretchability to a mattress cover

A fitted mattress cover for enveloping the top, side and end surfaces of a mattress is constructed to accommodate a range of mattress peripheral sizes and thicknesses. The construction utilizes composite end panels which include stretch end panels covering lower partial portions of the mattress end surfaces and which impart recovery forces to effectively grip the mattress and thereby minimize the shifting of the cover relative to the mattress. At the same time, the look and feel of the mattress covering, which may be of importance especially in the case of a fitted sheet, is improved, by virtue of the fact that the side panels can be formed as uninterrupted unitary extensions of the material forming the top side panel, or other material based upon aesthetic considerations, as can upper partial portions (extension end panels) of the composite end panels. In a related aspect, stretchability of the mattress cover skirt may be imparted in a post-manufacture heat treatment finishing step, which may include a laundry wash and dry cycle.

Owner:LOUISVILLE BEDDING CO INC

Cargo restraint method and system with enhanced shear strength

ActiveUS20100310336A1Improve securityMinimize travelSynthetic resin layered productsFlexible elementsEngineeringFront edge

A load restraint method and system for securing cargo within transport containers wherein the angle θ of attachment between a side wall of a container and a reinforcing strip of material attached to the side wall is maintained at 15 degrees or less in accordance with the formula B≦cot θ·A, where θ is the angle formed between an exterior surface of said load restraining strip and an interior plane of the lateral wall surface of the transport container “A” is the distance from a front edge of a load to an adjacent side wall and “B” is the distance along the wall of the container behind the point of contact of the restraining strip with an edge of the load to be restrained.

Owner:MBULL HLDG LLC

Ultra sheer natural latex insertable condom with ribbing and snap holes

InactiveUS20050081864A1Easy to useLow costMale contraceptivesFemale contraceptivesBiomedical engineeringAnchor point

An insertable condom comprises a sheath of material formed to enclose a volume leaving an opening at one end, a ribbed member connected to the sheath of material, and an anchor point attached to the ribbed member. A wearable prophylactic system may be employed with the insertable condom, said system comprising a garment having a strap with an engagement device. A method for manufacturing a prophylactic device comprises forming a first portion of a prophylactic device using a poured molding process and subjecting the first portion of the prophylactic device to a dip molding process to add a second portion to the prophylactic device.

Owner:CARNEVALE JERRY ALLEN

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com