Bipolar Transistor with Pseudo Buried Layers

a bipolar transistor and pseudo-buried layer technology, applied in the direction of semiconductor devices, basic electric elements, electrical equipment, etc., can solve the problems of not meeting the rf requirement, the advanced cmos process is quite expensive, and the cost of materials, etc., to achieve less parasitic effect, less device size, and less photo mask layer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

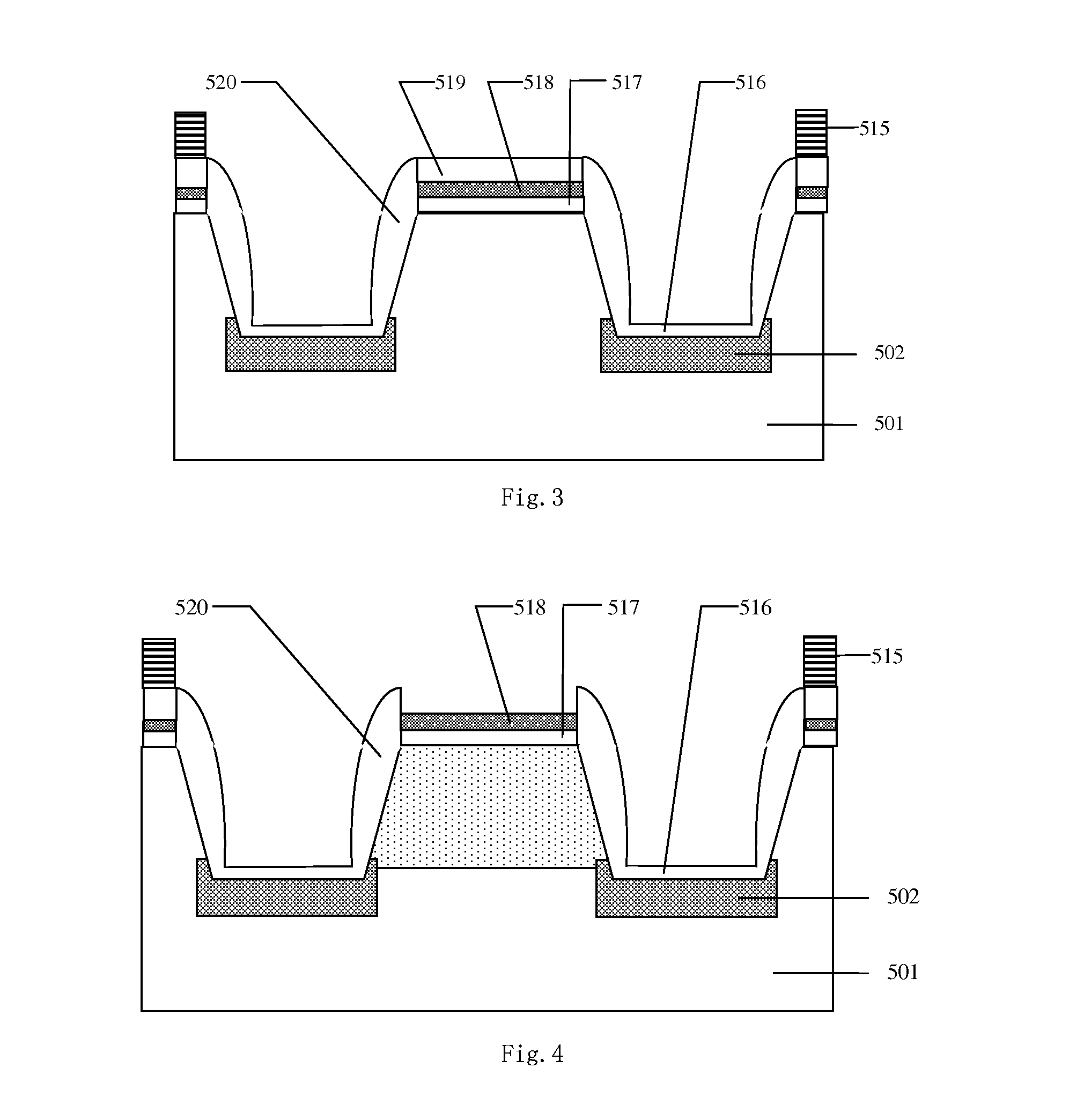

[0018]FIG. 2 is cross sectional view showing the structure of the bipolar transistors in the invention. On substrate 501, the active area is isolated by field oxide 503 in shallow trenches. The transistor comprises a collector 514, a base 511 and an emitter 510.

[0019]The collector 514 is formed by single or multiple implants of first electric type impurity into active area. At the bottom of collector 514, two pseudo buried layers 502 at STI bottoms link up to be buried layer. For active critical dimension less than 0.5 micron, two pseudo buried layers 502 overlap in active by lateral diffusion and become collector 514's buried layer. If active critical dimension is larger than 0.5 micron, the implant into active with the same impurity type as pseudo buried layer 502 is implemented to link two pseudo buried layers. The implant depth is almost same as that of pseudo buried layers. The deep trench contacts 504 are etched through the field oxide 503 above pseudo buried layers 502 to con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com