Quad flat no-lead chip carrier with stand-off

a flat no-lead, chip carrier technology, applied in the direction of printed circuit, sustainable manufacturing/processing, final product manufacturing, etc., can solve the problems of qfn misalignment with pcb pads, limit the ability of solder to wet, and affect the yield, so as to improve the yield of assembly to a substrate, improve the yield, and increase the solder area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

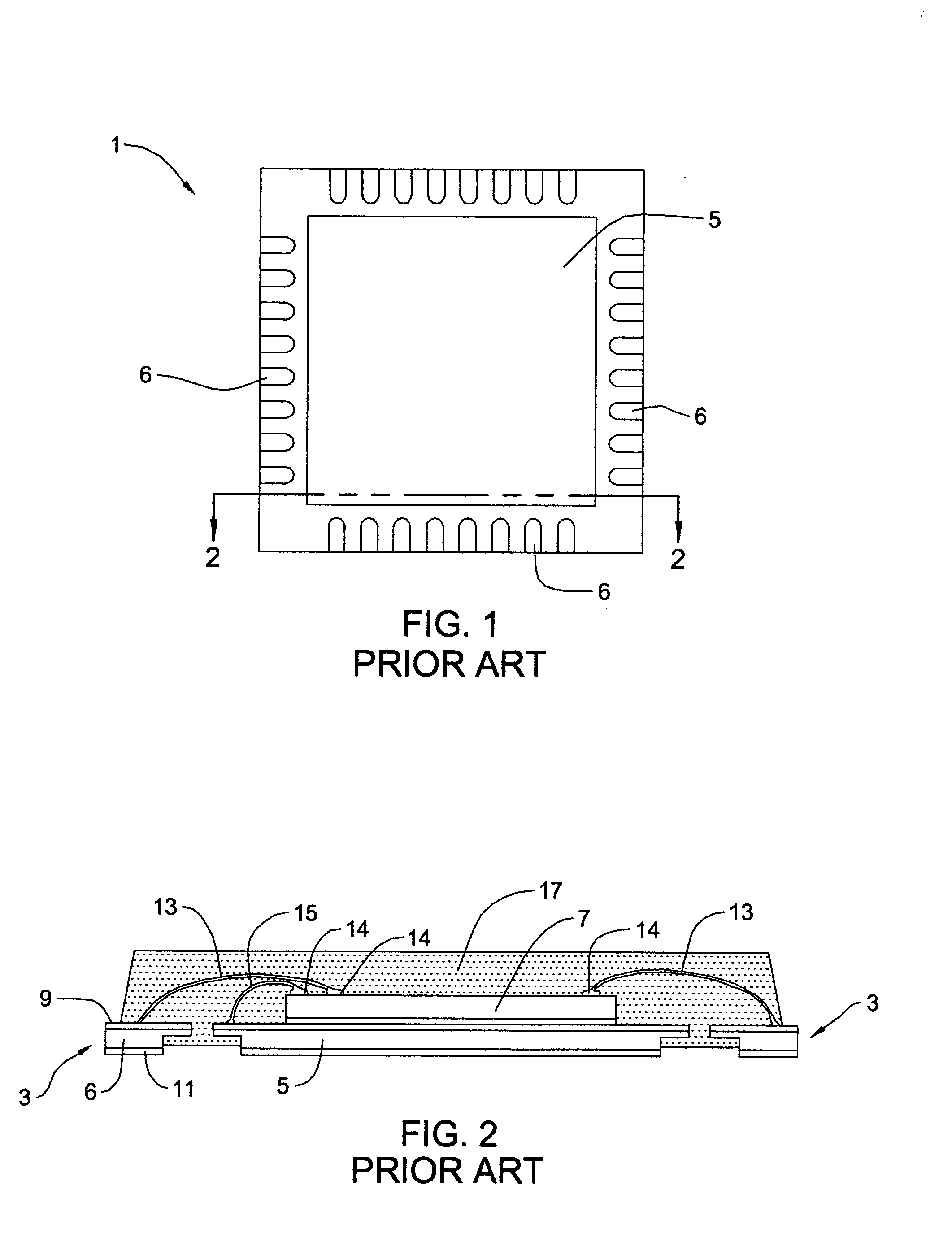

[0023]The bottom of a conventional QFN chip carrier is shown in FIG. 1. This is the side of the carrier that attaches to a substrate, such as, a PCB. Typically, the QFN chip carrier comprises a leadframe made from a flat copper plate. The leadframe 1 in FIG. 1 comprises a pattern that includes copper die paddle 5 and leads 6. The pattern of the paddle and leads may be etched or stamped out of the flat copper plate.

[0024]FIG. 2 shows a cross-sectional view of the QFN chip carrier of FIG. 1 taken along line 2-2. As shown, copper leads 6 are plated on the top with a layer 9 of, for example, silver and on the bottom with a layer 11 of, for example, solder to thereby form lead contacts 3. In this regard, it can be seen that the surfaces of die paddle 5 are also similarly plated on top and bottom at the same time leads 6 are plated. Wires 13, made of gold for example, connect contact pads 14 on chip 7 to lead contacts 3. Similarly, gold wire 15 forms a ground connection. As shown, this as...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com