Location-specific NAND (ls NAND) memory technology and cells

a technology of location-specific nand and memory cells, which is applied in the direction of digital storage, instruments, semiconductor devices, etc., can solve the problems of complex and costly technology, cell technology never mainstream non-volatile cells, and difficult if not impossible complete removal of charge stored in nitrid

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

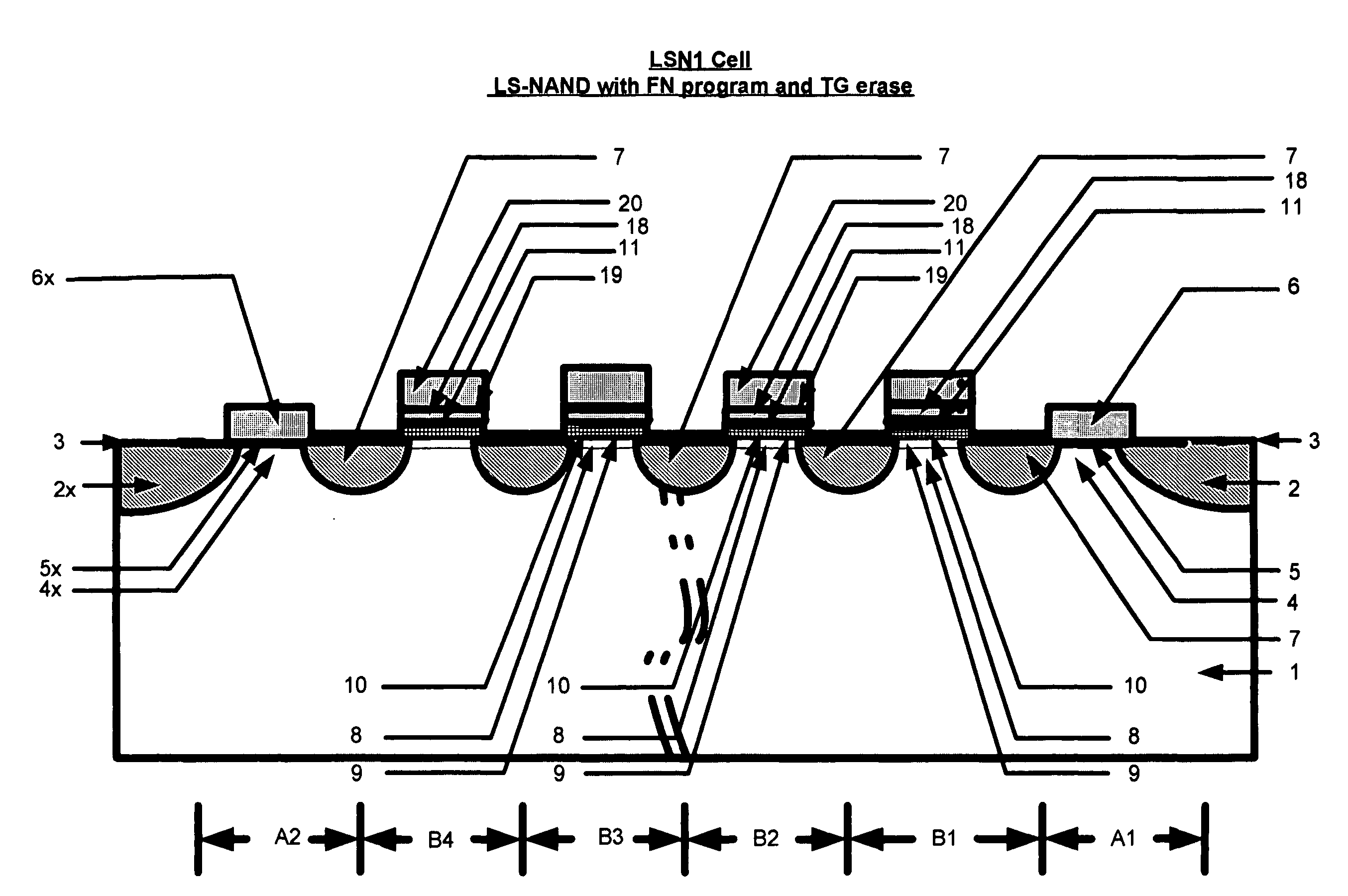

[0130] The current disclosure of LS based NAND cells are explained using two separate types of NAND cells. The difference between the two is in the programming method used. The cell shown in FIG. 5 uses FN Tunneling for programming the selected storage gates, while the cell shown in FIG. 6 uses Low-current Channel Hot Electron for programming the selected storage gates. In both cases the cells or arrays are erased using the TG to generate and supply the carriers, typically holes to neutralize the stored electron charge of the cell.

[0131] In the first instance, FIG. 5 is a NAND cell which is programmed by FN tunneling and erased by TG method. The NAND cell shown comprise of four storage gates or segments (B1 to B4) and two select gates (A1 and A2) that help isolate the cell if it is not a selected cell in the array. The four gates are shown as exaple and should not be construed as limiting the number of gates that can be implemented in the cell. The storage gate number can be increa...

PUM

| Property | Measurement | Unit |

|---|---|---|

| voltage | aaaaa | aaaaa |

| voltage | aaaaa | aaaaa |

| voltage | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com