Method and resulting structure for manufacturing semiconductor substrates

a technology of semiconductor substrates and manufacturing methods, applied in the direction of semiconductor/solid-state device details, polycrystalline material growth, crystal growth process, etc., can solve the problems of compound semiconductor wafers being more prone to damage, compound semiconductor materials are still relatively expensive compared to circuits, and other limitations of compound semiconductor materials, so as to reduce the possibility of breakage, reduce the possibility of damage, and reduce the effect of fragileness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

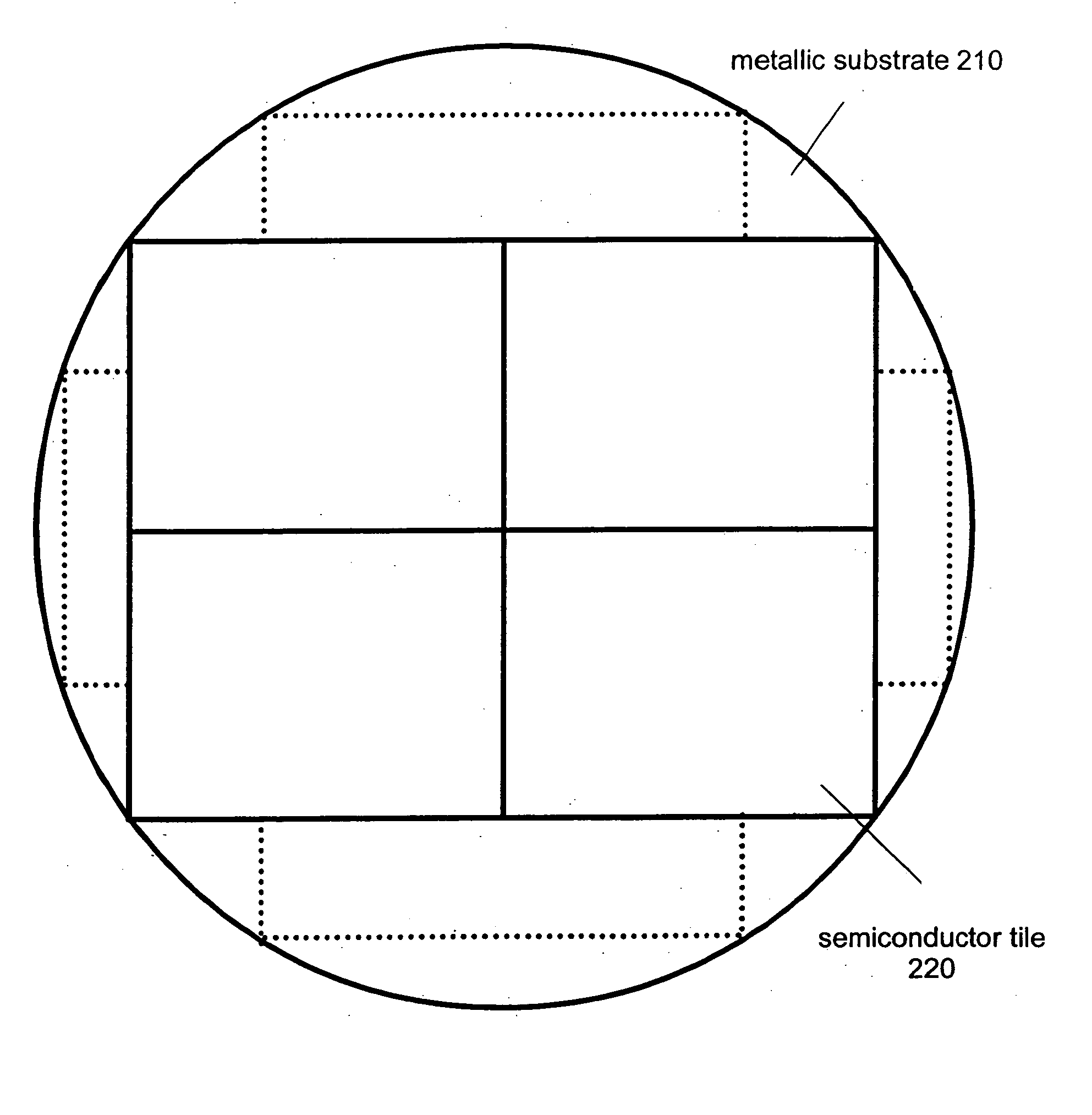

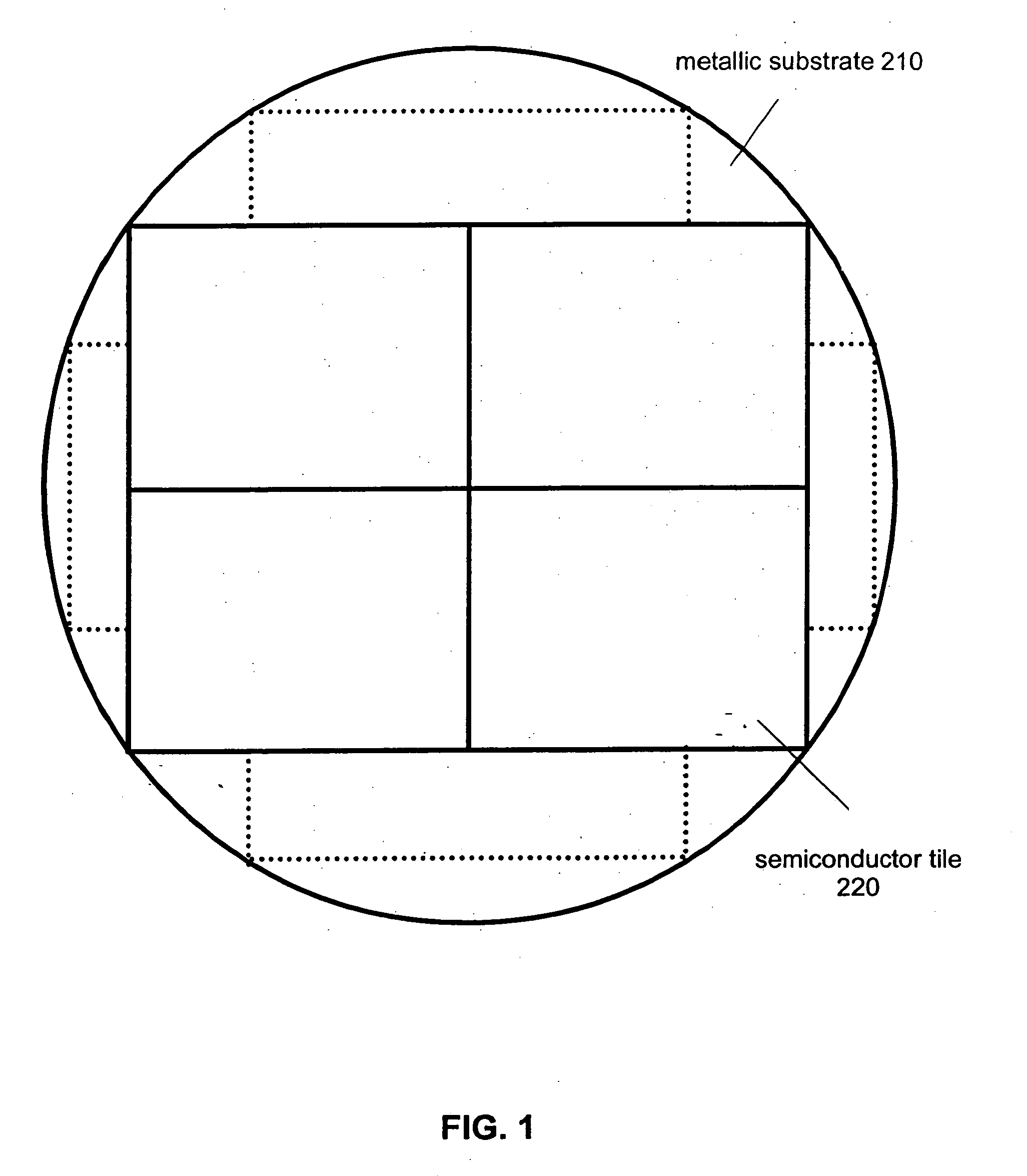

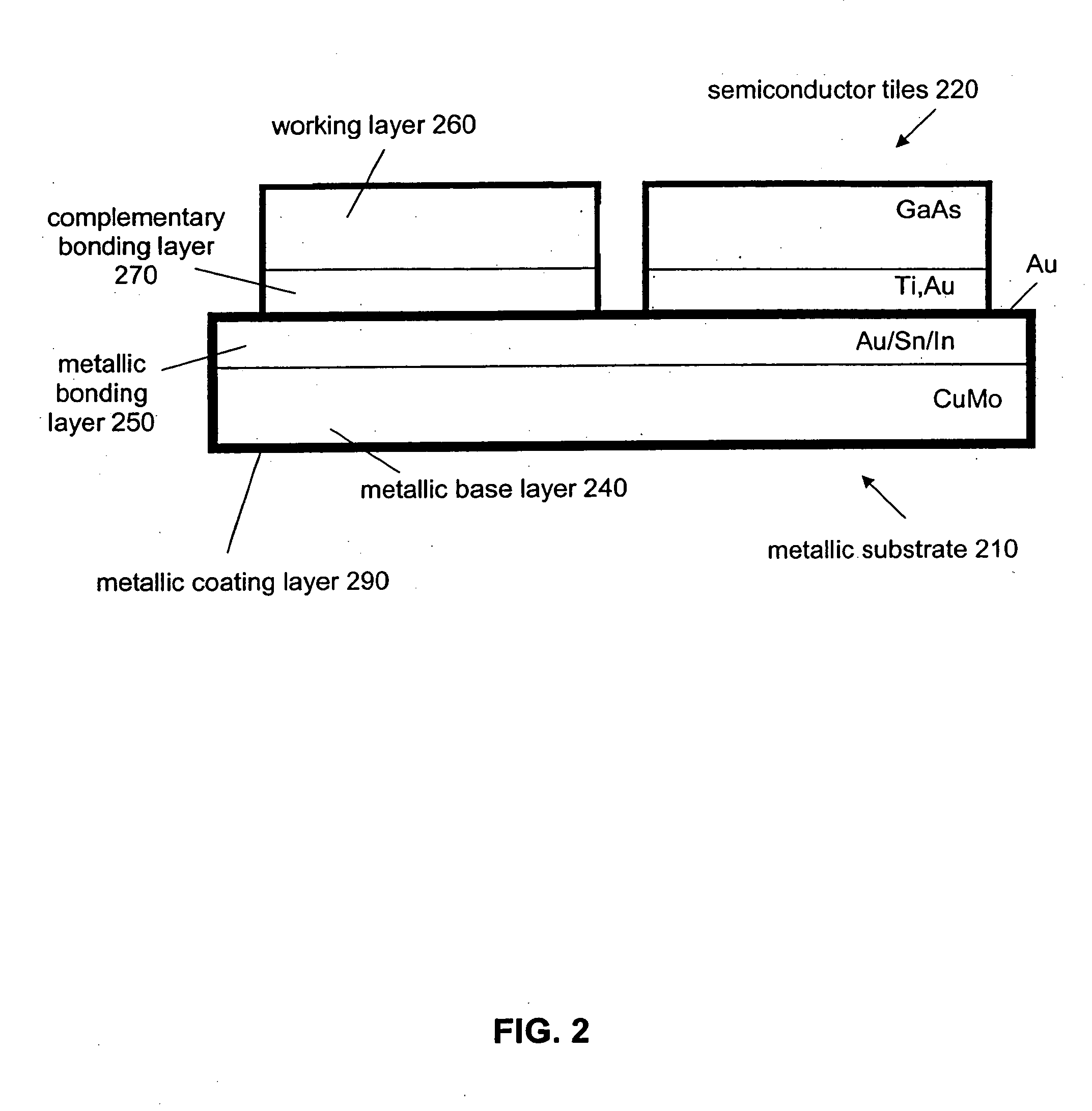

[0032] According to the present invention, techniques for manufacturing substrates are provided. More particularly, the invention provides a method and device for improved semiconductor substrates to form advanced semiconductor devices. Merely by way of example, the invention has been applied to a metallic substrate that includes a plurality of panels and / or tiles, which are bonded on the substrate, for the manufacture of the advanced semiconductor devices. But it would be recognized that the invention has a much broader range of applicability.

[0033] A semiconductor wafer composite is described herein. The composite is well suited to fabrication of compound semiconductor devices. Further, the composite has particular application in the context of large scale production of such devices. The semiconductor wafer composite from which the individual semiconductor devices are fabricated is first described, followed by a procedure for high volume production of semiconductor devices using ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

| diameters | aaaaa | aaaaa |

| diameters | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com