Formation of low resistance via contacts in interconnect structures

a technology of interconnect structure and contact, which is applied in the direction of basic electric elements, semiconductor/solid-state device manufacturing, electric apparatus, etc., can solve the problems of fatal ic failure mode, increased via resistance, and associated fabrication problems with prior art structures, and achieve low via contact resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

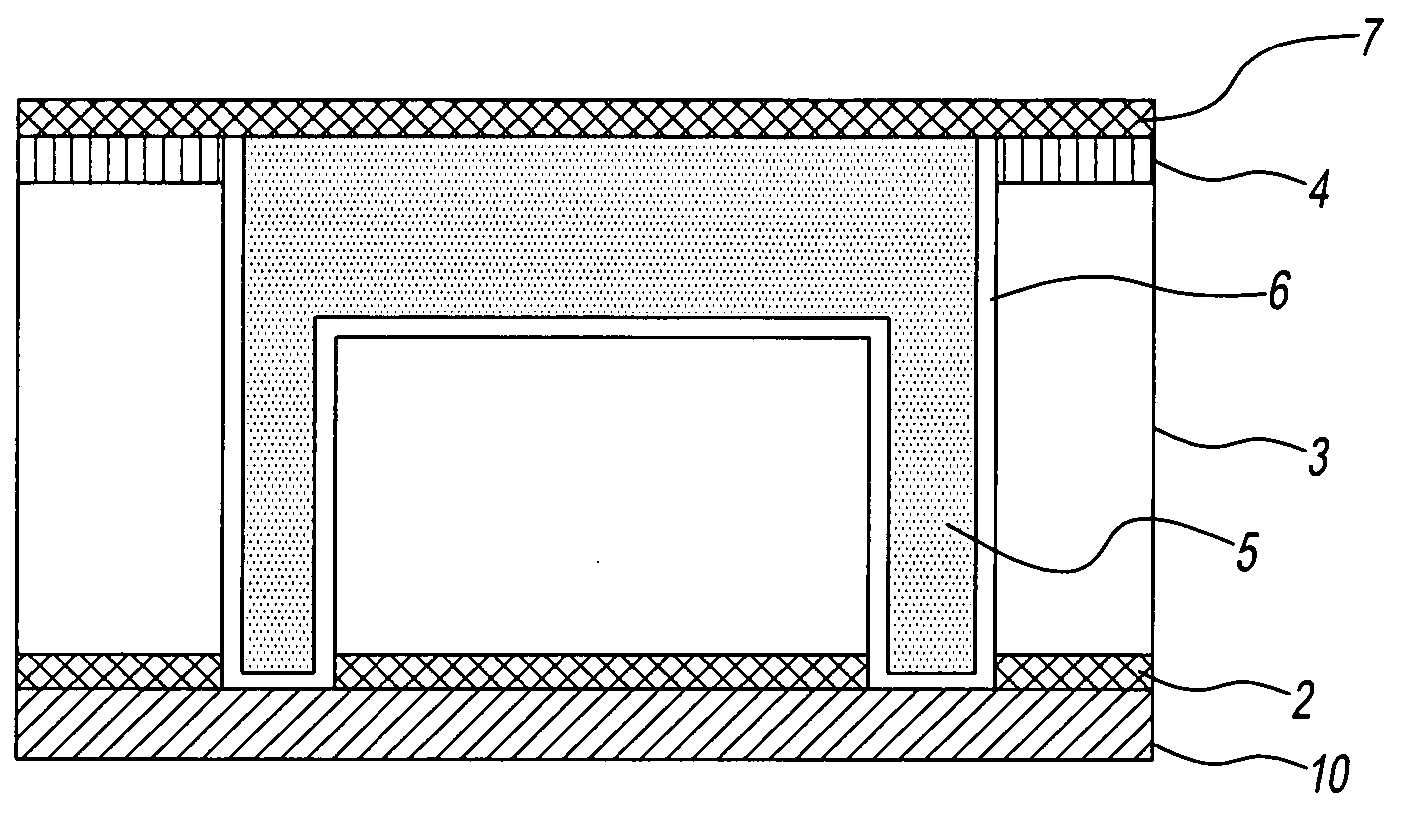

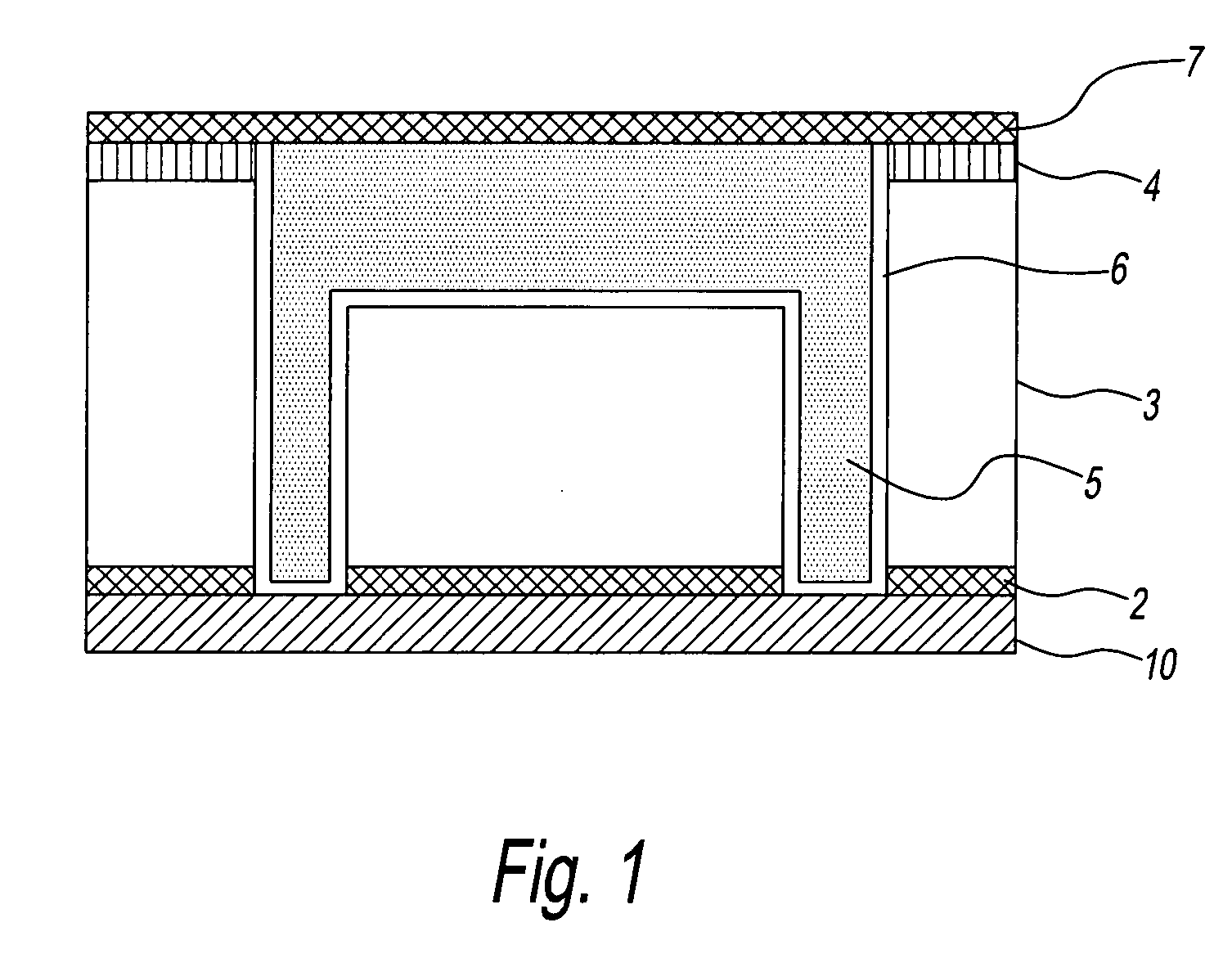

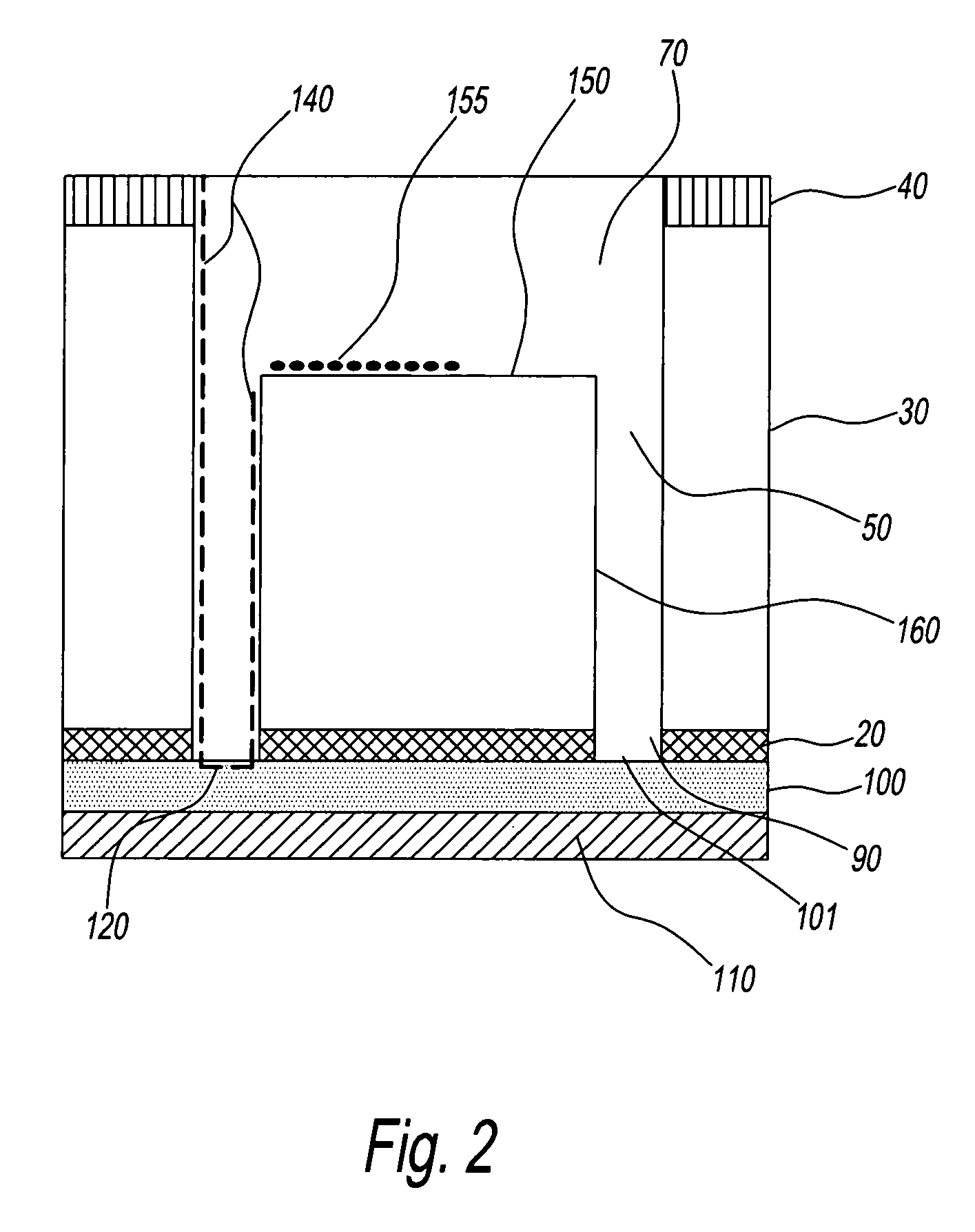

[0035] The present invention provides a non-destructive pre-clean process methods for liner / barrier deposition on low-k dielectrics.

[0036] In general, an integrated circuit will have interconnect levels, each level including metallic lines and vias that are of a dual damascene (via plus next level conductor) wiring interconnect structure for use on the IC chip. The metallic lines and vias are composed of the same or different conductive material. Suitable materials for use herein include, but are not limited to, W, Cu, Al, Ag, Au and alloys thereof and the like. A particularly preferred material is Cu.

[0037] The condensable cleaning agent (CCA) can be a reducing agent; metal based reducing agent, metal hydride; mixed metal hydride such as, LiAIH, molecular source of fluorine or a source of hydrogen, or a source of both hydrogen and silicon.

[0038] Examples of the latter include, but are not limited to disilane; trisilane; tetrasilane and other condensable silanes.

[0039] Molecular...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com