Spectral shaping dynamic encoder for a dac

a dynamic encoder and encoder technology, applied in the field of multi-bit digitaltoanalog encoders, can solve the problems of modulators employing 1-bit dacs, unable to correct errors in feedback loops, and unable to achieve only relatively limited resolution for 1-bit data converters

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

The invention relates to a mismatch-shaping, dynamic encoder suitable for use in a multiple-bit digital-to-analog converter (DAC). While the drawings and the specification below describe exemplary embodiments of best modes of practicing the invention, those of skill in the art will appreciate that other modes of practicing the invention are possible. The claims appended to this specification therefore define the true scope of the invention.

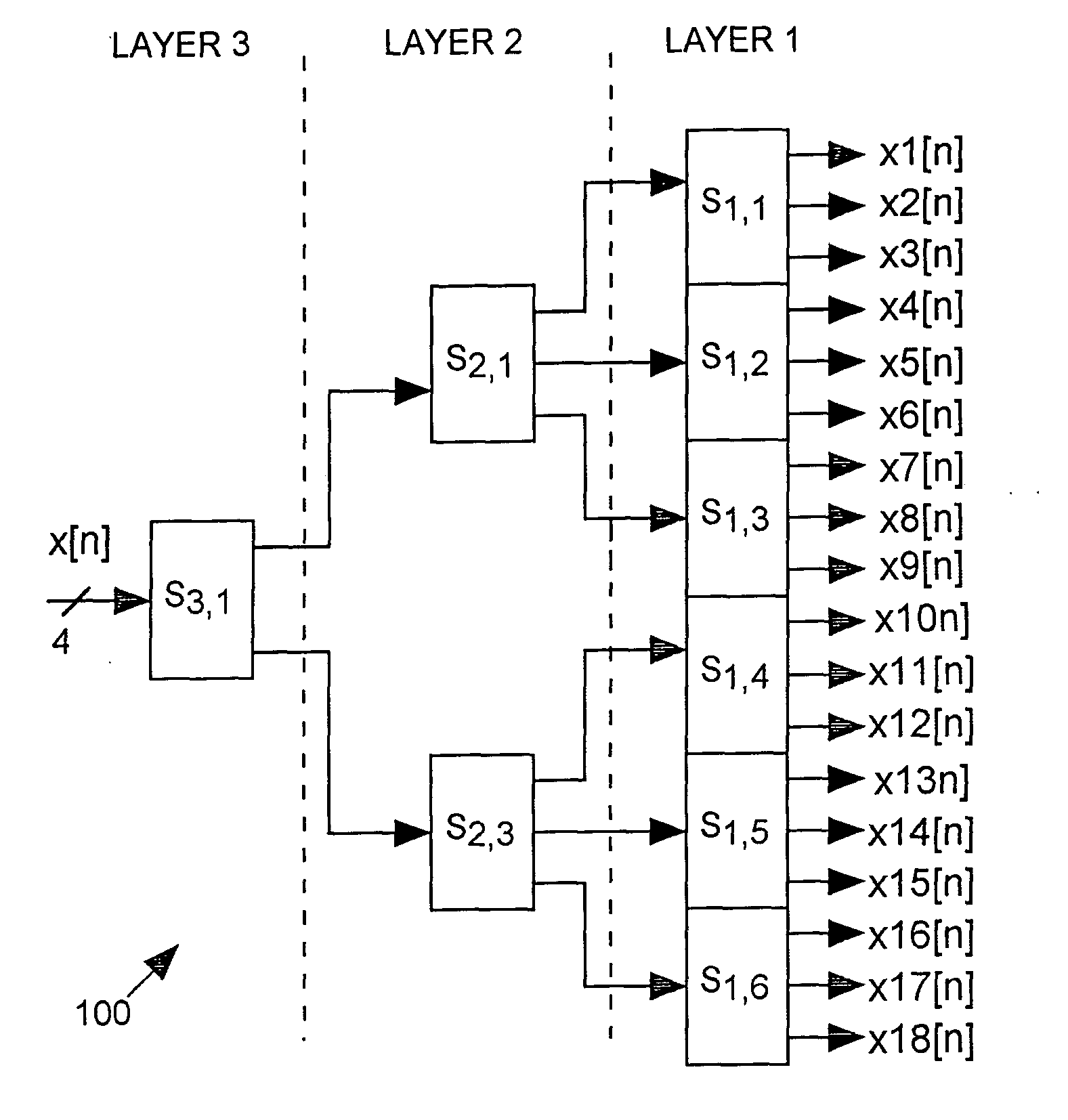

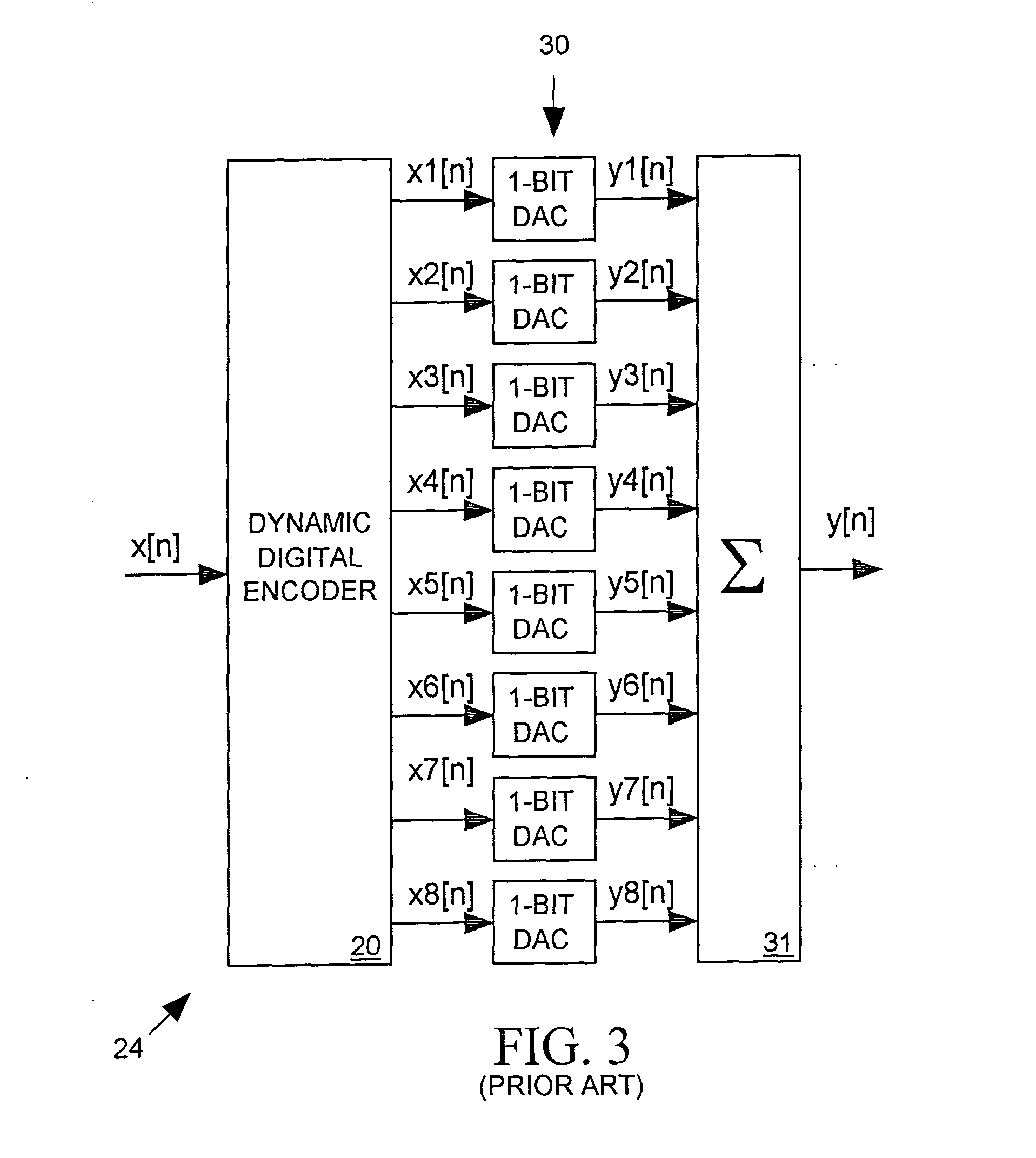

As discussed above in connection with FIG. 3, a dynamic digital encoder is useful in a multiple bit digital-to-analog converter (DAC) 24 including a summing amplifier 31 for summing outputs of a set of single-bit DACs 30 to produce an analog output signal y[n]. A dynamic digital encoder 20 converts an input word x[n] into an output word {x1[n]-x8[n]} having a number of bits of value 1 equal to the value of input word x[n]. By appropriately scrambling bit-patterns of successive words {x1[n]-x8[n]} supplying input bits to DACs 30, dynamic digital...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com