Igfet with silicide contact on ultra-thin gate

a technology of igfet and contact, which is applied in the direction of semiconductor devices, electrical equipment, transistors, etc., can solve the problems of difficult to obtain consistent threshold voltages, poor quality of refractory metal oxides, and inability to provide suitable replacements for polysilicon, etc., to achieve a well-controlled doping profile and high-miniaturized igfet

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] In the drawings, depicted elements are not necessarily drawn to scale and like or similar elements may be designated by the same reference numeral throughout the several views.

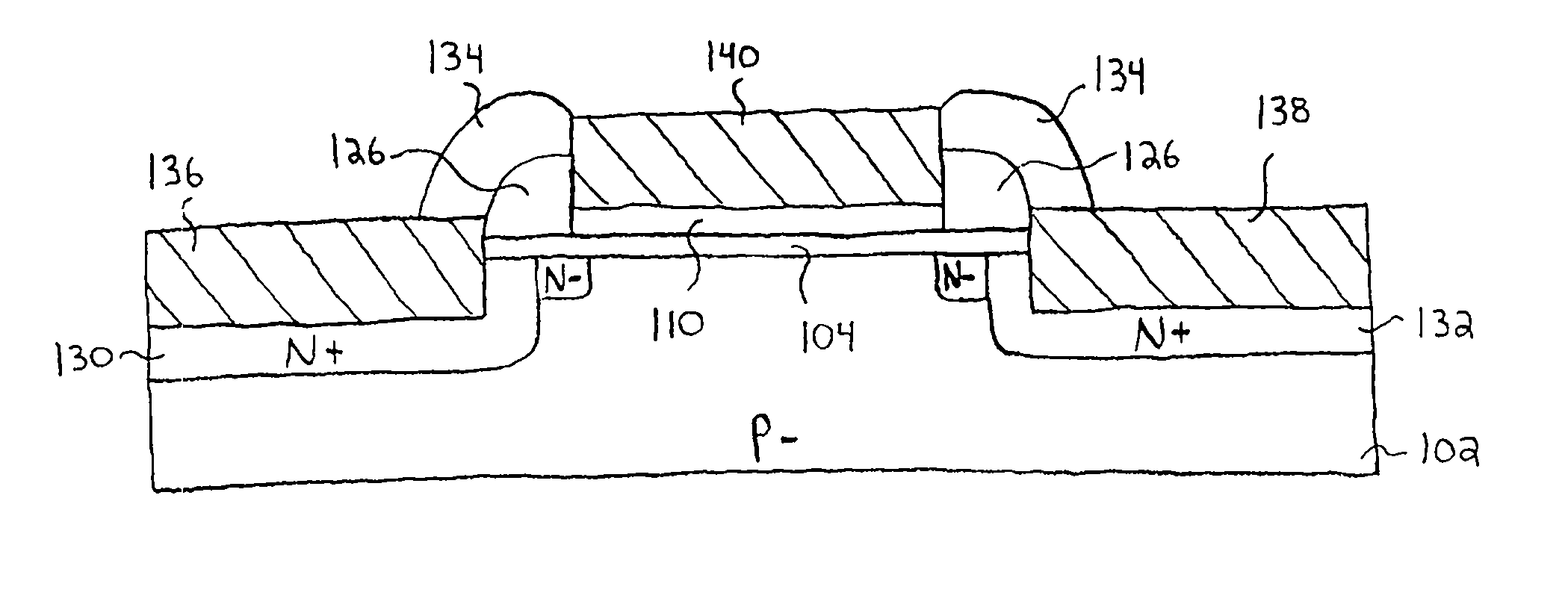

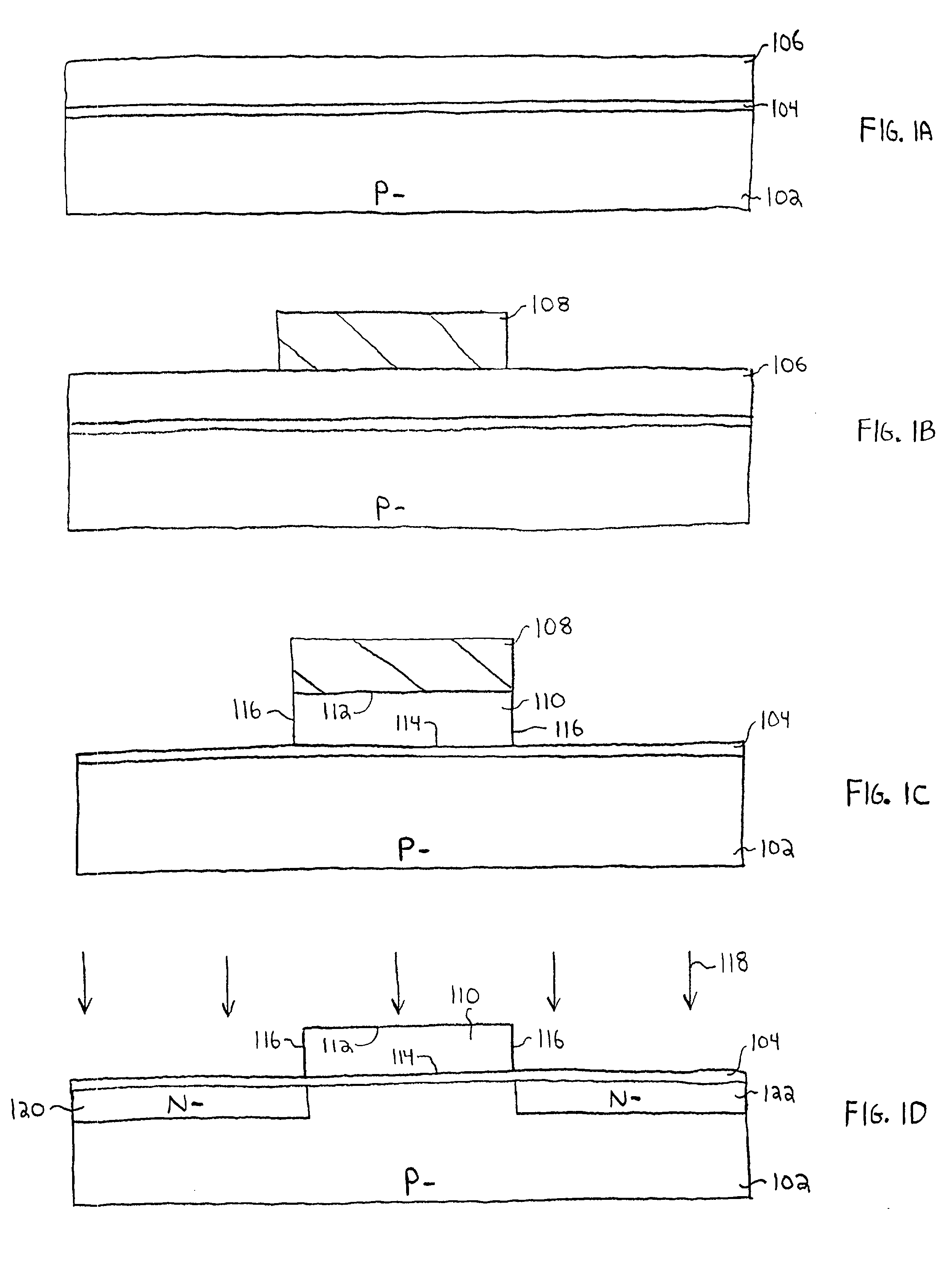

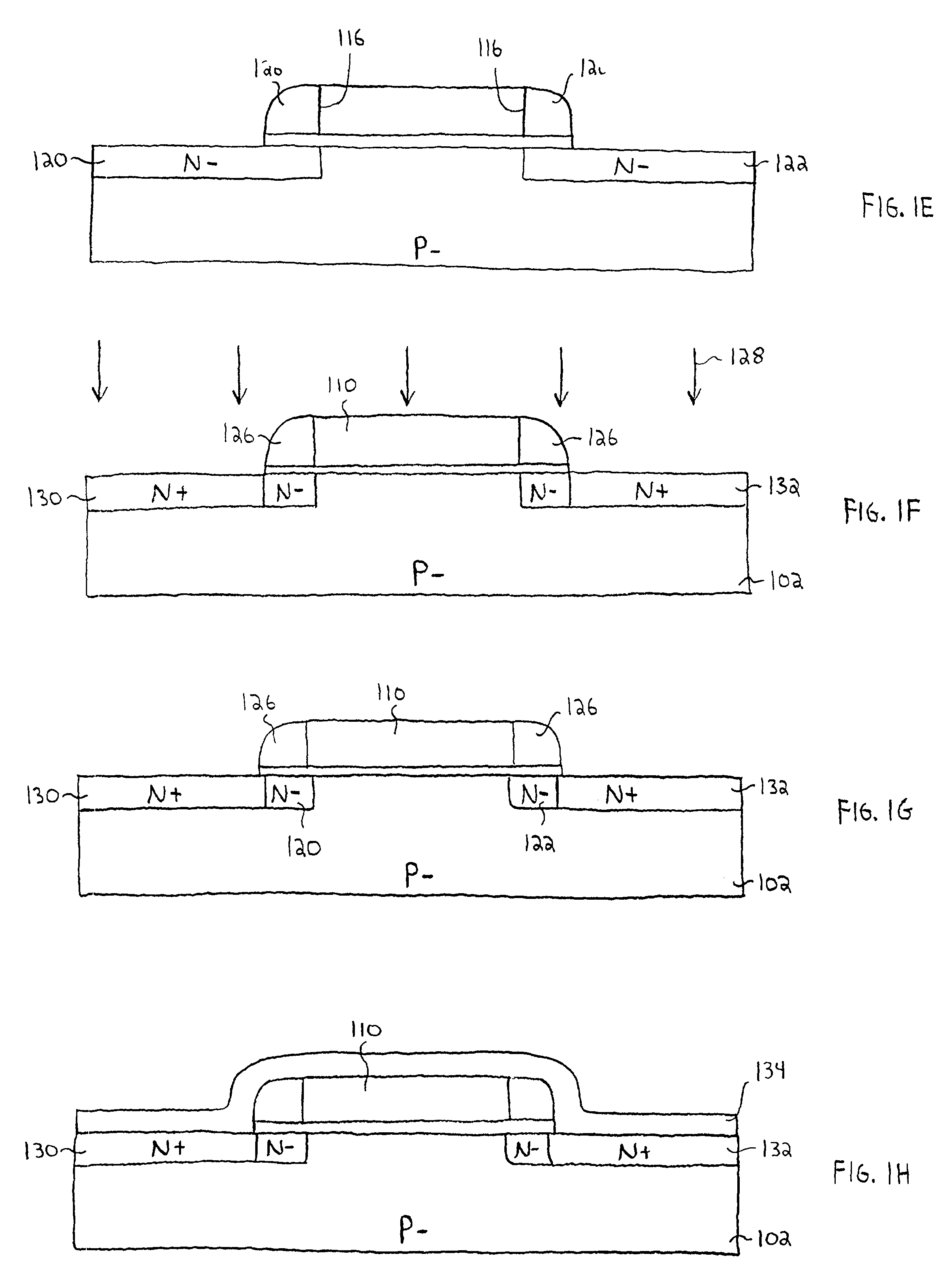

[0023] In FIG. 1A, silicon substrate 102 suitable for integrated circuit manufacture includes a P-type epitaxial surface layer disposed on a P+ base layer (not shown). The epitaxial surface layer provides an active region with a boron background concentration on the order of 1.times.10.sup.16atoms / cm.sup.3, a orientation and a resistivity of 12 ohm-cm. Substrate 102 can be subjected to a threshold voltage implant, a punch-through implant, and a well implant as is conventional. For convenience of illustration, dielectric isolation such as field oxides between adjacent active regions is not shown. A blanket layer of gate oxide 104, composed of silicon dioxide (SiO.sub.2), is formed on the top surface of substrate 102 using tube growth at a temperature of 700 to 1000.degree. C. in an O.sub.2 containing amb...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com