Method for reducing wafer harm caused by shallow slot insulation chemical mechanical polishing technique

A chemical-mechanical, wafer-based technology used in semiconductor/solid-state device manufacturing, electrical components, circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

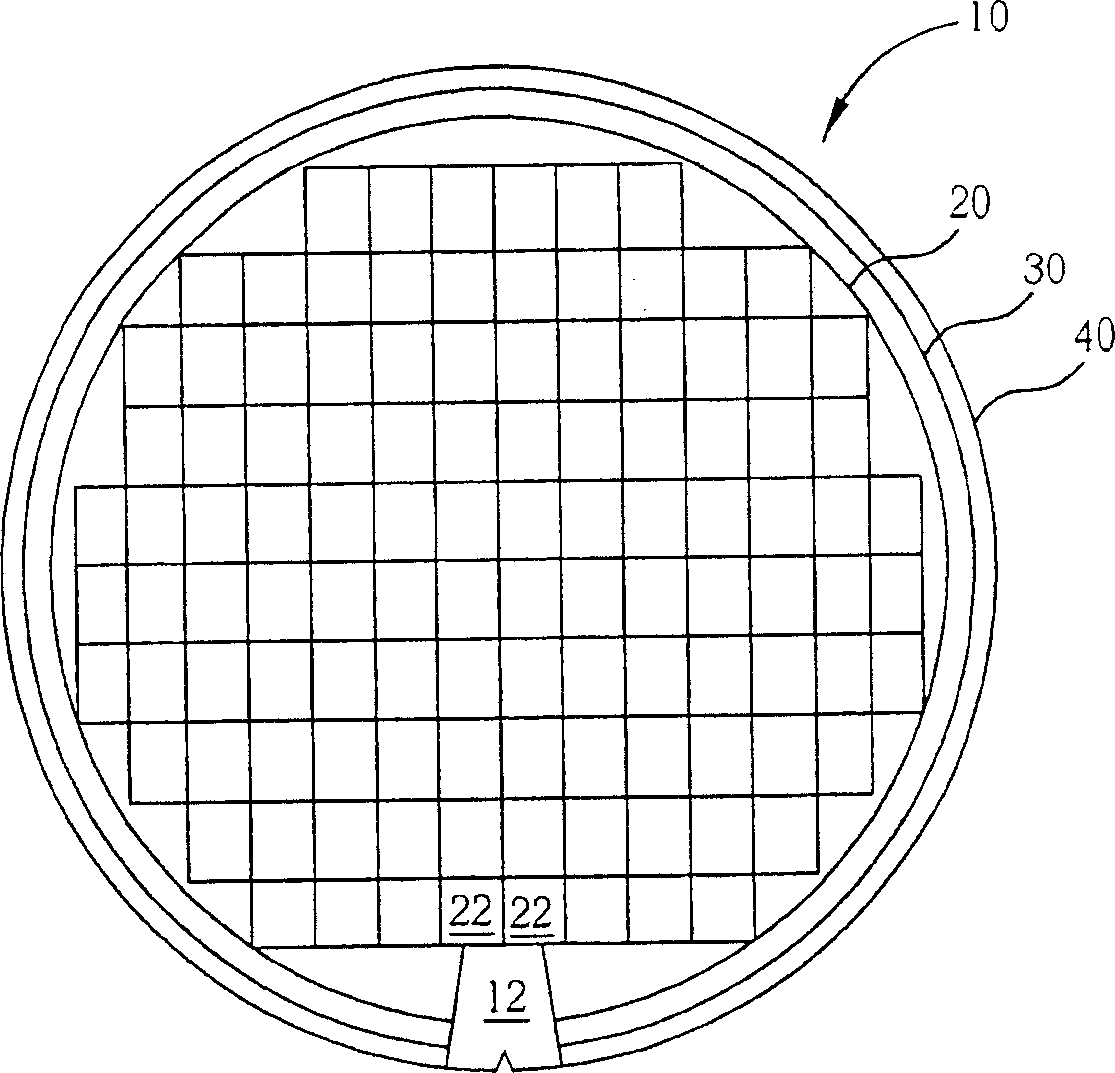

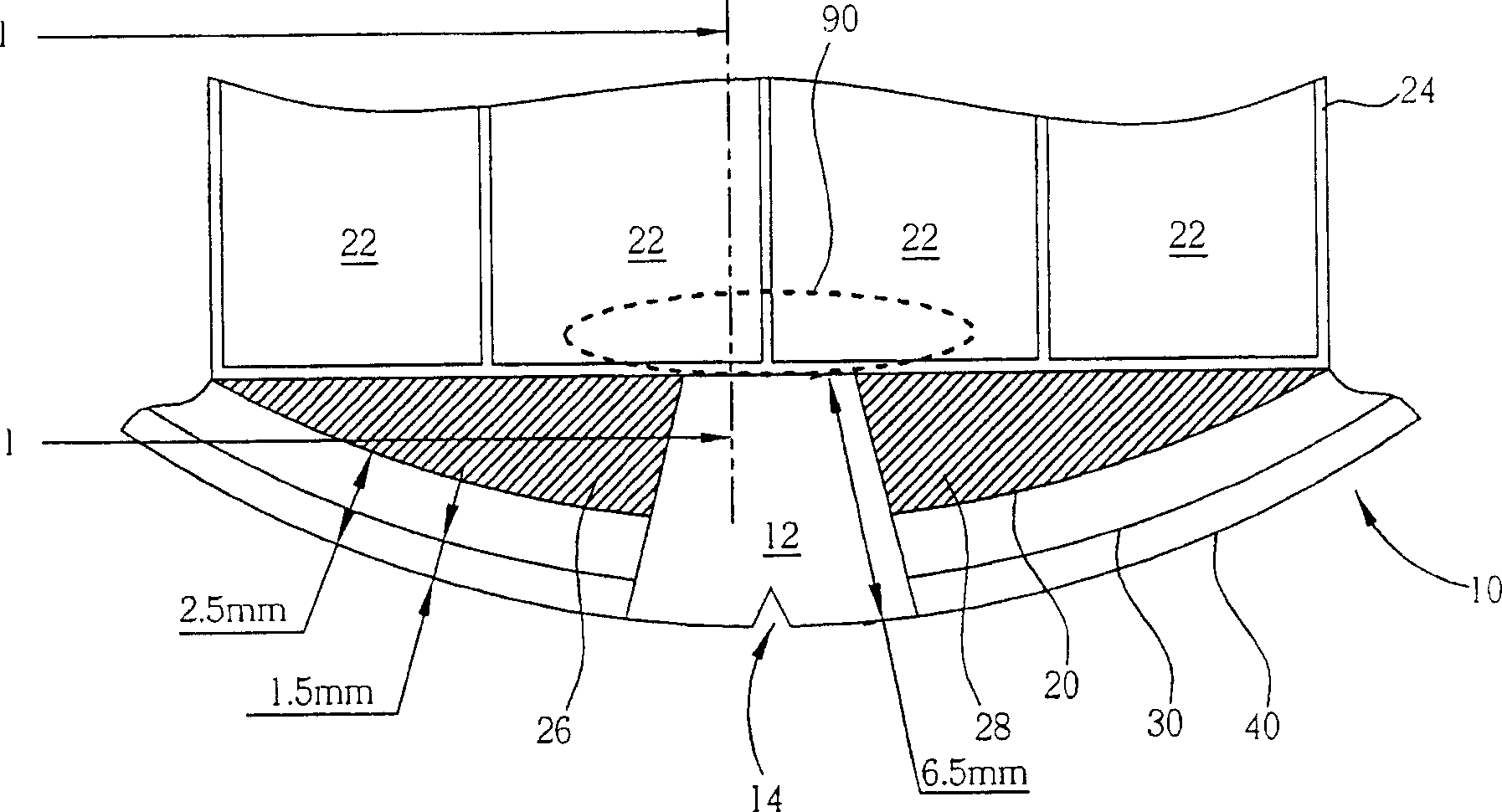

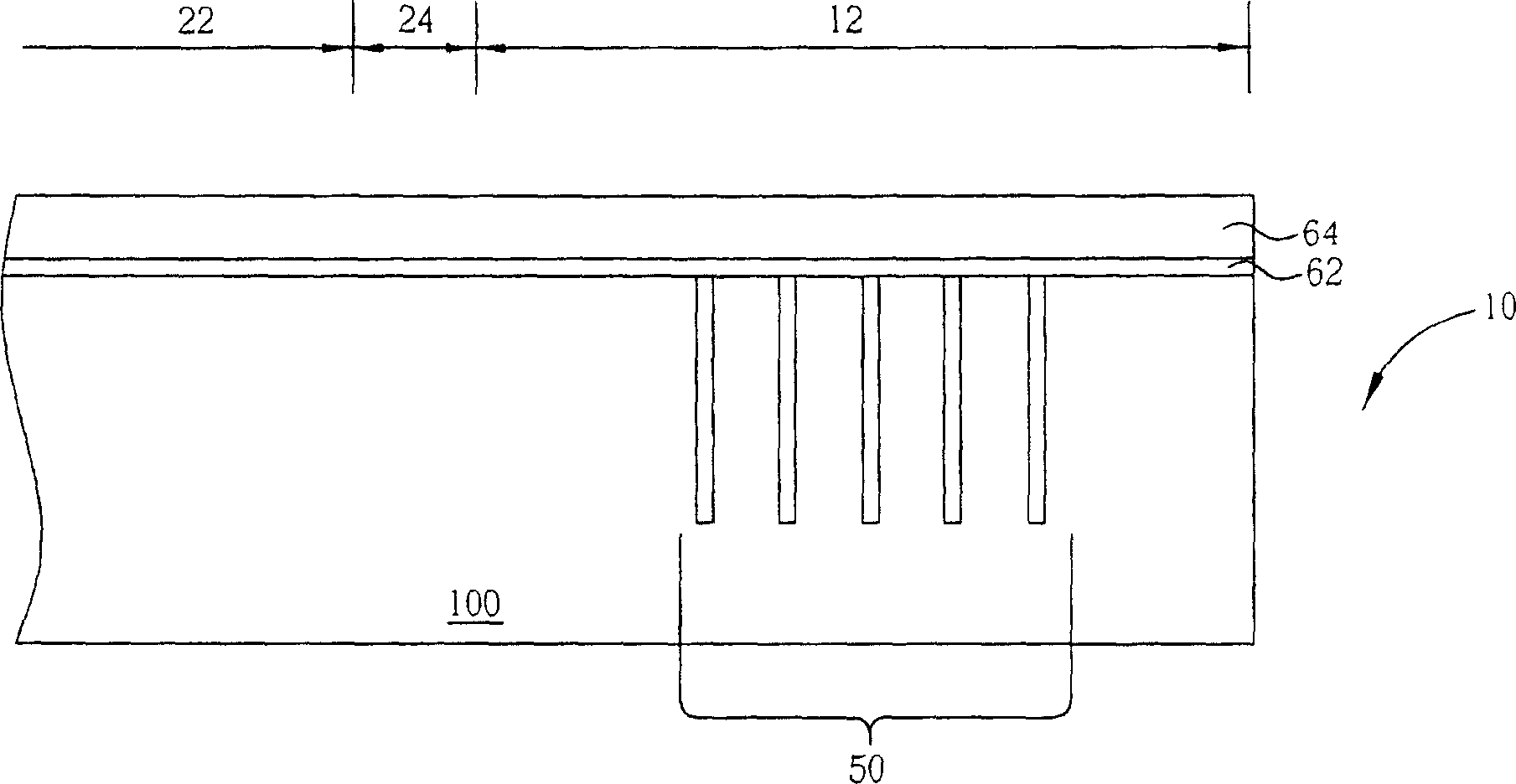

[0035] see Figure 8 , which shows the top view near the laser marking area 12 of the wafer 10 according to the preferred embodiment of the present invention, which includes the integrated circuit wafer area 22, the wafer edge exposure area (waferedge exposure, WEE) and the wafer edge cleaning area ( edge bead removal, EBR). Such as Figure 8 As shown, the wafer 10 has a V-shaped notch 14 , and the laser marking area 12 is generally located near the V-shaped notch 14 and is provided on the front side of the wafer 10 . In the laser marking area 12 , there is provided a laser marking 50 of the wafer including the batch number of the wafer and the identification number of the wafer. The laser marking area 12 is adjacent to the scribe line 24 surrounding the IC die area 22 , and the interface between the laser marking area 12 and the scribe line 24 is usually about 6.5 mm away from the edge 40 of the wafer. The purpose of the laser marking area 12 being disposed on the edge of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com