Strain source-drain CMOS integrating method with oxide separation layer

An integrated method and oxide technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as erosion of spacers and shallow trench isolation regions, and achieve wide process tolerance, safe removal, and easy process. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

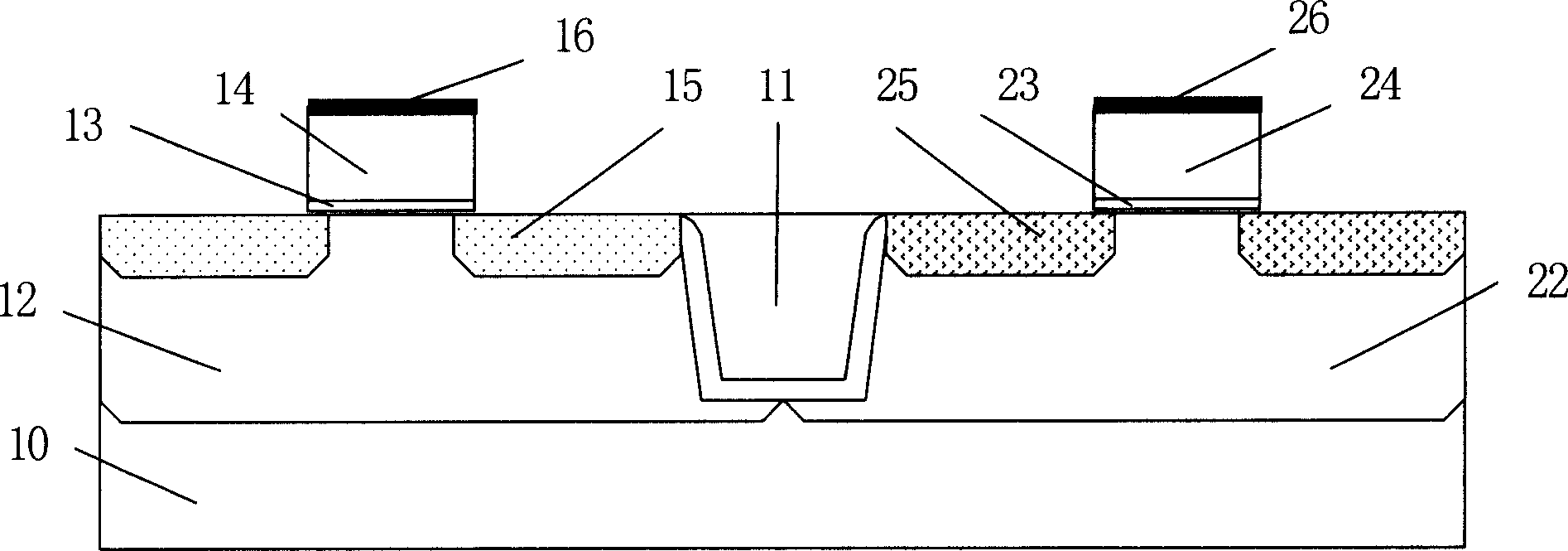

Embodiment 1

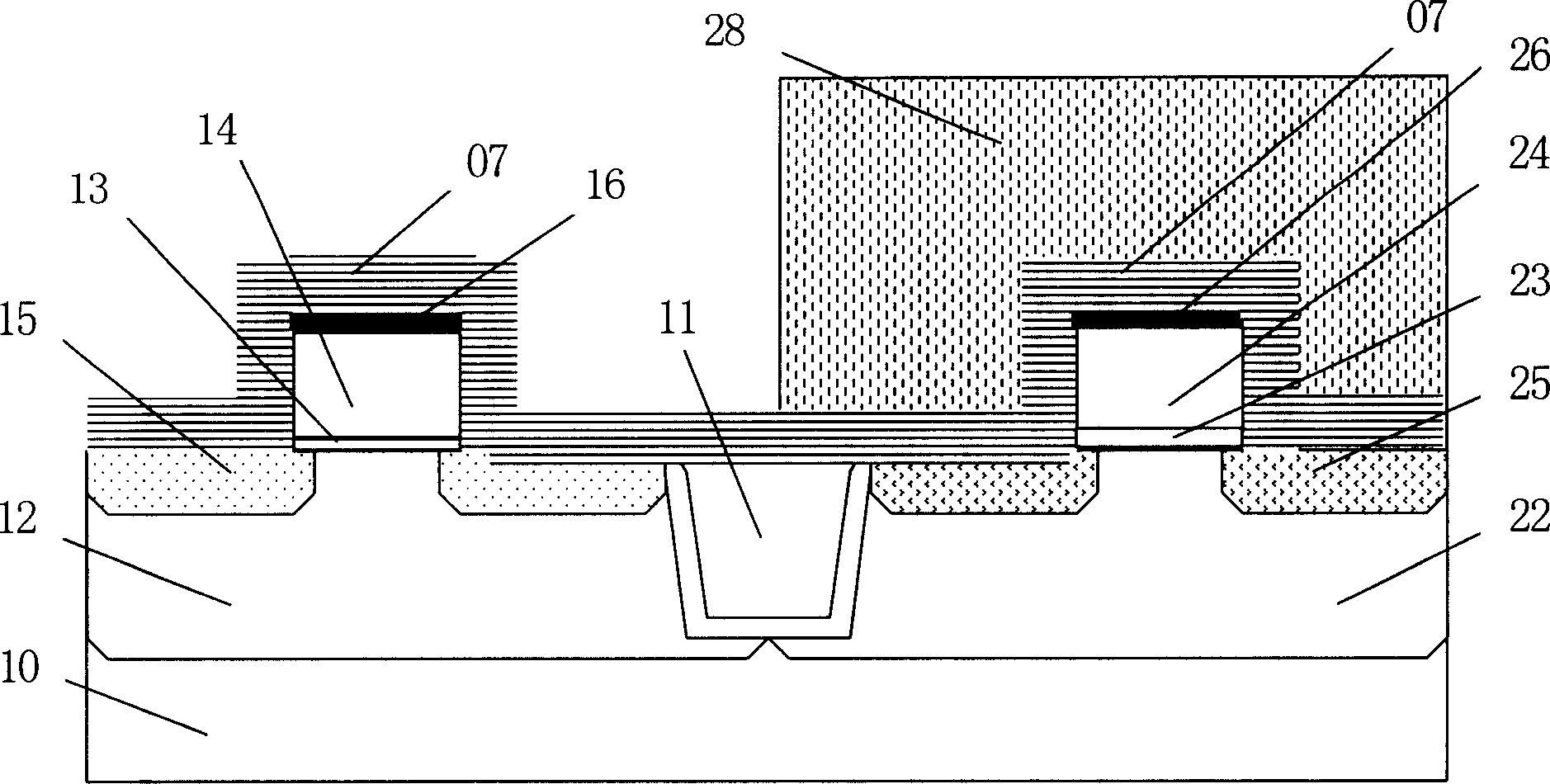

[0066] Such as Figure 3a As shown, the NMOS region is protected with a photoresist 28, and the photolithographic patterning exposes the PMOS region. Such as Figure 3b As shown, the spacer layer 17 of the PMOS region is then etched to form the spacer layer 17 of the PMOS region, and the NMOS region is protected.

[0067] Such as Figure 4 As shown, the photoresist 28 in the NMOS area is removed and cleaned, and the PMOS polysilicon hard mask 16 and the spacer layer 17 are used as a photolithography pattern mask to conduct self-aligned silicon substrate recess etching in the PMOS area. A silicon germanium layer 155 is epitaxially grown on the recessed silicon. Its germanium concentration is 5-45%. Then chemical vapor deposition of nitride 09 with a thickness of 50-500 Å is carried out in the PMOS region and the NMOS region. As shown in Table 2, since silicon has a higher etching rate than silicon nitride, its etching rate ratio is 4-5.4, so it is easy to realize and contr...

Embodiment 2

[0074] The above PMOS and NMOS epitaxial growth sequences can be interchanged, and the method is the same as before, that is, the NMOS silicon carbon is first formed before the silicon germanium is formed.

[0075] The PMOS area is protected with photoresist, and the NMOS area is exposed by photolithography patterning. Then, the spacer layer of the NMOS region is etched to form the spacer layer of the NMOS, and the PMOS region is protected.

[0076] The photoresist is removed and cleaned, and the polysilicon hard mask and the spacer layer are used as the mask of the photolithographic pattern, and the self-aligned silicon substrate is recessed and etched in the NMOS region. Silicon carbon is grown on the recessed silicon. Its carbon concentration is 0.5-10%. Silicon nitride with a thickness of 50-500A is chemically vapor deposited in the PMOS and NMOS regions.

[0077] The NMOS area is covered with photoresist, and a photoresist pattern is formed on the exposed PMOS area. U...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com