Error decoding circuit, data bus control method and data bus system

A decoding circuit and data bus technology, applied in the field of data processing, can solve the problems of long processing time and large error correction circuit scale, and achieve the effects of high-speed processing, high-speed data bus cycle, and simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

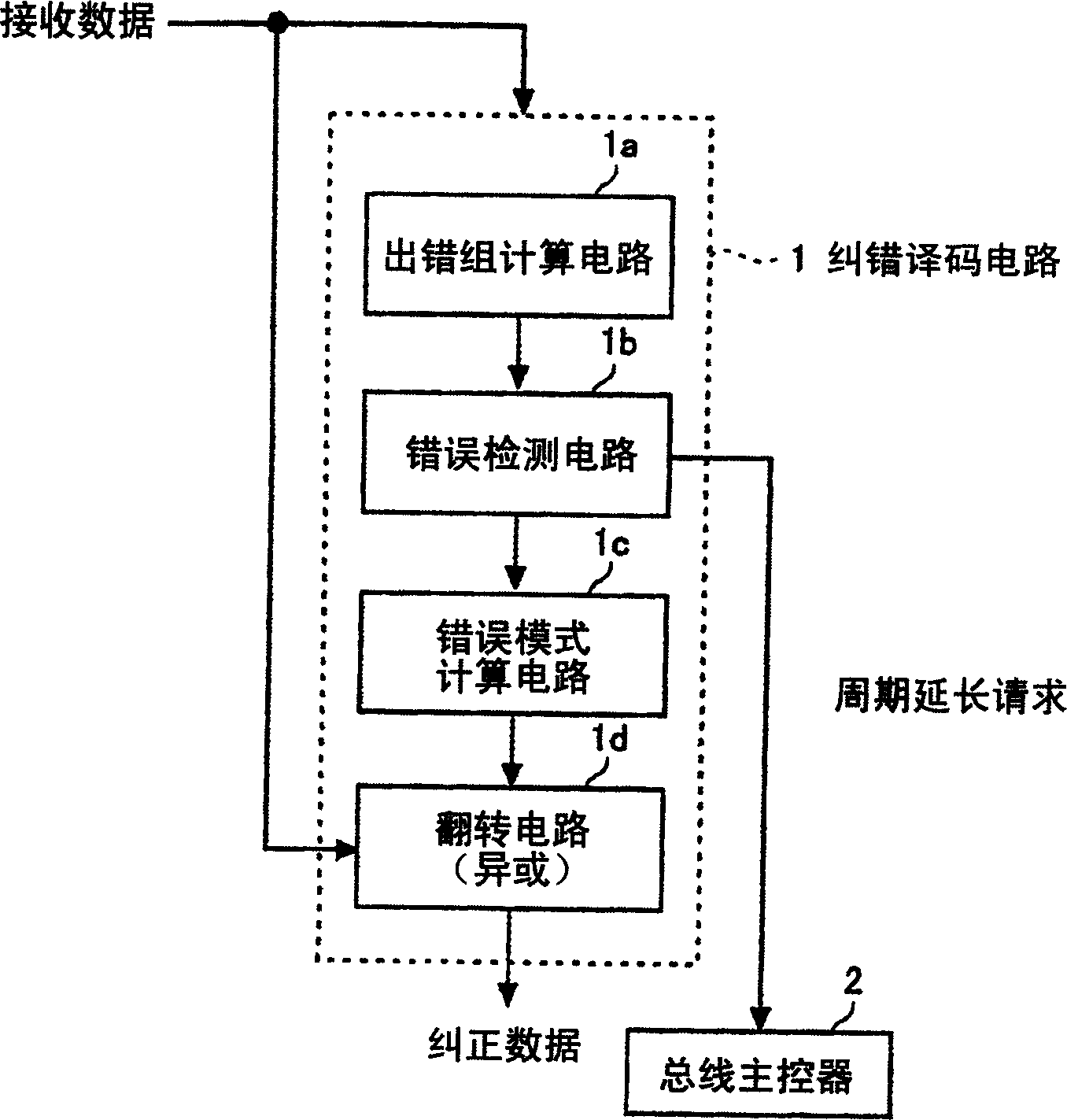

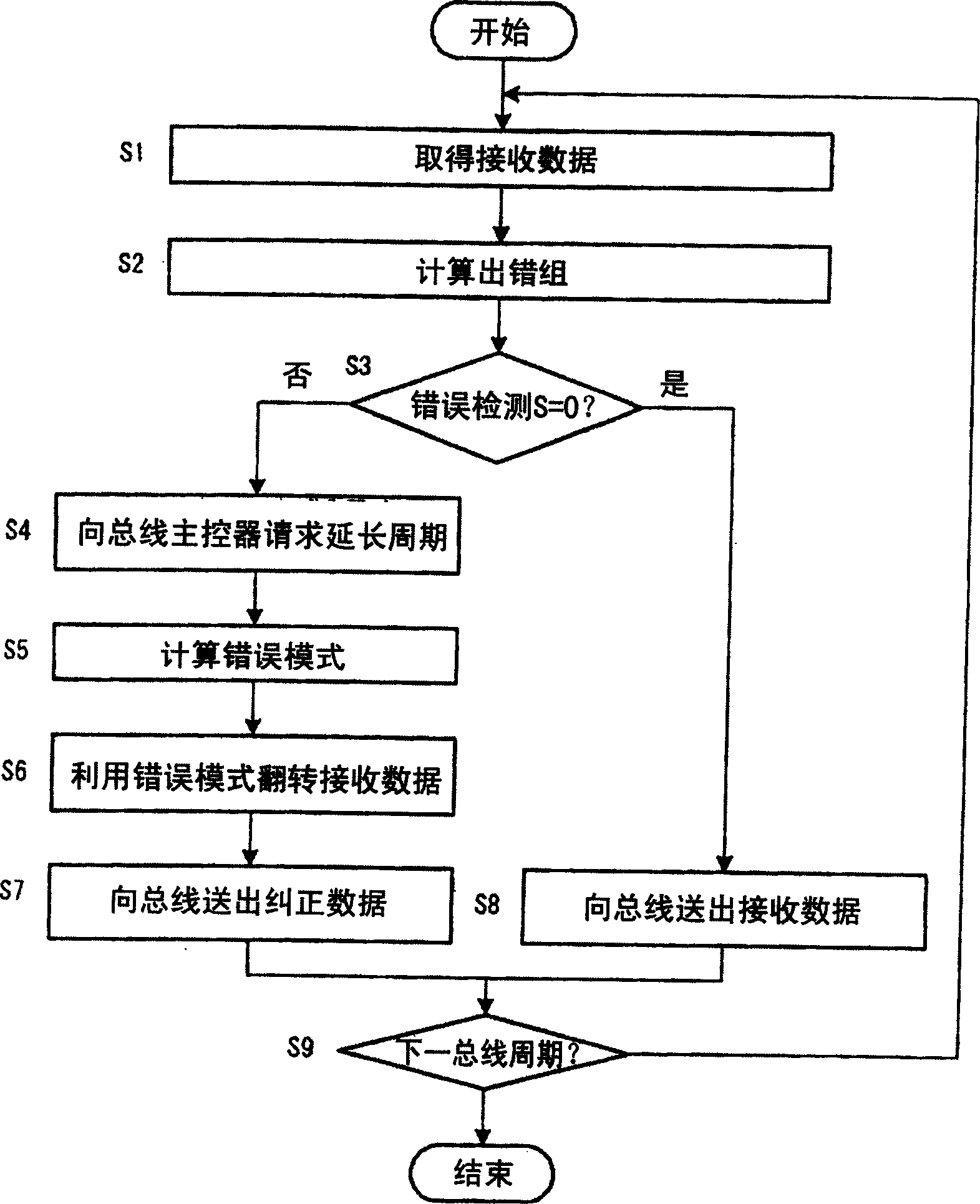

[0053] figure 1 It is a figure for explaining the outline|summary of the error correction decoding circuit of this invention. figure 1 The shown error correction decoding circuit 1 has an error group calculation circuit 1a that inputs received data and calculates the error group, an error detection circuit 1b that detects an error based on the calculated error group, and calculates an error pattern based on the error group when an error is detected. An error pattern calculation circuit 1c, and an inversion circuit 1d for error-correcting received data based on the calculated error pattern.

[0054] The error detection circuit 1b outputs a bus cycle extension request signal to the bus master 2 when it determines that there is an error in the received data based on the detection result.

[0055] In addition, received data is data received via a transmission path by adding a check bit to input data using an encoding circuit not shown. The transmission path is not limited to a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com