Single electron trivalue storage based on coulomb baffle principle design and its preparation method

A principle design, Coulomb blocking technology, applied in the direction of electric solid devices, circuits, electrical components, etc., to achieve the effect of high storage density, enhanced storage time, and simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

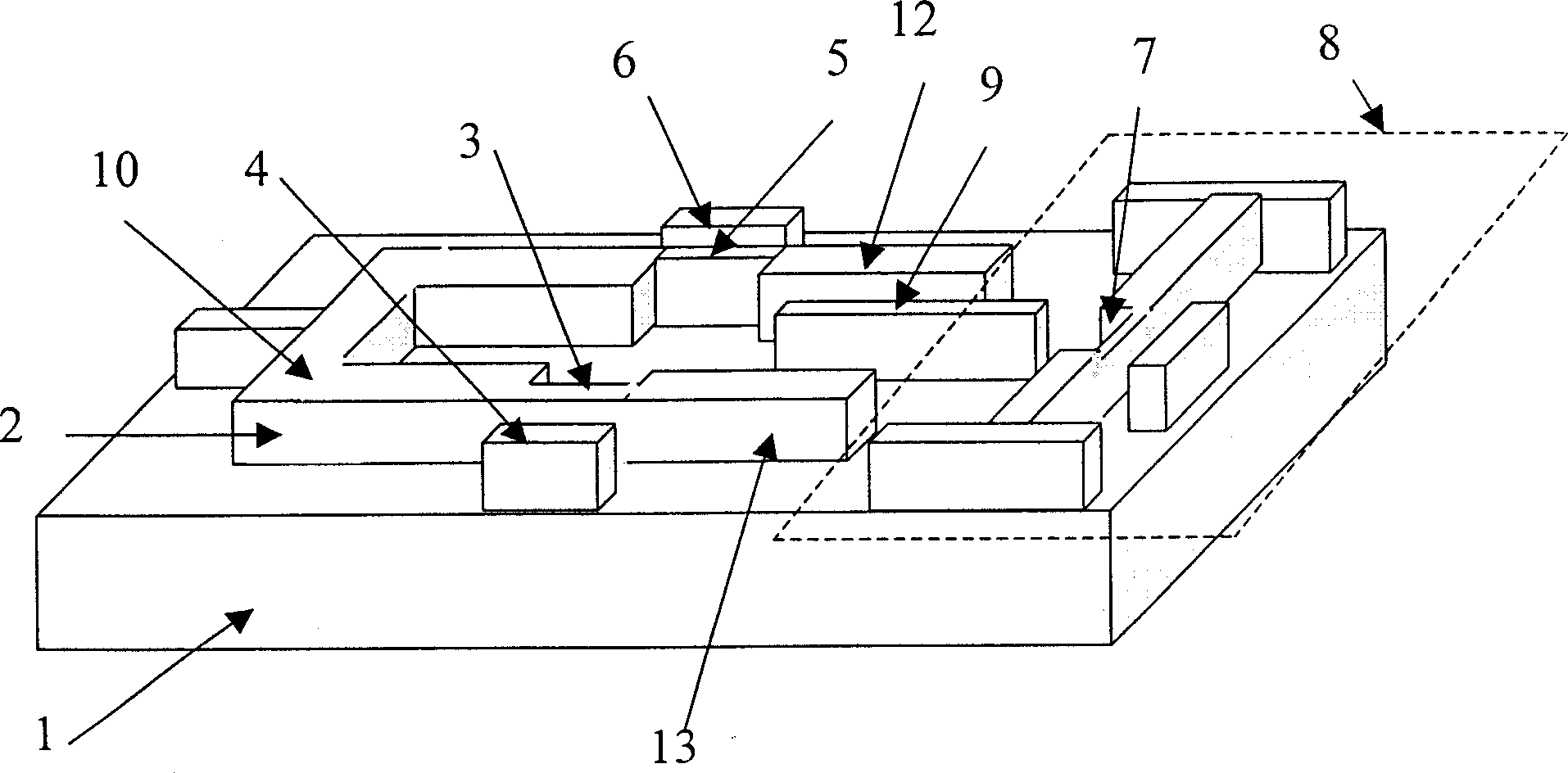

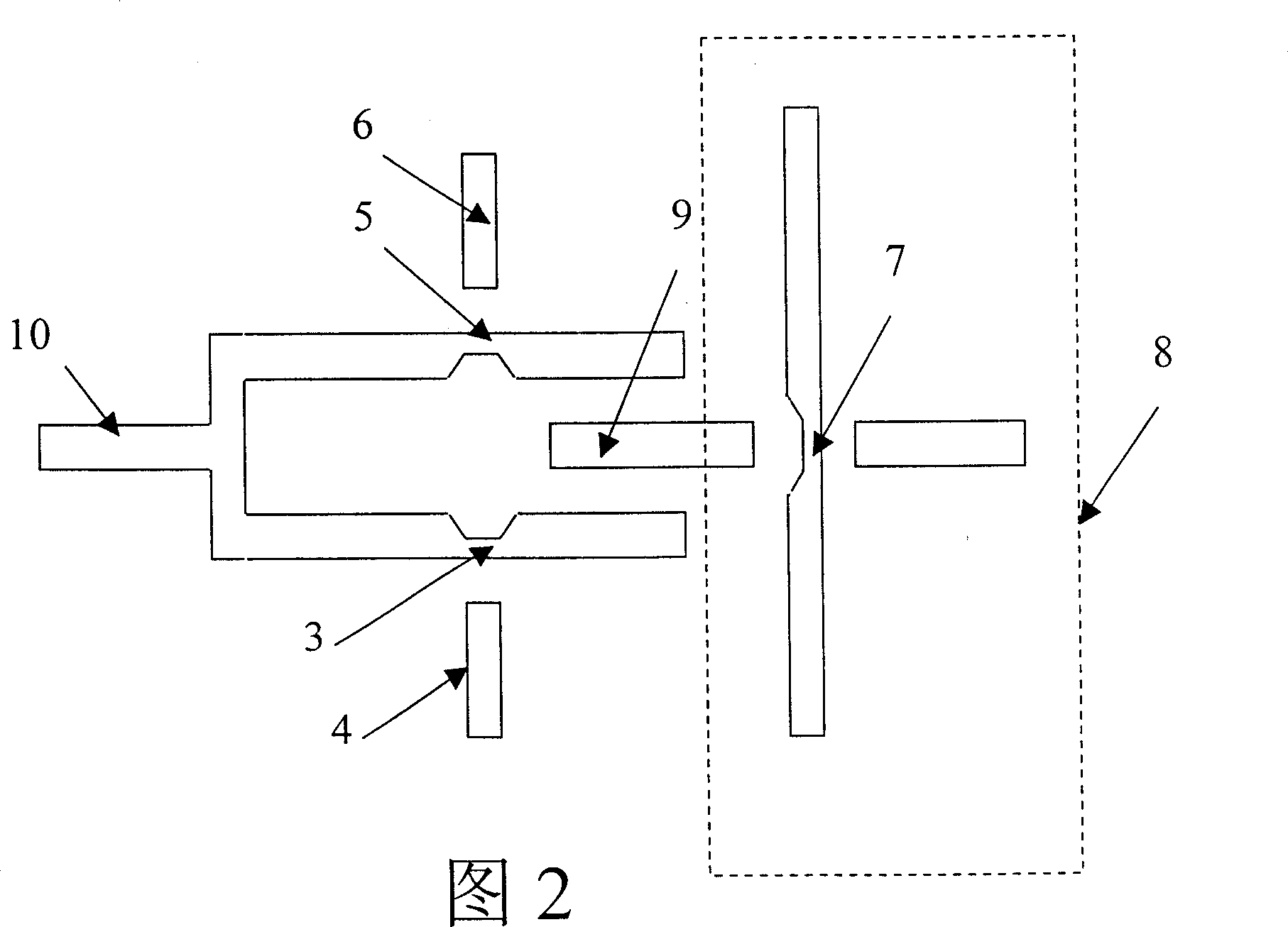

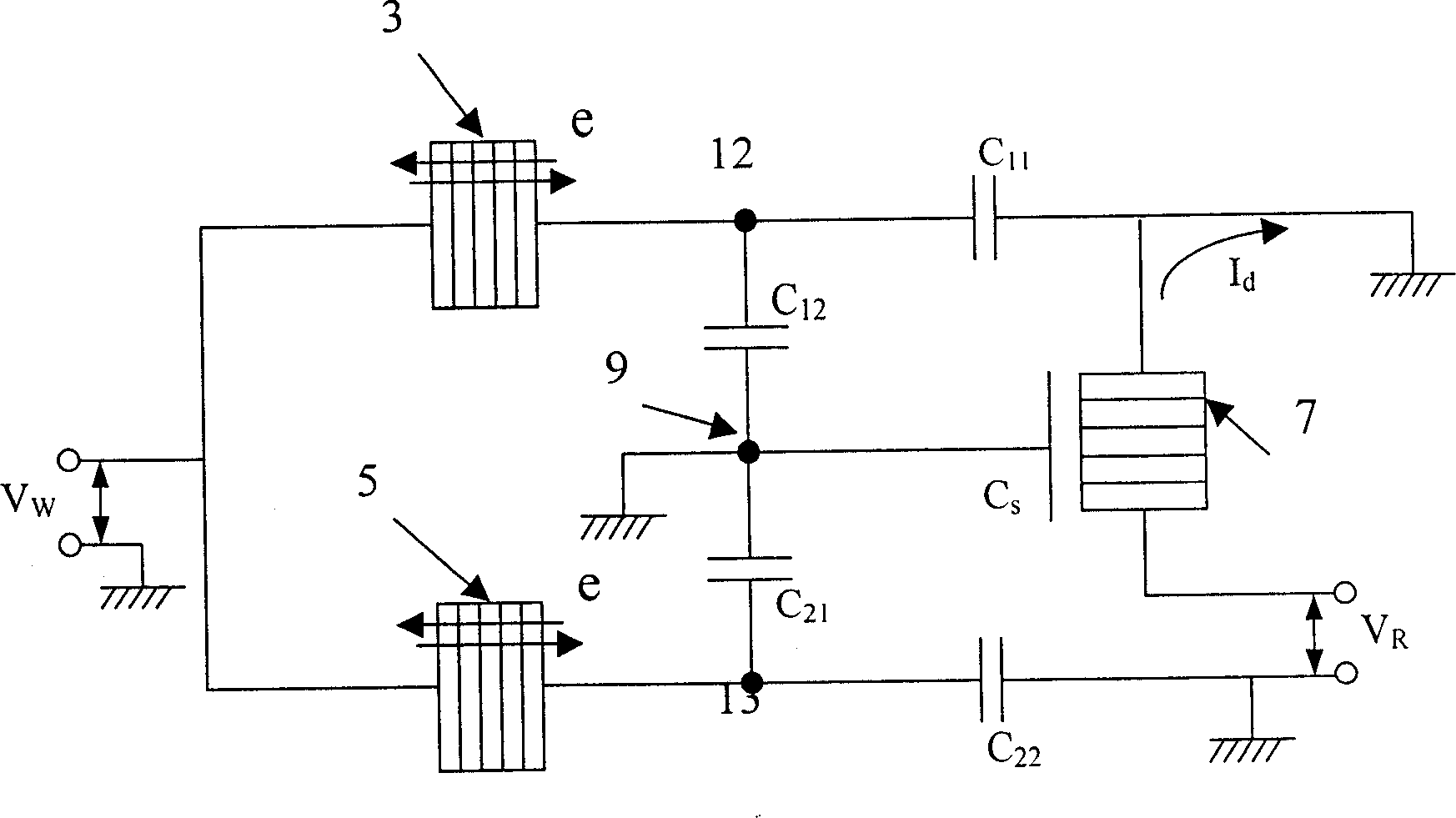

[0036] according to figure 1 and 2 make a single-electron ternary memory designed based on the Coulomb blocking principle of the present invention, and the present invention will be described in detail below in conjunction with embodiments and manufacturing methods:

[0037] A half-insulating GaAs sheet is selected, and a 1-micron-thick GaAs buffer layer is grown on it by molecular beam epitaxy (MBE) to form an insulating substrate 1 . A silicon delta-doped GaAs layer is formed on the buffer layer by molecular beam epitaxy, and the layer is deposited on the GaAs buffer layer with an area density of 1×10 12 cm -2 Silicon and a 50nm-thick GaAs layer grown on it, which constitutes the conductive material layer 2 of the device.

[0038] Then, the following structures (such as figure 1Shown): the first side gate 4, the second side gate 6, the gate length is 200 nanometers, the length of the two depleted nanowires is 200 nanometers, the width is 100 nanometers, and the distance b...

Embodiment 2

[0040] Silicon with (001) orientation is selected, and a 60 nm thick silicon dioxide insulating layer is oxidized by dry oxygen oxidation method at an oxidation temperature of 900° C., which forms the substrate 1 . A 40nm-thick polysilicon layer is formed on the oxide layer by molecular beam epitaxy MBE or chemical vapor deposition, and heavily doped with arsenic to become an n-type semiconductor layer with an implantation dose of 6×10 13 cm -2 , so that the highly doped silicon layer forms the conductive material layer 2 .

[0041] The preparation of other parts of the device is the same as in Example 1.

Embodiment 3

[0043] Silicon on insulator (SOI) is selected, which is prepared by oxygen injection isolation process, and the top layer silicon is thinned by dry oxygen oxidation. The parameters are as follows: material crystal orientation , P type, resistivity 3Ωcm; thickness of top layer silicon is 40 nm, and the thickness of the buried silicon dioxide is 200 nm. The n-type conductive layer is formed by implanting impurity arsenic into the thinned top silicon, and the implantation dose is 5×10 13 cm -2 . The doped top layer silicon is thinned to form the conductive material layer 2 .

[0044] The preparation of other parts of the device is the same as in Example 1.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com