Method for testing security performance of SRAM (Static Random Access Memory) chip

A technology of safety performance and testing method, applied in the field of testing, can solve the problems of inability to accurately measure the degree of aging, single evaluation variable, etc., to ensure the reliability of data, simplify the calculation process, and save computing resources.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

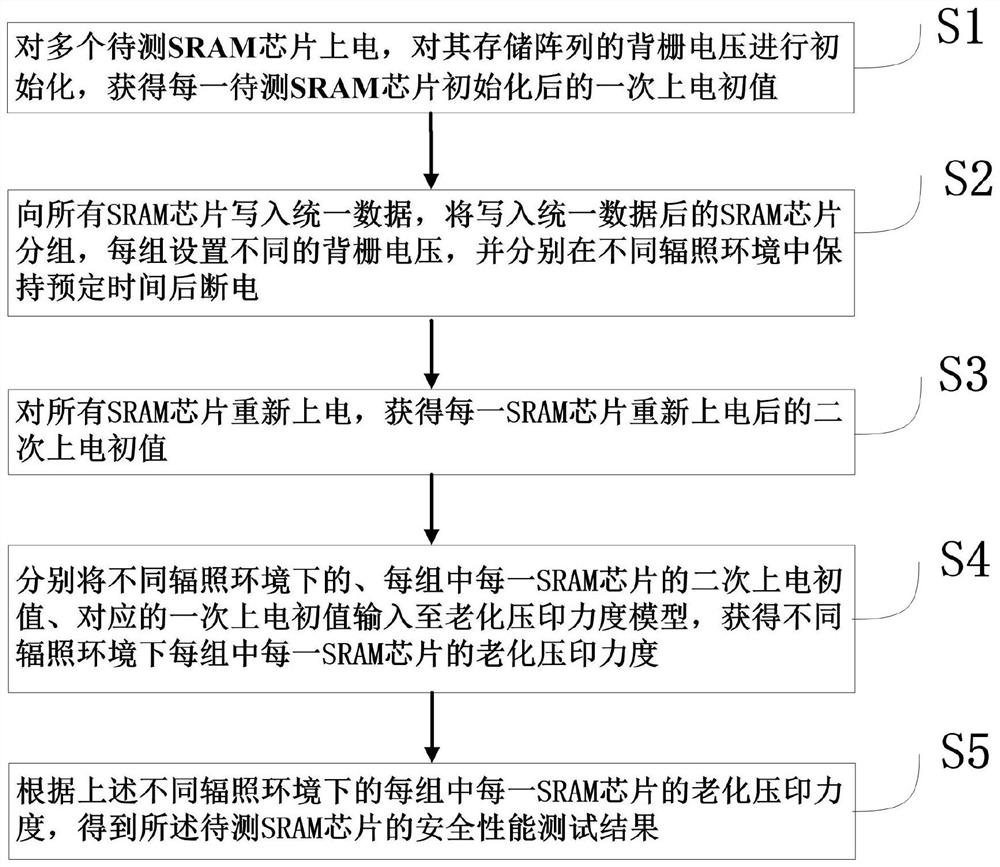

[0058] A specific embodiment of the present invention discloses a method for testing the safety performance of an SRAM chip, such as figure 1 shown, including the following steps:

[0059] S1. Power on multiple SRAM chips to be tested, initialize the back gate voltage of their storage arrays, and obtain an initial power-on value after initialization of each SRAM chip to be tested through statistics;

[0060] S2. Write unified data to all SRAM chips, group the SRAM chips after writing the unified data, set different back gate voltages for each group, and keep the power off after a predetermined period of time in different irradiation environments;

[0061] S3. Re-power on all SRAM chips, and obtain the initial value of the second power-on after re-powering each SRAM chip through statistics;

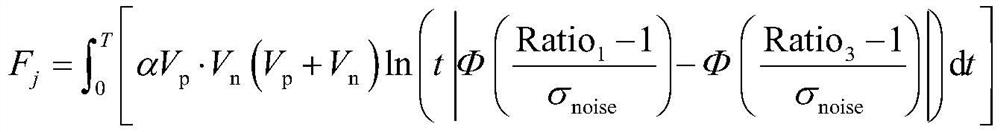

[0062] S4. Respectively input the secondary power-on initial value and the corresponding primary power-on initial value of each SRAM chip in each group under different irradiation environ...

Embodiment 2

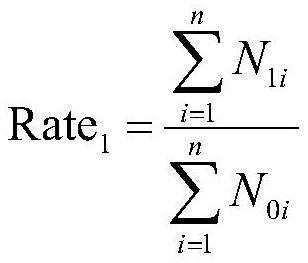

[0067] On the basis of Embodiment 1, optimization is performed, and the initial value of power-on is represented by the ratio of the number of memory cells with a value of 1 to the number of memory cells with a value of 0 in the SRAM chip after power-on.

[0068] Step S1 further includes:

[0069] S11. Connect each SRAM chip to be tested to the test system, and power on the SRAM chip through the test system;

[0070] S12. Set the back gate voltage V of all NMOS transistors and PMOS transistors in the memory array of the SRAM chip BN with V BP All are set to 0V, the initialization is completed, and the number and proportion of 1 and 0 in the storage array after initialization are counted;

[0071] S13. Repeat the process of the above steps S11 to S12 to complete n tests, and sequentially obtain the number and ratio of 1 and 0 in the storage array after the SRAM chip is initialized in the n test results, and for all the number N of 1 and 0 1i , N 0i Calculate the average wit...

Embodiment 3

[0094] The present invention also provides an evaluation system for the safety performance of the SRAM chip corresponding to Embodiment 1 or 2, including a test board, an FPGA chip and a host computer connected in sequence. Wireless communication is possible between the FPGA chip and the host computer.

[0095] The test board is used to access the SRAM chip to be tested, and to adjust the back gate voltages of all NMOS transistors and PMOS transistors in its storage array according to the control of the FPGA chip; and, to output the information stored in the storage array of the SRAM chip to be tested to FPGA chip.

[0096] Through the above test board, each port of the SRAM chip to be tested is led out.

[0097]The FPGA chip is used to send an initialization instruction to the test board during testing, and the initialization instruction is used to set the back gate voltages of all NMOS transistors and PMOS transistors in the storage array of the SRAM chip to be tested to 0V...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com