Automatic temperature control power chip structure and preparation method thereof

A power chip and temperature control technology, applied in the fields of semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems of affecting thermal fatigue life, reducing the reliability of high-power devices, and hindering the heat dissipation performance of high-power devices, etc. Achieve precise control of temperature uniformity, enhanced direct heat dissipation and heat dissipation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0058] Corresponding to a kind of automatic temperature control power chip structure, the present invention provides a kind of automatic temperature control power chip preparation method, such as Figure 8 Shown, preparation method comprises:

[0059] Step S1, preparing the N-P-N layer of the IGBT;

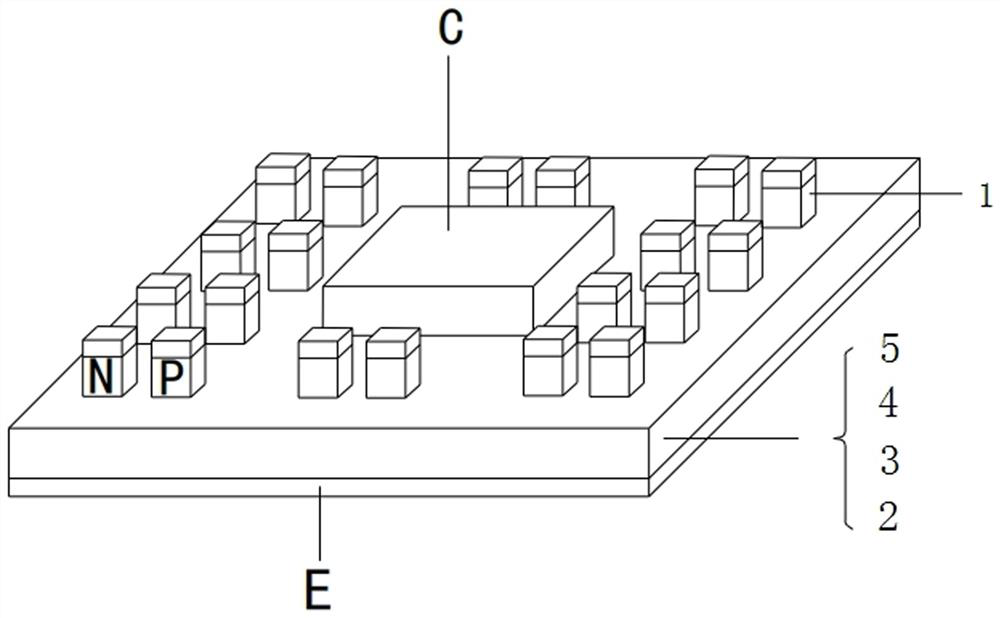

[0060] Step S2, using the N region of the N-P-N layer as the substrate to perform epitaxial growth to form a plurality of N-type epitaxial layers;

[0061] Step S3, etching the plurality of N-type epitaxial layers through a metal mask to form an arrayed columnar structure;

[0062] Step S4, directionally injecting P-type impurity ions into each columnar structure in the arrayed columnar structure to form an arrayed P-N thermocouple structure 1;

[0063] Step S5, performing metallization on the arrayed P-N thermocouple structure 1 and the P+ drain injection region 5 in the N-P-N layer by evaporation or sputtering to form the metal layer of the IGBT.

Embodiment 1

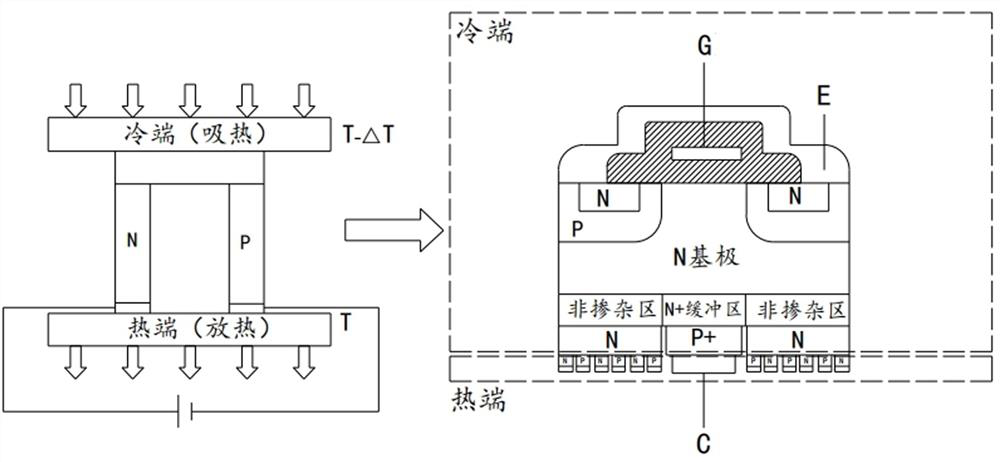

[0065] The IGBT is an asymmetric IGBT (also known as a punch-through IGBT) with an N+ buffer zone 4 . Asymmetric IGBT has the advantages of small forward voltage drop, short turn-off time, and small tail current when turned off, but its reverse blocking ability is relatively weak.

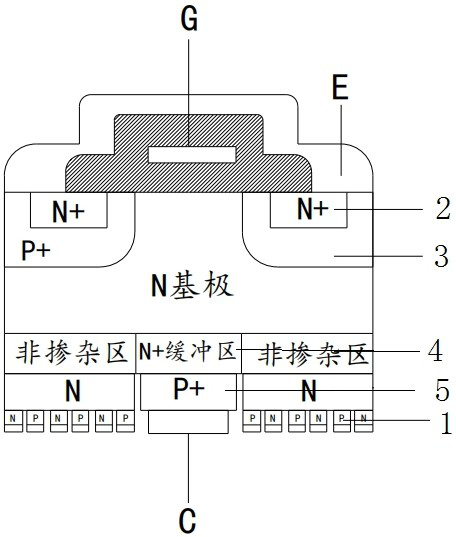

[0066] refer to Figure 4 , Insulated gate bipolar transistor includes: gate, emitter, collector, gate region arranged in sequence from emitter to collector, N+ source region 2, P-type region 3, N base, N+ buffer zone 4 and P+ Drain into region 5. A gate is attached to the gate region. One side of the multiple N-type epitaxial layers is connected to the N+ buffer zone 4 , and the other side of the multiple N-type epitaxial layers is provided with an arrayed P-N thermocouple structure 1 .

[0067] Among them, the N+ region attached to the emitter (E) is the source region, the P+ region is the P-type region 3, the N+ region attached to the P+ region is the N buffer zone, the control region of the ...

Embodiment 2

[0080] The IGBT is a symmetrical IGBT (also known as a non-punch-through IGBT), without an N+ buffer zone 4. Non-punch-through IGBT means that the electric field does not penetrate the N-drift region. The basic technical principle of NPT (Non-PunchThrough, non-punch-through) is to cancel the N+ buffer zone and directly inject space charge into the collector region to form a high-resistance region. The main confluence of the holes is replaced by a P+ collector. The symmetrical IGBT has strong forward and reverse blocking ability, and its other characteristics are worse than those of the punch-through IGBT.

[0081] refer to Figure 5 , The insulated gate bipolar transistor includes: a gate, an emitter, a collector, a gate region arranged sequentially from the emitter to the collector, an N+ source region 2 , a P-type region 3 , an N base and a P+ drain injection region 5 . A gate is attached to the gate region. One side of the multiple N-type epitaxial layers is connected to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com