Layout-based high fan-out line network optimization method and optimization system for FPGA integrated circuit

A technology of integrated circuits and optimization methods, which is applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of not being able to adapt to the high integration of integrated circuits and quickly process signals, not considering the impact of timing, and single division methods , to achieve the effect of improving splitting efficiency, simplifying wiring difficulty, and accurate and fast algorithm

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0061] The present invention is described below based on examples, but the present invention is not limited to these examples. In the following detailed description of the invention, some specific details are set forth in detail. The present invention can be fully understood by those skilled in the art without the description of these detailed parts. In order to avoid obscuring the essence of the present invention, well-known methods, procedures, and flow charts are not described in detail. Additionally, the drawings are not necessarily drawn to scale.

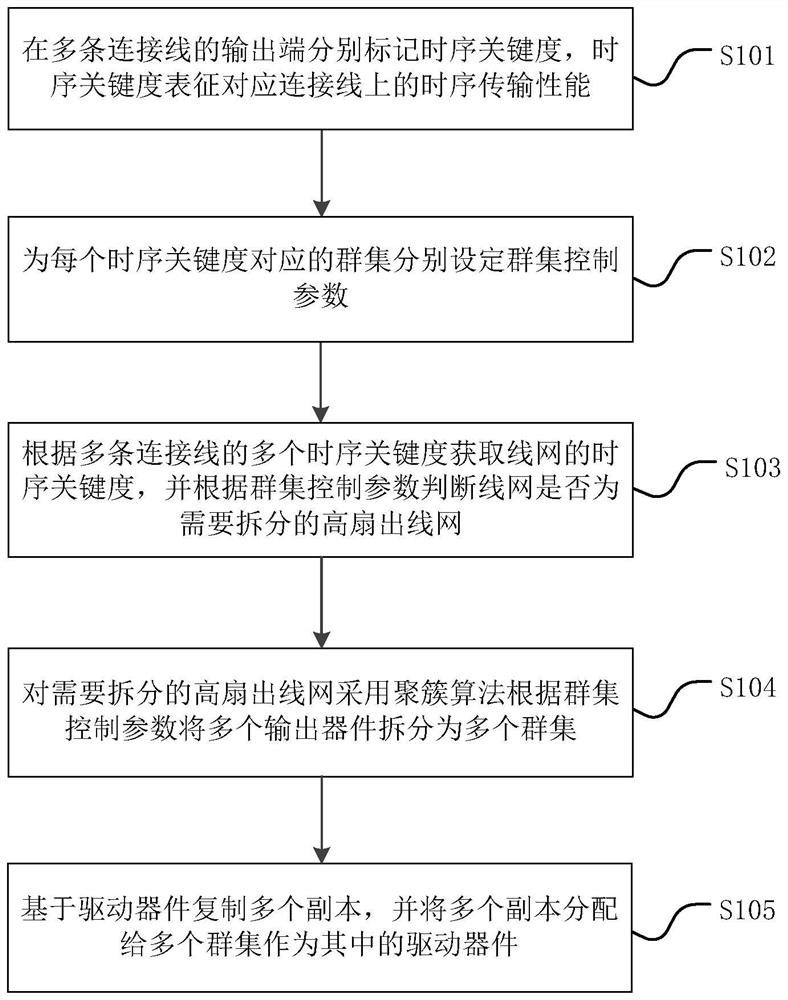

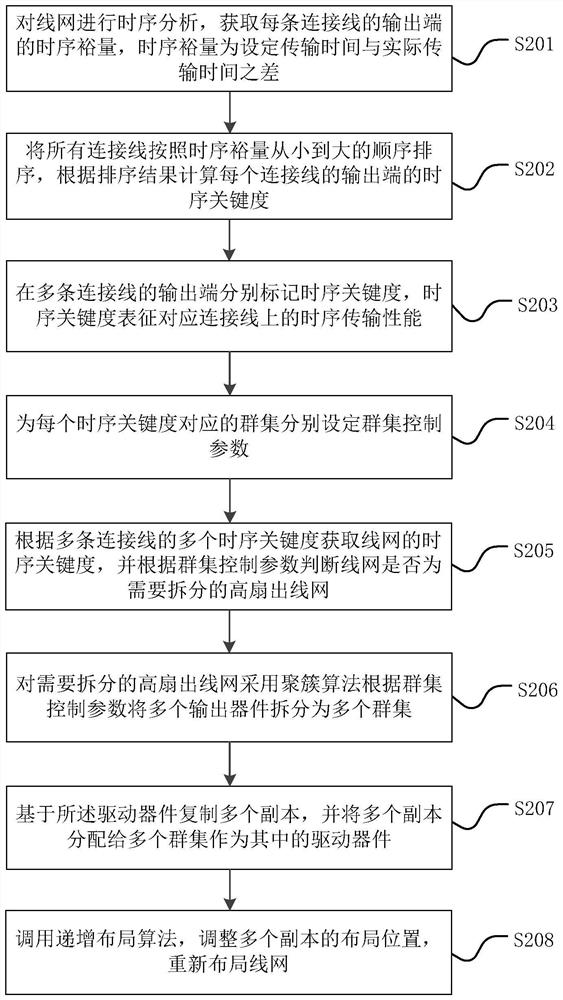

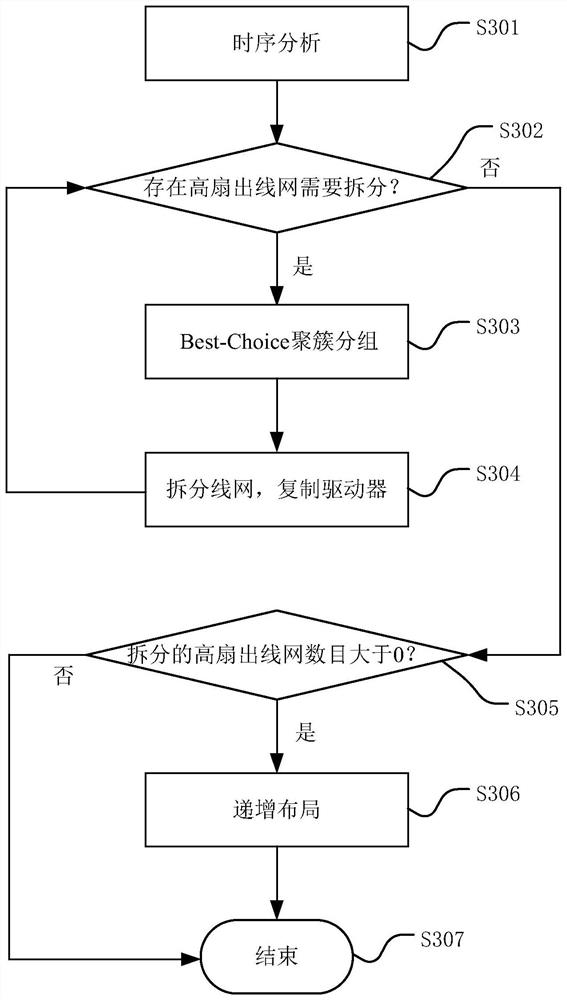

[0062] figure 1 A simplified flow chart of a layout-based high fan-out net optimization method for an FPGA integrated circuit according to an embodiment of the present invention is shown, and the specific steps include S101-S105.

[0063] When routing integrated circuits, some optimization methods for high fanout nets are usually used to reduce the load on high fanout nets. For example, the K-Center clustering algorithm is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com