Soc PMUT, array chip and manufacturing method suitable for high-density system integration

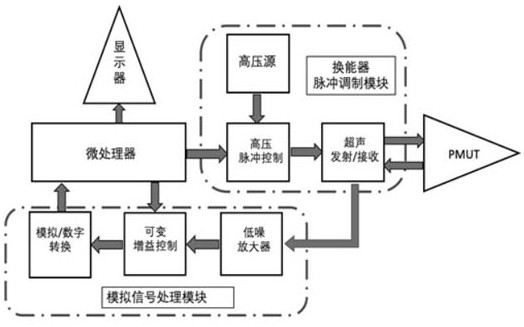

A technology of system integration and manufacturing method, which is applied to components of TV systems, manufacturing microstructure devices, fluid velocity measurement, etc., can solve the problem of reducing PMUT unit duty cycle, affecting PMUT array uniformity, operating frequency, and poor power consumption Influence and other problems, to achieve the effect of reducing chip size and system volume, realizing one-machine multi-frequency scanning, and high-density system integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

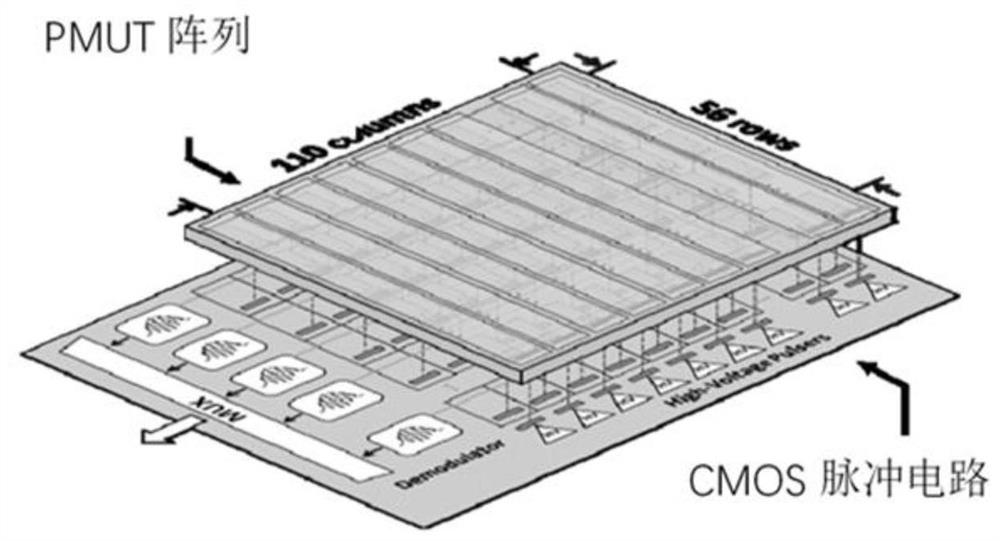

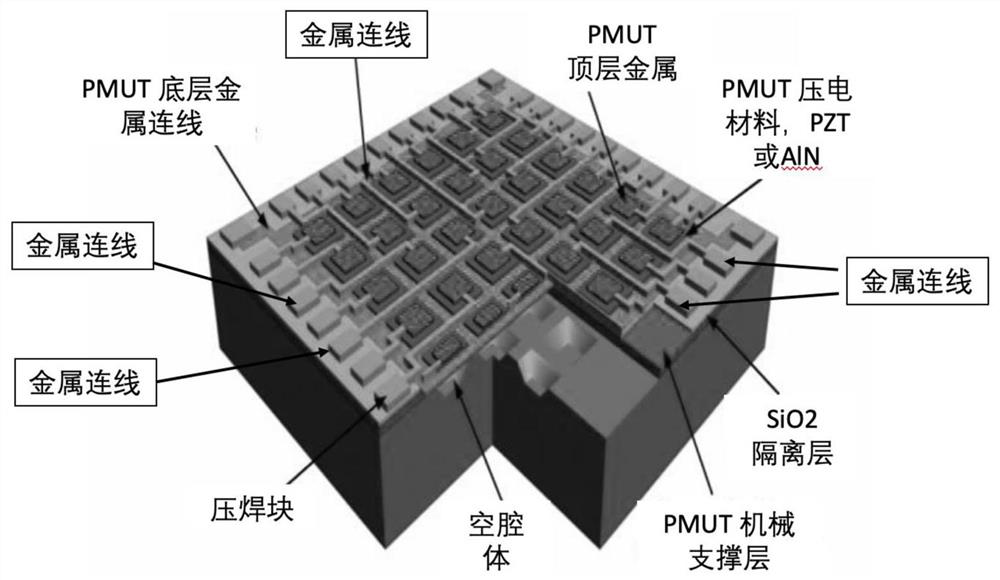

[0091] As shown in Fig. 4 (a), 4 (b), present embodiment provides a kind of SOC PMUT suitable for high-density system integration, comprises first wafer and second wafer, and first wafer arranges silicon substrate material 160 , CMOS unit 160-CMOS with double-layer metal wiring, the second wafer arranges the mechanical layer 130, the lower metal layer 112, the piezoelectric material layer 115, the upper metal layer 114, the cavity body 120, and the CMOS auxiliary circuit of the double-layer metal wiring 300-CMOS.

[0092] The two ends of the metal interconnection layer 201 of the CMOS unit 160 -CMOS disposed above the silicon substrate 160 are vertically interconnected with two second-layer metal wirings 202 above the metal interconnection layer 201 through two metal lead holes 212 respectively. The silicon substrate 160 is provided with two silicon through-hole TSVs 162 that run through the entire silicon substrate 160, so that the two ends of the metal interconnection layer ...

Embodiment 2

[0103] This embodiment provides a SOC ultrasonic transducer suitable for high-density system integration, which is similar to the structure of Embodiment 1. Considering the overall design of the SOC PMUT, when the resolution requirement is high and a large-scale array is required, the interconnection Implementations may require multiple layers of wiring. For example, when artificial intelligence algorithms are also put into SOC PMUT ultrasonic design, CMOS IC design may require 5-6 layers of metal wiring. In the process flow of the present invention, the wiring structure has been specially considered, and the process flow has great flexibility in the number of wiring layers. Therefore, in this embodiment, on the basis of the first embodiment, at least one layer of metal wiring is provided above the second layer of metal wiring, and the metal wiring of each layer of the at least one layer of metal wiring is vertically interconnected through metal lead holes. , the lowermost la...

Embodiment 3

[0106] This embodiment provides a vertical electrical interconnection to replace the traditional planar wiring method to manufacture the ultrasonic transducer suitable for high-density system integration. The SOC PMUT ultrasonic transducer vertically connects the PMUT upper metal layer 114 to the stop layer metal structure 303 and the corresponding CMOS auxiliary circuit 300-CMOS second layer metal 302 respectively through the upper metal connection hole ZTM163-1; The lower metal layer 112 is vertically connected to the stop layer metal structure 303 and the corresponding CMOS auxiliary circuit 300-CMOS second layer metal 302 through the lower metal connection hole ZBM 163-2, and then through the two metal The lead hole 312 is vertically connected to any device in the CMOS auxiliary circuit 300-CMOS. Through reasonable wiring, series and parallel connection of multiple ultrasonic transducers can be realized.

[0107] The CMOS auxiliary circuit 300-CMOS can be connected to the...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com