Power transistor structure and manufacturing method thereof

A power transistor and trench technology, which is applied in the field of power transistor structure and its manufacturing, can solve the problems of poor connection ability, poor contact and delamination of the inner dielectric layer, and achieves that it is not easy to break, ensures the connection performance, and has a good connection effect. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

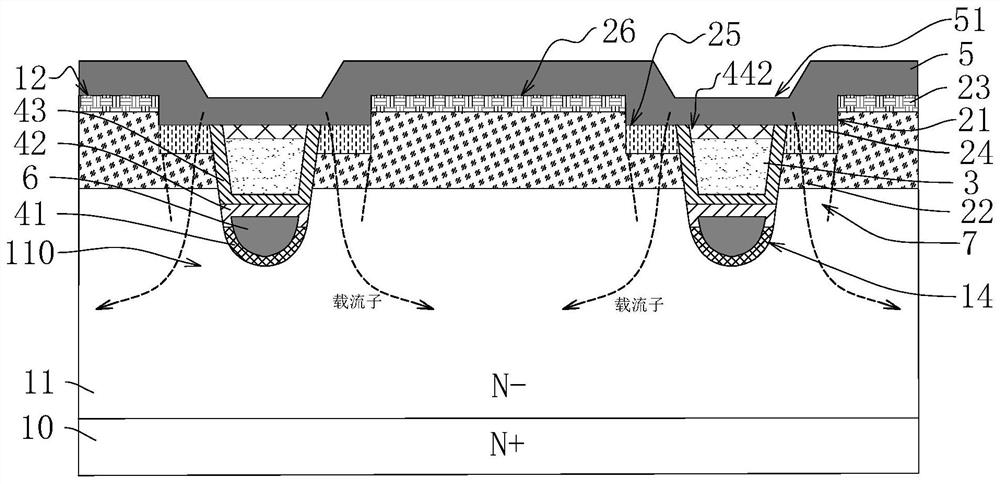

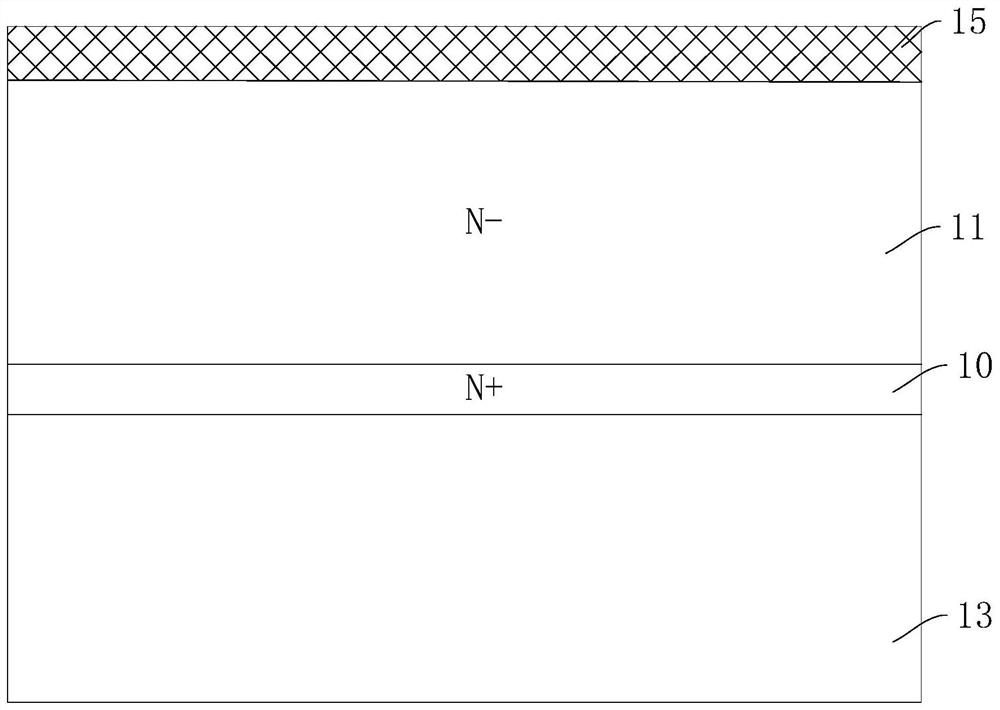

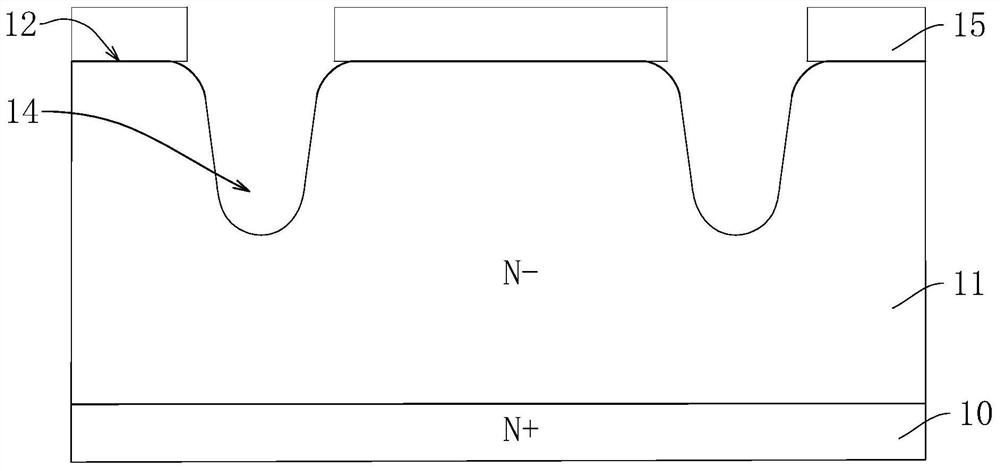

[0080] The technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the accompanying drawings in the embodiments of the present invention. Apparently, the described embodiments are only part of the embodiments for understanding the inventive concepts of the present invention, and cannot represent All the embodiments are not explained as the only embodiment. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art on the premise of understanding the inventive concepts of the present invention fall within the protection scope of the present invention.

[0081] It should be noted that if there is a directional indication (such as up, down, left, right, front, back...) in the embodiment of the present invention, the directional indication is only used to explain the relationship between the components in a certain posture. If the specific postu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com