Semiconductor integrated circuit device

A technology of integrated circuits and semiconductors, applied in the manufacture of semiconductor devices, circuits, and semiconductor/solid-state devices, etc., can solve problems such as increased power consumption, and achieve the effect of improving yield and suppressing manufacturing and performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

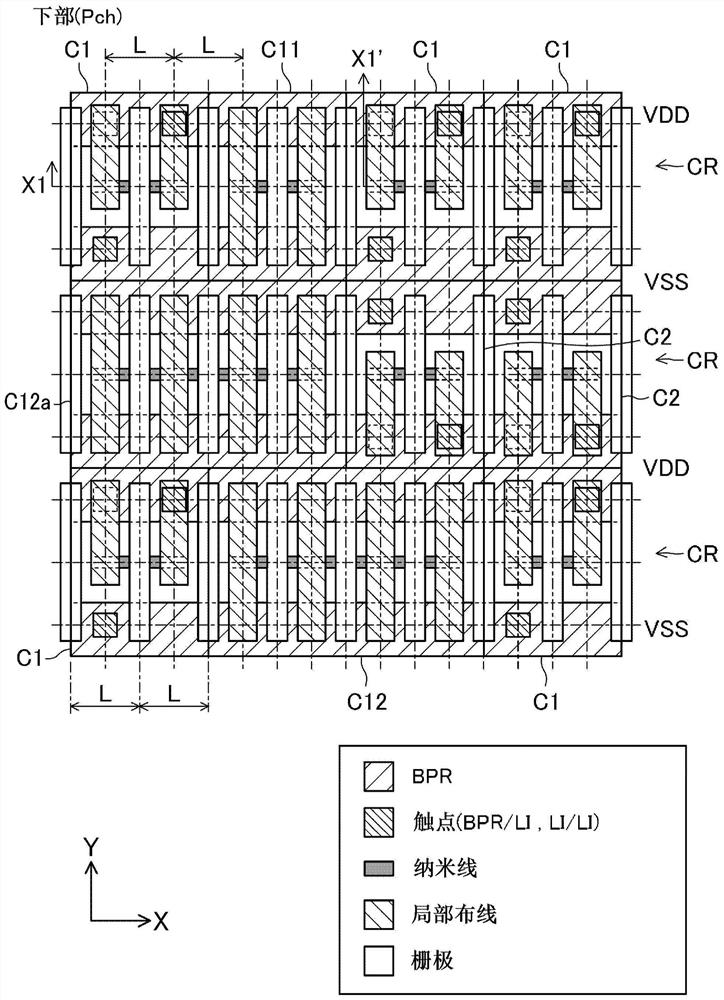

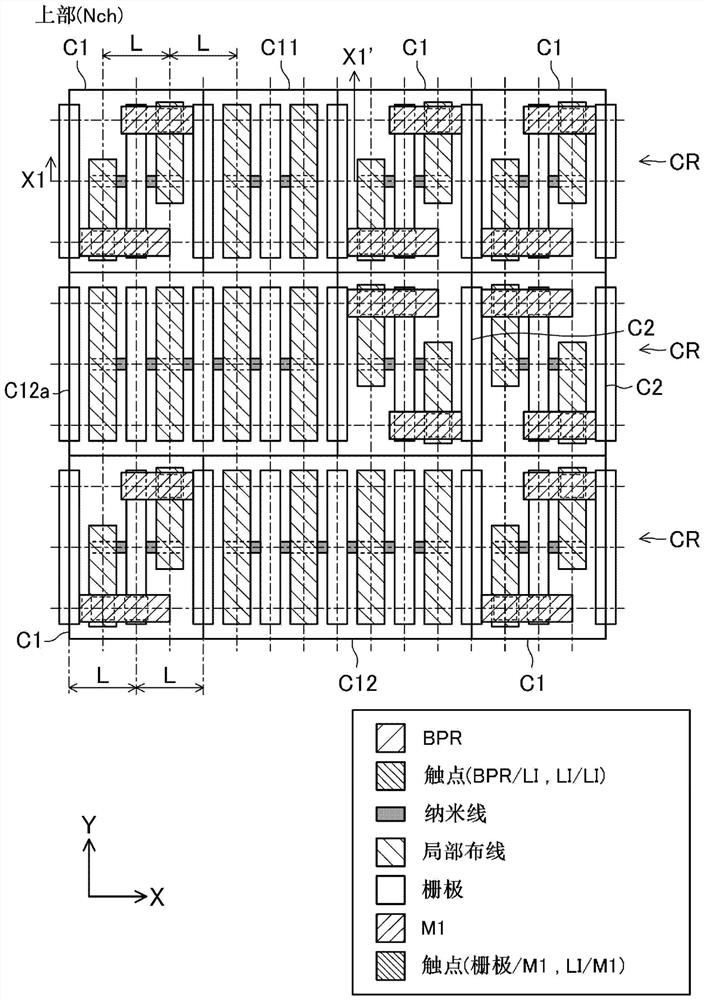

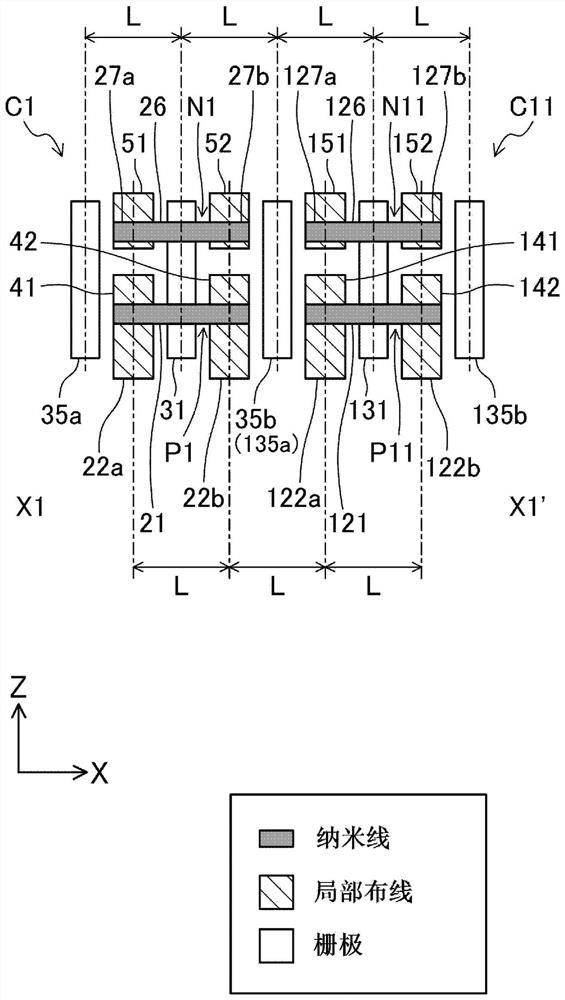

[0052] figure 1 is an example of the layout of the lower part of the circuit block using the standard cell according to the first embodiment, figure 2 is an example of the layout of the upper part of the circuit block using the standard cell according to the first embodiment, image 3 is along figure 1 and figure 2 The section cut by the line X1-X1'. figure 1 and figure 2 is a top view of the circuit block. in particular, figure 1 The lower part is shown, that is, the part including the three-dimensional structure transistor (here, a P-type nanowire FET) formed on the side close to the substrate, figure 2 The upper part is shown, that is, the part including the three-dimensional structure transistor (here, N-type nanowire FET) formed on the side away from the substrate.

[0053] It should be noted that, in the following description, in figure 1 In the top view, the horizontal direction of the drawing is defined as the X direction (corresponding to the first directi...

no. 2 approach

[0134] Figure 12 is a diagram showing the layout structure of the filling cell according to the second embodiment, Figure 12 (a) shows the lower part of the unit, Figure 12 (b) shows the upper part of the unit. The filling cell C21 has no P-type or N-type dummy transistors.

[0135] Such as Figure 12 As shown in (a), power supply wirings 211 and 212 extending in the X direction are respectively provided at both ends of the filling cell C21 in the Y direction. Both the power supply wirings 211 and 212 are buried power supply wirings (BPR) formed in the buried wiring layer. The power supply wiring 211 is supplied with the same power supply voltage VDD as that of the power supply wiring 11 . The power supply wiring 212 supplies the same power supply voltage VSS as that of the power supply wiring 12 .

[0136] In the filling cell C21 , a dummy gate wiring 231 extending in the Y direction substantially at the center in the X direction and extending in the Z direction from...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com