High-resolution in-situ fluid turbulence heating chip of transmission electron microscope

A technology of transmission electron microscope and heating chip, which is used in material analysis using radiation, scanning probe technology, instruments, etc. It can solve the problems of lack of nanofluids, unclear heat conduction mechanism of nanofluids, and large differences in macroscopic motion behavior.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0084] The invention provides a method for preparing a high-resolution in-situ fluid turbulence heating chip under a transmission electron microscope. The preparation method includes the following steps,

[0085] Upper substrate production:

[0086] S101. Prepare Si(100) wafer A with silicon nitride or silicon oxide insulating layers on both sides, the thickness of silicon nitride or silicon oxide is 20nm-200nm;

[0087] S102. Using a photolithography process, transfer the upper center window and the injection port pattern from the photolithography mask to the back of the wafer A, and then develop in a positive photoresist developer to obtain a wafer A-1;

[0088] Preferably, the photolithography process is exposed under the hard contact mode of the ultraviolet lithography machine; the developing time is 50s;

[0089] More preferably, the exposure time is 15s;

[0090] S103. Utilize the reactive ion etching process to etch the upper central window and sample injection port o...

Embodiment 2

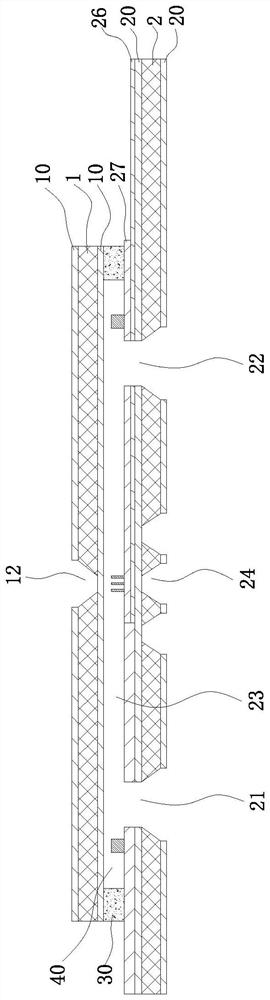

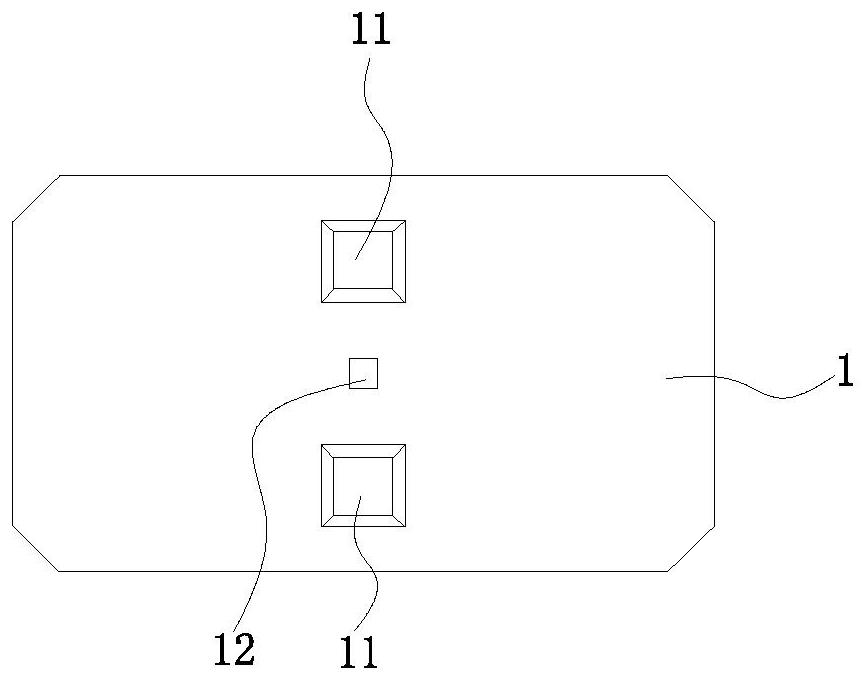

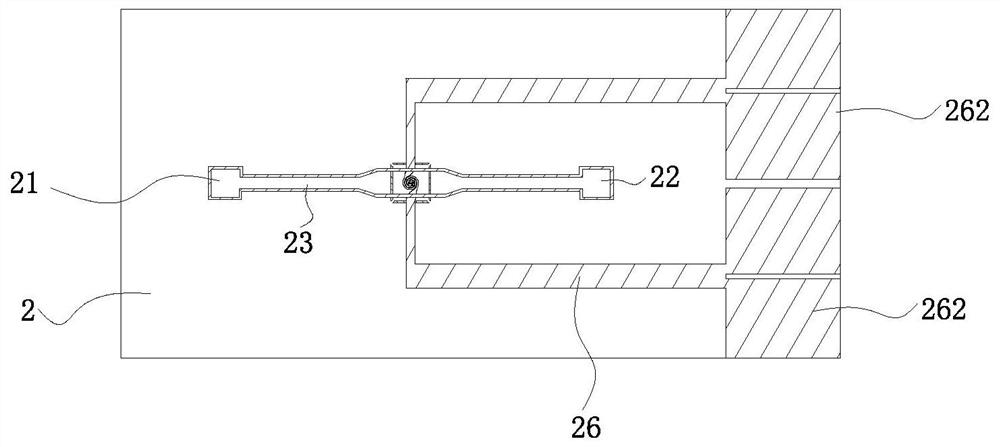

[0136] Such as Figure 1-Figure 4 As shown, the present invention provides a transmission electron microscope high-resolution in-situ fluid turbulence heating chip, the in-situ fluid turbulence heating chip includes an upper substrate 1 and a lower substrate 2, and the upper substrate 1 and the lower substrate 2 The two opposite sides are respectively defined as the front and the back; wherein, the upper substrate 1 has a first insulating layer 10 on the front and the back, and the lower substrate 2 has a second insulating layer 20 on the front and the back. In this embodiment, the materials of the upper substrate 1 and the lower substrate 2 are both silicon substrates, and the first and second insulating layers are silicon nitride or silicon oxide insulating layers.

[0137] The front side of the upper substrate 1 is bonded and fixed on the front side of the lower substrate 2 through an annular metal bonding layer 30, and an ultra-thin cavity 40 is formed by self-sealing. as...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com